简介:在数字通信中,OFDM技术广泛用于传输高速数据流,而FFT作为其核心计算部分负责频域和时域的转换。本资源主要介绍使用Verilog HDL实现的256点FFT算法,适用于OFDM系统的硬件描述。FFT算法优化了DFT的计算量,而Verilog HDL用于设计FFT的硬件电路,以实现高效、低延迟的信号处理。本资源提供了完整的Verilog代码示例或仿真结果,帮助工程师理解和掌握FFT算法在OFDM系统中的应用和优化。

1. OFDM技术与FFT的应用

1.1 OFDM技术概述

正交频分复用(Orthogonal Frequency Division Multiplexing, OFDM)是一种多载波传输技术,它将高速数据流分解为多个并行的低速数据流,在频域内通过相互正交的子载波进行传输。OFDM技术因其对频率选择性衰落和多径效应的强抵抗能力、频谱利用率高、抗干扰性强等特点,被广泛应用于数字电视、无线局域网(WLAN)、4G/5G移动通信等领域。

1.2 FFT在OFDM中的作用

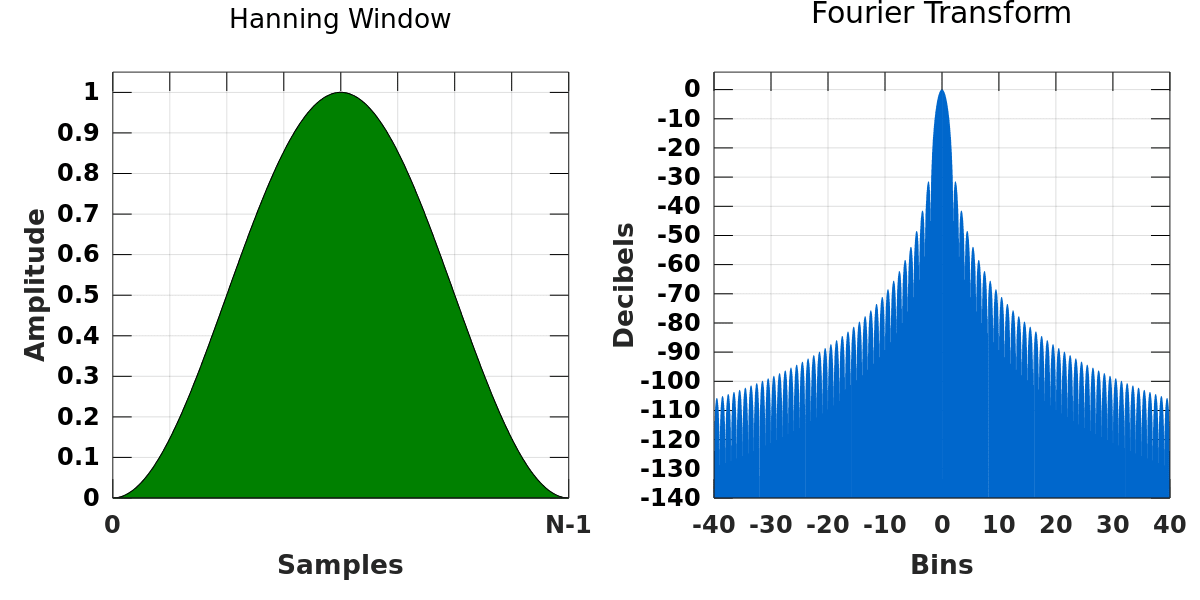

快速傅里叶变换(Fast Fourier Transform, FFT)是实现OFDM的关键技术之一。FFT算法极大地简化了傅里叶变换的计算复杂度,将原本需要O(N^2)复杂度的离散傅里叶变换(DFT)降至O(NlogN),使得实时处理成为可能。在OFDM系统中,FFT用于调制和解调过程,将时域信号转换为频域信号,并将频域信号再转换回时域信号。

1.3 OFDM与FFT的结合

OFDM利用FFT算法实现了频谱资源的高效利用,并提高了系统的抗干扰能力。FFT的引入使得OFDM系统能够在用户端实现高效、快速的信号处理,成为OFDM技术得以广泛商用的基石。在下一章中,我们将深入探讨FFT技术的具体原理及其在数字通信中的关键作用。

2. FFT在数字通信中的作用

在现代数字通信系统中,快速傅里叶变换(FFT)技术扮演着至关重要的角色。它不仅大幅提高了信号处理的效率,而且也是实现许多复杂通信技术的基础。本章我们将深入探讨FFT技术的原理、重要性以及在通信系统中的具体应用。

2.1 FFT技术概述

2.1.1 快速傅里叶变换(FFT)的基本原理

FFT是傅里叶变换的一种高效算法,它通过利用信号样本的对称性和周期性特性来减少计算量。传统的傅里叶变换需要的计算量与样本数量的平方成正比,而FFT则将这一计算量降低至线性对数关系,显著提高了运算效率。

其基本原理是从时域信号变换到频域信号的过程中,将原始信号分割成多个小段,然后对每一段信号进行离散傅里叶变换(DFT)。通过“分治策略”,即递归地将信号分成两部分进行DFT,然后将结果合并,从而实现快速运算。FFT的实现通常采用“蝶形运算”,这一特殊的运算结构极大地简化了算法流程。

2.1.2 FFT与传统傅里叶变换的比较

与传统的傅里叶变换相比,FFT的计算复杂度大幅降低。在处理大规模数据时,FFT算法可以减少大量的计算步骤,从而降低计算资源的消耗和提高处理速度。以N点DFT为例,传统方法需要执行大约N²次复数乘法和加法,而使用FFT算法仅需约Nlog₂N次操作。

为了更直观地理解FFT的优势,我们以以下表格比较FFT与传统傅里叶变换在不同数据点数下的运算次数:

| 数据点数N | 传统DFT运算次数 | FFT运算次数 | |------------|-----------------|-------------| | 1024 | 1,048,576 | 10,240 | | 2048 | 4,194,304 | 24,576 | | 4096 | 16,777,216 | 49,152 |

2.2 FFT在通信系统中的重要性

2.2.1 FFT在信号处理中的应用

在数字通信系统中,FFT主要应用于信号的调制和解调过程,尤其是在正交频分复用(OFDM)系统中。在OFDM系统中,FFT用于将高速数据流分配到多个子载波上,以实现频谱的高效利用,并减少码间干扰。此外,FFT还广泛应用于信号的频谱分析、信道估计、信号去噪等多个方面。

2.2.2 提高信号处理效率的关键技术点

FFT之所以能显著提高信号处理的效率,关键在于其有效利用了信号的对称性和周期性。FFT算法在设计时引入了多种数学优化技巧,如蝶形运算、位反转排序和分治策略。例如,蝶形运算允许在单个步骤中处理多个数据点,大幅度减少了运算次数。位反转排序则是将输入序列以一种特殊方式重新排列,以便在FFT算法中使用。

通过上述技术和方法的应用,FFT成功降低了数字通信系统中的计算复杂度,使得高速数据流能够实时处理,为现代通信技术的发展铺平了道路。

在下一章节中,我们将进一步了解FFT算法的具体实现方法,探讨如何在硬件层面利用Verilog HDL来实现高效、可靠的FFT运算。

3. Verilog HDL硬件描述语言

3.1 Verilog HDL基础

3.1.1 Verilog语言的基本语法和结构

Verilog是一种硬件描述语言(HDL),用于模拟电子系统,特别是在数字电路设计和FPGA(现场可编程门阵列)的开发中广泛应用。它允许设计师使用类似于编程语言的语法描述硬件的行为和结构。

基本语法特点 :

- 模块(Module) :Verilog中最基本的单元是模块,它定义了电路的接口和行为。模块可以包含输入(input)、输出(output)以及双向(inout)端口。

- 数据类型 :Verilog支持多种数据类型,如

wire,reg,integer,real等。wire类型用于连续赋值,而reg类型用于过程赋值。 -

赋值语句 :连续赋值使用

assign关键字,如assign wire_var = expression;。过程赋值使用always块,并在敏感列表中指定触发信号,如always @ (posedge clk)。 -

时序控制 :Verilog提供了用于描述时序逻辑的

always块。这些块可以包含posedge和negedge来描述时钟沿触发的逻辑。 -

参数和宏定义 :使用

parameter关键字可以定义参数,而'define用于宏定义,例如,'define DEBUG。 -

条件语句和循环 :与传统编程语言类似,Verilog支持

if-else,case,for,while等控制结构。

基本结构 :

module module_name (

input wire a,

input wire b,

output reg sum

);

// 模块实现代码

endmodule

3.1.2 设计模块化和代码复用

模块化 是设计大型数字电路系统的关键。通过定义多个小的模块,每个模块负责系统中的一个小部分功能,设计者可以更容易地管理复杂的设计。

代码复用 可以通过参数化模块实现,参数化的模块允许在模块实例化时指定参数,从而可以根据需要复用同一模块的不同实例。

module adder #(

parameter WIDTH = 8

)(

input [WIDTH-1:0] a,

input [WIDTH-1:0] b,

output [WIDTH-1:0] sum

);

assign sum = a + b;

endmodule

在上面的例子中, adder 模块是参数化的,可以根据 WIDTH 参数来定义加法器的位宽。

3.2 Verilog在FPGA开发中的应用

3.2.1 FPGA的工作原理及特点

FPGA是一种可编程的逻辑设备,它由大量可编程的逻辑块、可编程互连资源以及可配置的输入输出单元组成。FPGA可以实现高度并行的处理能力,适合于算法加速、信号处理等应用。

FPGA特点 :

- 可重配置性 :FPGA能够重新编程,以适应不同的应用需求。

- 高性能 :由于并行处理能力,FPGA能够提供高性能的数字信号处理。

- 低延迟 :适合于需要快速响应的实时系统。

- 可扩展性 :通过堆叠多个FPGA可以实现更高的性能。

3.2.2 Verilog与FPGA开发流程

FPGA开发流程一般包括设计描述、综合、布局布线、生成配置文件以及最终的硬件验证。

- 设计描述 :使用Verilog或VHDL等硬件描述语言对电路进行描述。

- 综合 :将HDL代码转换成FPGA可以理解的门级网表。

- 布局布线 :将综合后的网表映射到FPGA的物理资源上。

- 生成配置文件 :通过布局布线后的结果生成可下载到FPGA上的配置文件。

- 硬件验证 :将配置文件下载到FPGA中,进行实际的硬件测试和验证。

在FPGA开发中,Verilog扮演了核心角色,它不仅用于描述硬件设计,还可以在模拟和测试阶段发挥作用,验证设计的正确性。

// 示例:一个简单的2位二进制加法器模块

module adder_2bit (

input [1:0] a,

input [1:0] b,

output [2:0] sum

);

assign sum = a + b;

endmodule

在设计FPGA项目时,往往需要编写大量的Verilog代码,编写时应该遵循良好的编程实践,如模块化设计、代码复用和清晰的命名约定,以提高代码的可读性和可维护性。

4. 256点FFT算法实现

4.1 256点FFT算法原理

4.1.1 256点FFT算法的数学模型

快速傅里叶变换(FFT)是数字信号处理中非常核心的算法之一,尤其在多点离散傅里叶变换(DFT)中,FFT的引入极大地提高了运算的效率。256点FFT算法是一种将时域信号转换为频域信号的数学模型,适用于处理256个样本点的数据序列。

DFT的数学表达式可以表示为:

[X[k] = \sum_{n=0}^{N-1} x[n] \cdot e^{-j \frac{2 \pi}{N} kn}]

对于256点FFT,N=256,这意味着我们将对一个包含256个样本点的序列进行变换。在传统的DFT中,该运算的时间复杂度为O(N^2),而通过FFT算法,复杂度可以降低到O(NlogN)。这一优化是通过递归地将大的DFT问题分解为小的DFT问题,利用频域的对称性和周期性来实现的。

4.1.2 FFT算法的蝶形运算与迭代过程

蝶形运算的核心思想是将一个大的FFT问题分解为一系列小的FFT问题,然后再将这些小问题的结果进行合并。在256点FFT算法中,这种分解主要体现在将DFT矩阵按位逆序分组,然后进行迭代计算。

蝶形运算单元是FFT算法中的基本运算单元,每个单元对应于DFT公式中的一个指数项。迭代过程可以分为多个阶段,每个阶段中,输入序列被分成多个组,每组内进行蝶形运算。整个迭代过程可以通过递归或迭代的方式实现。

4.2 256点FFT的Verilog实现

4.2.1 Verilog代码结构设计

在Verilog中实现256点FFT算法,首先需要设计合适的模块结构。一个典型的FFT模块结构可能包括输入输出接口模块、数据排序模块(位逆序)、蝶形运算模块、以及控制逻辑模块。

以下是Verilog代码的简化示例结构:

module fft_256(

input clk,

input rst,

input [15:0] data_in[255:0], // 256个16位输入数据

output reg [15:0] data_out[255:0], // 256个16位输出数据

input start,

output reg done

);

// 代码实现细节...

endmodule

4.2.2 关键代码段分析与实现

在FFT算法的Verilog实现中,蝶形运算单元的代码是核心部分。以下是一个蝶形运算单元的示例代码:

always @(posedge clk) begin

if (!rst) begin

data_out <= 0;

end else begin

// 蝶形运算实现

// 假设data_in是输入数据,data_out是输出数据

// twiddle_factor是旋转因子

for (int i = 0; i < 128; i++) begin

complex temp1 = data_in[i];

complex temp2 = data_in[i + 128];

complex twiddle;

// 计算旋转因子

// ...

// 蝶形运算核心公式

temp1.re = temp1.re + twiddle.re * temp2.re - twiddle.im * temp2.im;

temp1.im = temp1.im + twiddle.re * temp2.im + twiddle.im * temp2.re;

temp2.re = temp1.re - twiddle.re * temp2.re + twiddle.im * temp2.im;

temp2.im = temp1.im - twiddle.re * temp2.im - twiddle.im * temp2.re;

data_out[i] = temp1;

data_out[i + 128] = temp2;

end

done <= 1;

end

end

在这个代码段中,我们使用了复数运算来实现蝶形运算。输入的复数数据 data_in 和旋转因子 twiddle_factor 被用于计算输出数据 data_out 。复数运算需要考虑到实部和虚部的正确操作,同时在实现中还应考虑数据宽度和定点表示。

以上代码展示了如何实现FFT算法中的蝶形运算,完整的FFT实现还需要包括数据排序、旋转因子的生成、以及控制逻辑等多个部分。在实际的FPGA设计中,由于资源和时序的限制,通常需要对代码进一步优化,以满足硬件实现的要求。

5. FFT算法的计算复杂度优化

5.1 FFT算法复杂度分析

5.1.1 时间复杂度和空间复杂度

在数字信号处理领域,快速傅里叶变换(FFT)算法的出现极大地方便了工程师对信号的分析和处理。FFT算法之所以受到青睐,很大程度上是因为其相比于传统的离散傅里叶变换(DFT),在计算复杂度方面实现了质的飞跃。计算复杂度主要从时间和空间两个维度来衡量。

时间复杂度 :FFT的时间复杂度通常指的是完成一次N点FFT变换所需要的乘法和加法的次数。以最常见的基-2 FFT算法为例,其时间复杂度为O(NlogN),对比于DFT的O(N^2),FFT实现了显著的提速。在工程实践中,这直接关系到实时处理的能力,尤其在高速信号处理的场合,这个优势尤为关键。

空间复杂度 :虽然FFT的时间复杂度优势显著,但也不应忽视其空间复杂度。在某些FFT实现中,为了避免大量的内存分配和释放,可能会引入额外的内存开销。例如,一个256点的FFT算法,可能需要预先分配一个大小为512的数组来存储中间结果,即使最终只需要256个结果。这样的空间开销在硬件实现时尤其重要,因为内存的使用会直接影响硬件的规模和成本。

5.1.2 算法优化的基本方法

为了进一步优化FFT算法,研究者们提出了多种方法。一些普遍使用的优化方法包括:

- 缓存优化 :通过合理安排数据的存储和访问顺序,使得数据可以尽可能地利用缓存,减少内存访问的次数,尤其是在CPU中。

- 分治策略 :将大问题分解为若干小问题,独立解决后再合并结果,例如Cooley-Tukey FFT算法就是采用的这种策略。

- 并行计算 :利用多核处理器或者硬件并行处理能力来同时计算多个数据点,大幅减少总的运算时间。

- 量化和剪枝 :在保证一定精度的前提下,减少所需的位宽和数值大小,以此降低乘法器和加法器的数量。

- 循环展开 :减少循环的开销,特别是在循环体较轻的情况下。

接下来,我们将具体介绍在实践中的FFT优化技术。

5.2 实践中的优化技术

5.2.1 位反转与内存访问优化

位反转(bit-reversal)是一种特殊的索引排序方式,用于FFT算法中,以保证数据在内存中的布局符合FFT计算的要求。在软件实现中,位反转可以通过预先计算一个位反转索引表来加速,在硬件实现中,则通常通过位反转逻辑网络来实现。

位反转的优化 :为了减少位反转过程的时间复杂度,可以设计特定的硬件逻辑或者优化的位反转算法,比如通过预先计算位反转的规律,使用查表法直接得到结果。

内存访问优化 :在FFT计算中,需要频繁地从内存中读取和写入数据。为了提高效率,一方面需要尽可能地减少访问次数,另一方面需要提高每次内存访问的利用率。例如,可以将数据以特定的方式存储,这样连续的内存访问能够一起处理更多的数据。此外,对于并行计算场景,利用多通道内存访问可以显著提升FFT的吞吐量。

5.2.2 循环展开与蝶形运算优化

循环展开(Loop unrolling)是一种常见的编译器优化技术和手动代码优化技术,目的是减少循环的开销。在FFT算法中,循环展开可以应用到蝶形运算的各个阶段,减少循环迭代次数从而加速计算过程。

蝶形运算的优化 :蝶形运算(Butterfly operation)是FFT算法的核心部分,涉及到复数的加法和乘法。通过优化蝶形运算,可以显著提高FFT算法的效率。蝶形运算的优化通常包括:

- 共轭对称性质的应用 :在FFT中,利用输入数据的共轭对称性质可以减少一半的运算量。

- 数值精度的优化 :在不影响性能的前提下,通过简化或省略某些计算步骤来降低运算精度的需求,从而减少资源消耗。

- 硬件并行化 :在FPGA或ASIC中,可以实现蝶形运算的并行处理,通过流水线技术和并行处理单元来提升性能。

通过上述优化手段,FFT算法的计算复杂度可以得到大幅优化,这对于需要实时处理高数据吞吐量场景下的数字信号处理系统来说意义重大。

// 示例:256点FFT中蝶形运算单元的Verilog代码片段

// 参数说明:Wn为旋转因子,X和Y为输入的复数序列,W为输出的复数序列

// 注意:以下代码仅为示例,未包含完整的设计细节和优化策略

module butterfly_unit(

input complex Wn, // 输入旋转因子

input complex X, // 输入序列X

input complex Y, // 输入序列Y

output complex W // 输出序列W

);

// 蝶形运算的复数加法和乘法

assign W = X + Wn * Y;

endmodule

在下一节中,我们将继续探讨FFT核心运算中的蝶形运算,以及如何在硬件层面进行高效实现。

6. FFT核心运算-蝶形运算

6.1 蝶形运算的基础知识

6.1.1 蝶形运算的定义和性质

蝶形运算是快速傅里叶变换(FFT)算法中的一种基本运算,因其形状类似蝴蝶而得名。在FFT中,蝶形运算用于执行复数乘法和加减操作,它是对信号进行频域分解的关键步骤。蝶形运算通常在FFT算法的各级迭代中执行,每一级迭代中,数据被分为不同的组别,组内的数据进行蝶形运算,从而实现在频域中的分割。

蝶形运算的特点是高度规则和对称,这使得其硬件实现具有很高的优化潜力。蝶形运算单元在实现上倾向于使用并行处理和流水线技术,以提高处理速度和效率。

6.1.2 蝶形运算在FFT中的角色

在FFT算法中,蝶形运算承担着分解和重组信号频谱的功能。每一次蝶形运算相当于一次频谱分析,将输入的复数数据流分成两部分,分别进行加法和减法运算。通过这种方式,FFT能够在对数级的时间复杂度内完成整个频域的变换。

由于蝶形运算的这一特性,它在提高FFT算法效率方面起着至关重要的作用。蝶形运算的优化直接关系到整个FFT算法的性能表现。

6.2 蝶形运算的硬件实现

6.2.1 蝶形运算单元的设计

在硬件层面,蝶形运算单元的设计需要考虑到处理速度、资源消耗和可扩展性。通常,蝶形运算单元采用定点数或浮点数来表示复数,而这些复数的实部和虚部会参与到运算中。

设计时需要考虑的因素包括: - 输入输出接口设计:确保数据流可以高效地送入和移出蝶形运算单元。 - 运算器的数量和类型:根据FFT算法的具体需求,选择适当数量和类型的运算器(如加法器、乘法器)。 - 控制逻辑设计:有效地控制运算流程,包括位反转、旋转因子的引入和蝶形运算的执行。

6.2.2 并行处理与流水线技术

为了提升FFT算法的性能,蝶形运算单元通常会集成并行处理和流水线技术。并行处理允许同时对多组数据执行蝶形运算,而流水线技术则允许在单个蝶形运算单元内实现多个运算步骤的重叠执行。

在设计时,要根据硬件资源和性能要求合理分配流水线的级数。过多的流水线级数会导致流水线的开销增大,而流水线级数太少则无法充分利用硬件资源。适当的优化需要在计算性能、资源消耗和设计复杂度之间取得平衡。

为了展示蝶形运算在FFT中的实际作用,可以考虑一个简单的2点FFT的例子,并据此设计对应的蝶形运算硬件单元。通过分析其输入输出关系,可以进一步理解如何在硬件上实现这种运算以提升整个FFT算法的效率。

简介:在数字通信中,OFDM技术广泛用于传输高速数据流,而FFT作为其核心计算部分负责频域和时域的转换。本资源主要介绍使用Verilog HDL实现的256点FFT算法,适用于OFDM系统的硬件描述。FFT算法优化了DFT的计算量,而Verilog HDL用于设计FFT的硬件电路,以实现高效、低延迟的信号处理。本资源提供了完整的Verilog代码示例或仿真结果,帮助工程师理解和掌握FFT算法在OFDM系统中的应用和优化。

4675

4675

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?