OPENNING

IC风暴-记录点滴

点击上方 蓝字 关注我们

PL端定制外设

引言

项目需要实现数据从XCKU115传输给XC7Z030之后,位于XC7Z030的PL端(可编程逻辑端)的数据寄存器,需要PS端(处理系统,即双核ARM)通过AXI-Lite总线实现读取PL端的寄存器内容。

该部分的开发思路基于板载XC7Z030与XCKU115之间通过若干组GPIO进行了互联,项目需要传输的数据量并不大,单次数据传输量为80bit的幅度值、13bit的距离单元结果。80+13=93bit,为方便按96bit处理。板载资源ZC702与KU115之间50路GPIO互联。

生成AXI4外设操作流程

数据通过GPIO连线进入XC7Z030后,位于PL端的特殊结果寄存器中,实现硬件定制外设之后PS端就可以读取特殊寄存器中的结果了。硬件定制AXI外设流程如下:

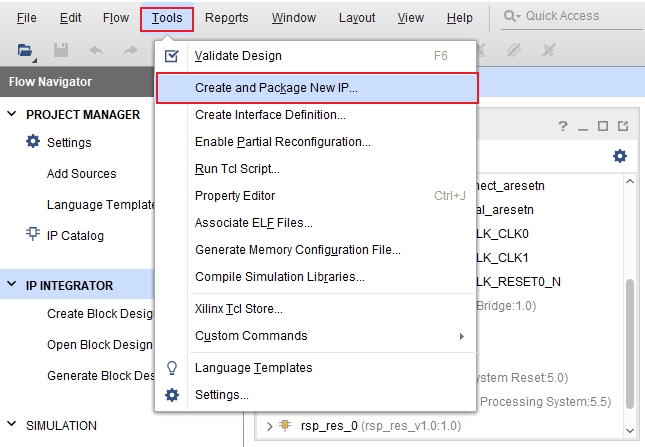

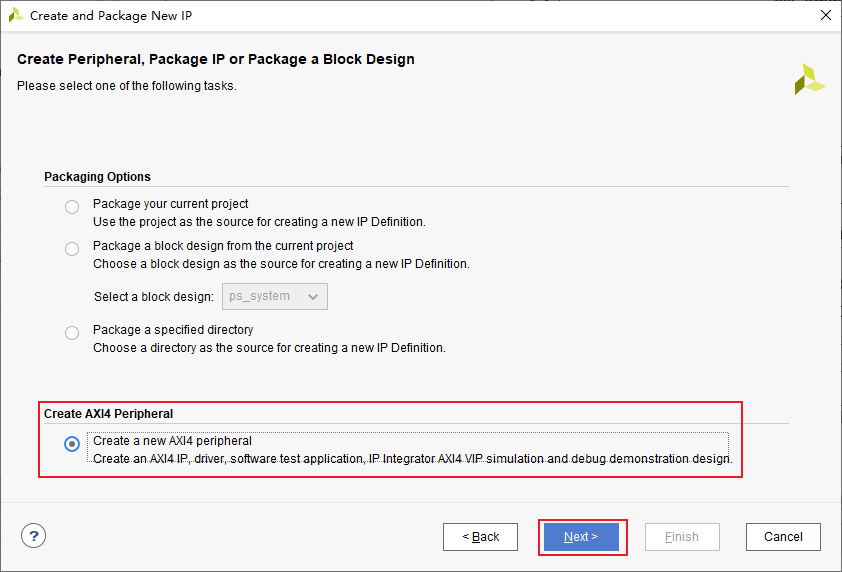

点击Tools选择Create and Package New IP...

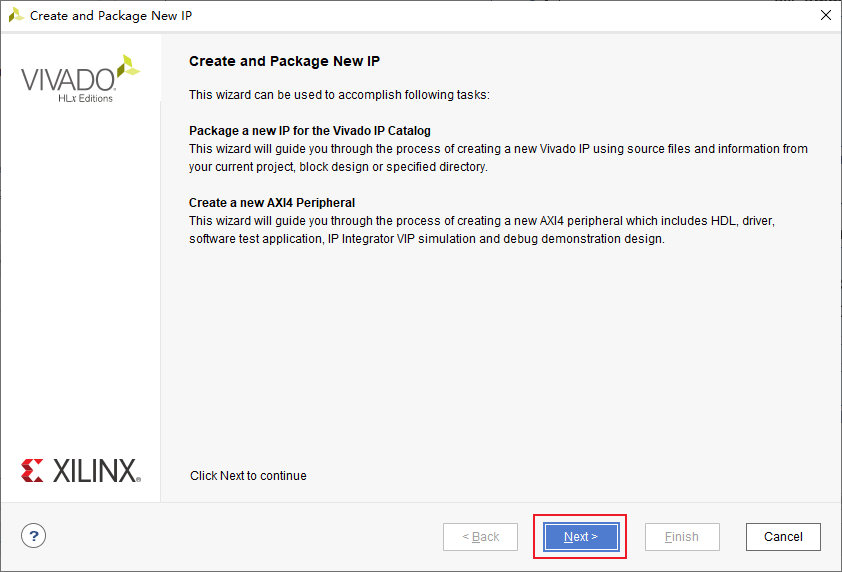

然后点击Next

勾选Create AXI4 Peripheral并点击下一步

输入要创建的IP名称,此处比如命名为rsp_test并点击下一步

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

360

360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?