如何在Vitis HLS中使用C语言代码创建AXI4-Lite接口

在本教程中,我们将来聊一聊有关如何在 Vitis HLS 中使用 AXI4-Lite 接口创建定制 IP 的基础知识。n-ZOe]3

注:在 Vivado HLS 中使用 AXI 创建 IP 的过程与使用 Vitis HLS 的过程不同。如果您想要在 Vivado HLS 中创建 AXI IP,请参阅UG902。2XoFmV),F

2"0q9 Jg

https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/c_ug902-vivado-high-level-synthesis.pdf;rwjqUDBz

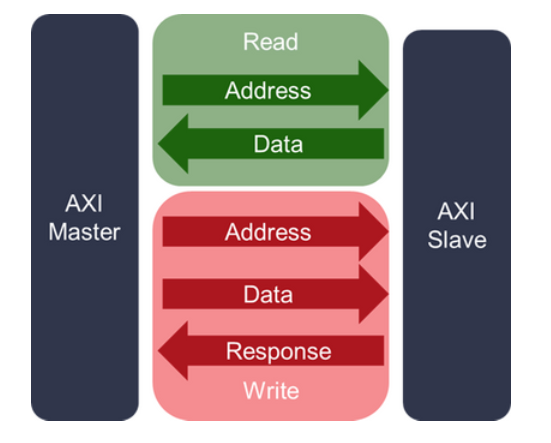

AXI4-Lite 属于基本 AXI 通信协议。它常用于简单的低吞吐量存储器映射通信(例如,往来于控制寄存器和状态寄存器的通信)。0_nY70B

如上图所示,AXI4-Lite 接口可设置为只读(仅包含 2 条读取通道)或只写(仅包含 3 条写入通道)。n1

如上图所示,AXI4-Lite 接口可设置为只读(仅包含 2 条读取通道)或只写(仅包含 3 条写入通道)。n1

k2

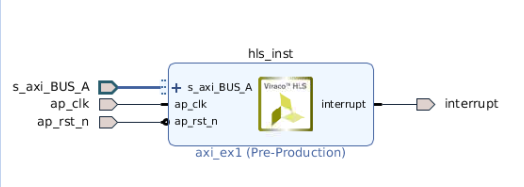

在本教程中,我们将创建以下 IP,并使用 s_axi_BUS_A 作为我们的 AXI4-Lite 接口:/mS|Byx

本教程结束时,您将能够~V#MI@]V~

本教程结束时,您将能够~V#MI@]V~

了解在 Vitis HLS 中创建 AXI4-Lite 接口的相关基础知识。z}Y23W&sX

了解 Vitis HLS 中的编译指示相关信息,此类编译指示用于定义所使用的 AXI 接口。9Q\CJ9

打开 AXI4-Lite 设计示例A'A5.\UN

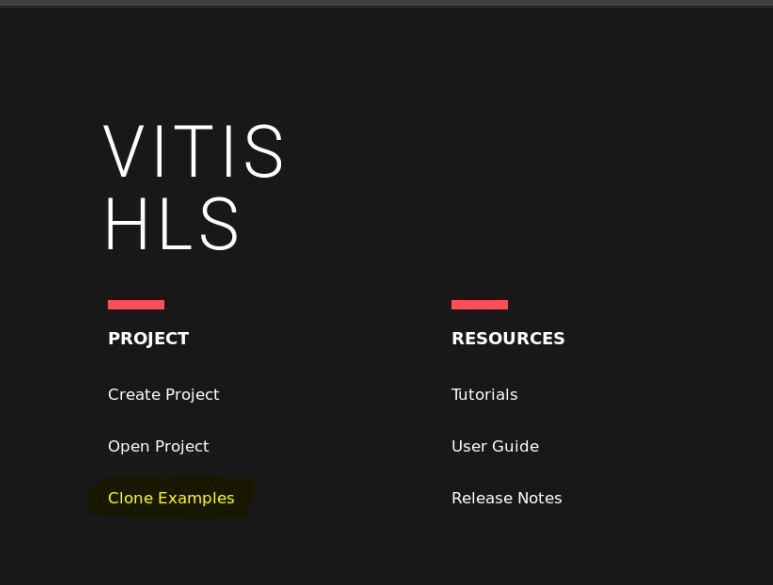

在 Vitis HLS 中提供了 AXI4-Lite 的设计示例。要打开 AXI4-Lite 的设计示例,请遵循以下步骤进行操作:73/DOF

1. 打开 Vitis HLS GUI。在首页屏幕中,选择“克隆示例 (Clone Examples)”选项以便从 GitHub 复制 Vitis HLS 设计示例:Ug:3)q[O

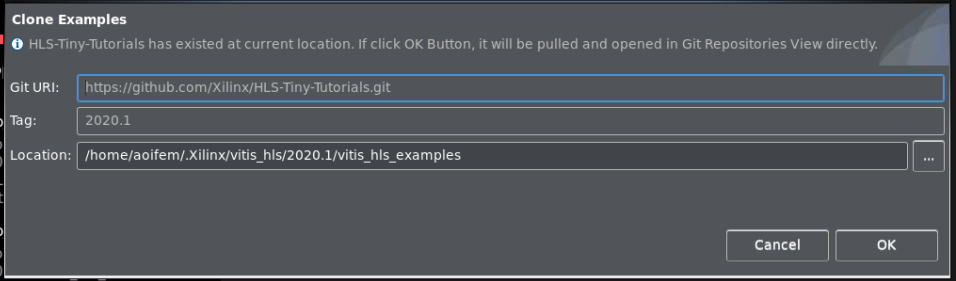

2. 在弹出选项卡中,选择示例的保存位置,然后单击“确定 (OK)”:jhRg47A

2. 在弹出选项卡中,选择示例的保存位置,然后单击“确定 (OK)”:jhRg47A

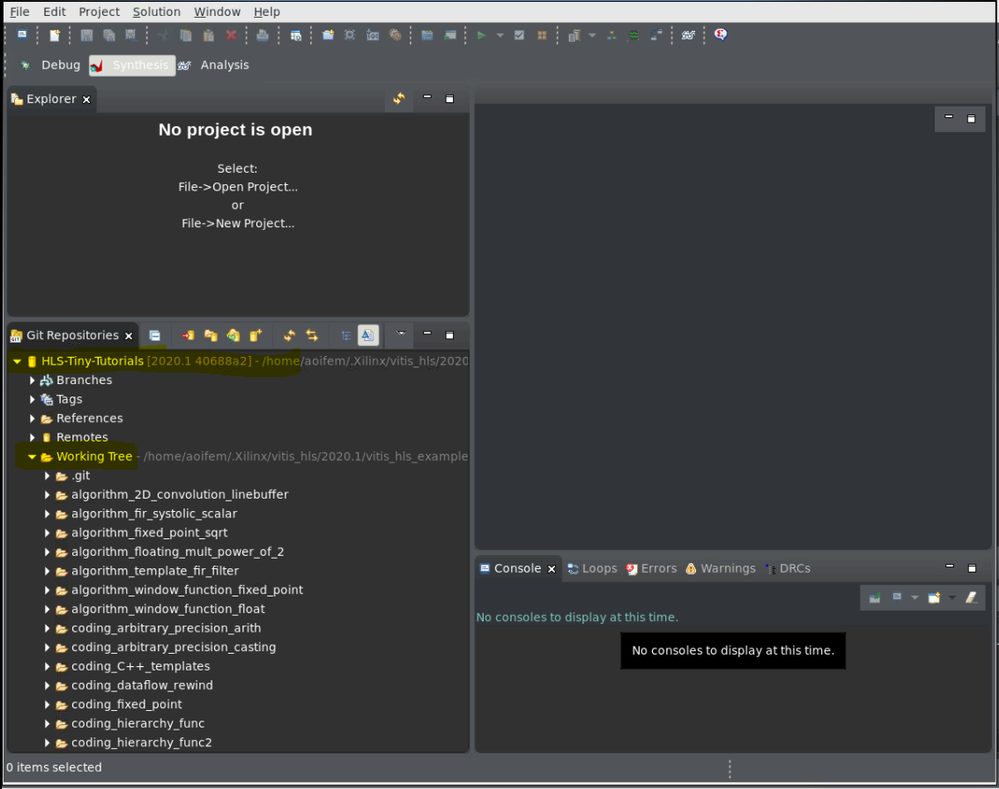

3. 在下一个屏幕中,设计示例将显示在左下角。选中“HLS 微教程 (HLS Tiny Tutorials)”和“工作树结构 (Working Tree)”旁的箭头即可查看所有可用示例。%@C(H%obWd

3. 在下一个屏幕中,设计示例将显示在左下角。选中“HLS 微教程 (HLS Tiny Tutorials)”和“工作树结构 (Working Tree)”旁的箭头即可查看所有可用示例。%@C(H%obWd

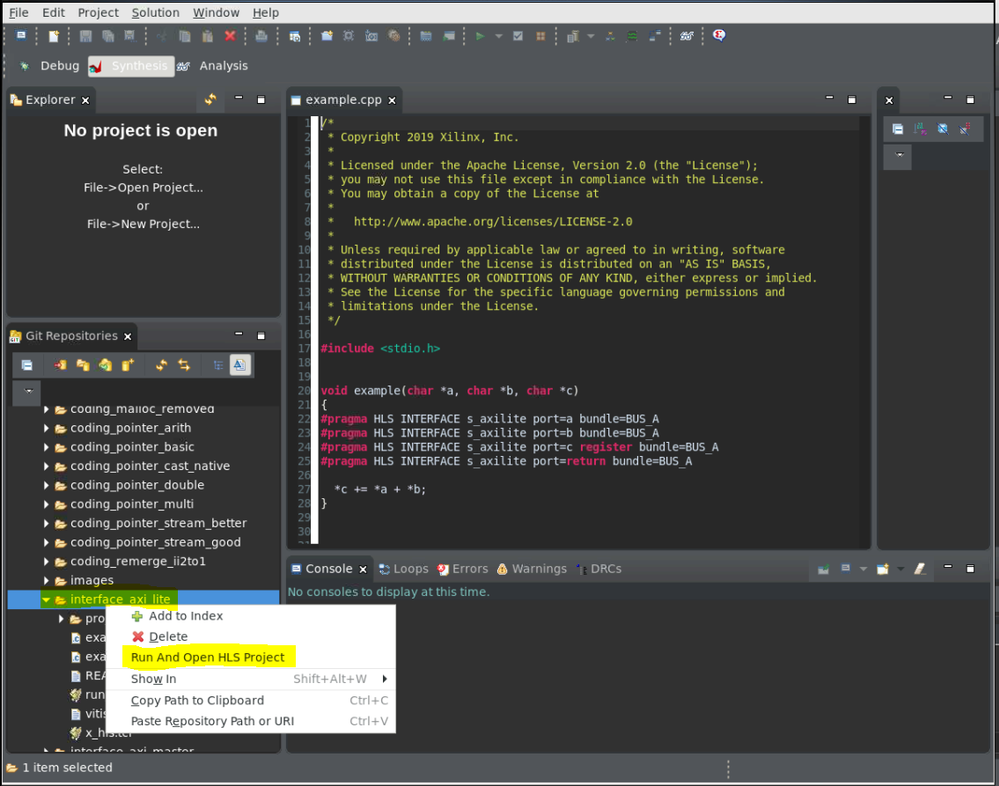

4. 向下滚动,找到 interface_axi_lite 示例。右键单击文件夹名称,然后选中“运行并打开 HLS 工程 (Run and Open HLS Project)”选项。"&$ [@c

4. 向下滚动,找到 interface_axi_lite 示例。右键单击文件夹名称,然后选中“运行并打开 HLS 工程 (Run and Open HLS Project)”选项。"&$ [@c

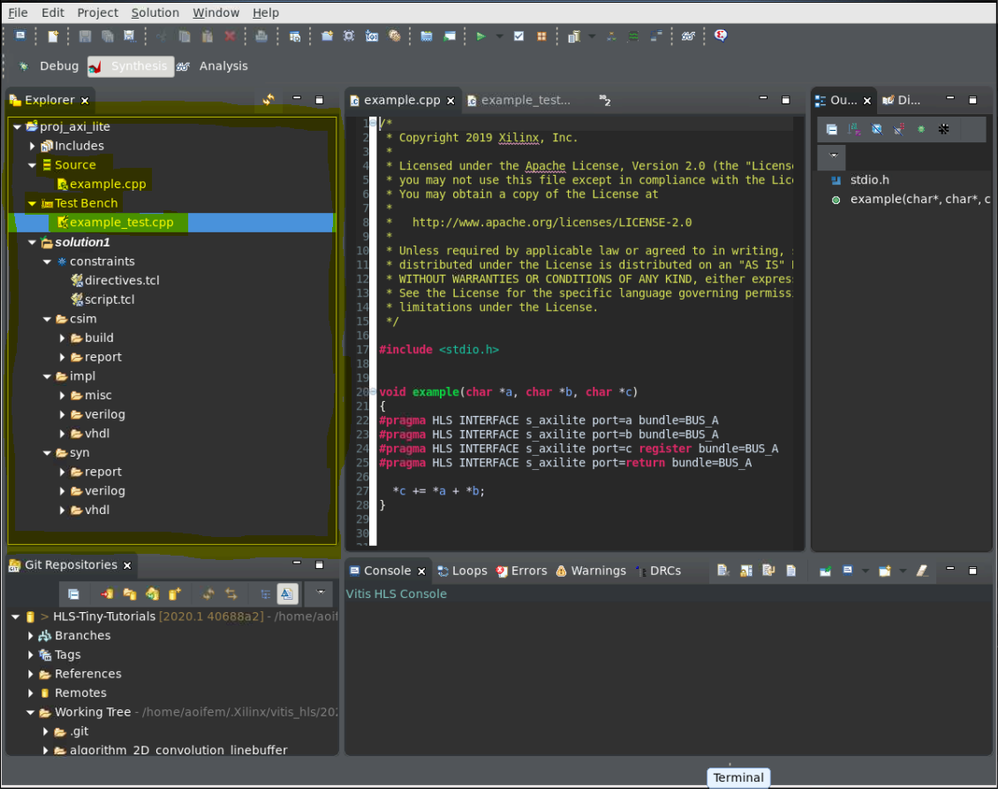

5. 完成此操作后,将在左侧选项卡中打开此工程。双击 example.cpp 和 example_test.cpp 以查看源代码和测试激励文件。qW~Z#Si

5. 完成此操作后,将在左侧选项卡中打开此工程。双击 example.cpp 和 example_test.cpp 以查看源代码和测试激励文件。qW~Z#Si

源代码详解0%x"Va~"z

此示例包含 2 个主要文件:^a>3U l{

Example.cpp - 此代码将综合到 RTL 中以创建“简介”中所示的 IP。此 IP 将与 Vivado Design Suite 中的其它 IP 相结合,并最终被放置到您的硬件上。6yn34'yw

Example_test.cpp - 此测试激励文件将用于确保 example.cpp 按期望方式运行。Example.cpp 算法将通过如下方式进行检查:将该算法的输出与测试激励文件中执行的“期望数据 (golden data)”计算结果进行比较。只要黄金数据与 example.cpp 的返回结果相匹配,HLS 中的测试激励文件就会返回 0。T"h@-UcTl

选中左侧列中“源代码 (Source)”下的 example.cpp 即可打开源代码。接下来我们来详细看下代码:%E<.>

选中左侧列中“源代码 (Source)”下的 example.cpp 即可打开源代码。接下来我们来详细看下代码:%E<.>

函数实参o)\\(^ld

void example(char *a, char *b, char *c)[p& n]T

进入库之后首先可看到的是 example(); 函数。只要您熟悉基于 C 语言的设计,就不难发现,通过形参(如上述示例中的 char *a、char *b 和 char*c)即可瞬间执行所有输入和输出操作。7hV9nuW

-4 *94<

对于进出 IP 的每一条数据,都应将其指定为主源文件中的一个独立函数实参。稍后,该函数实参将被综合成硬件 (RTL) 中的一个“端口”。K)ZW1d;

注:端口实际上可通过 3 种不同方法来创建,但本教程将主要讲解采用函数实参的方法。tW^oa

端口衍生自:=1|^)4M,x

指定的任意函数级协议。X283 . ?

函数实参。Q:L^DZkGV

全局变量(供顶层函数访问,在其作用域范围外定义)。f$7Xh~

注:由于 AXI4-Lite 接口中的变量为函数实参,因此在 C 语言代码中无法为其指定默认值。因此,无法为 AXI4-Lite 接口中的任何寄存器指定默认值。这些寄存器可通过 config_rtl 命令进行复位来实现,但不能为其指定任何其它默认值。(请参阅控制复位行为以了解详细信息)。Np2I*l6W

https://china.xilinx.com/html_docs/xilinx2020_1/vitis_doc/programmingvitishls.html2SjH7

'

接口编译指示vJ

+sdG

接下来,我们来看看编译指示接口。egXHp

首先逐一了解下其中每个组件:^l,(~03_

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A_cRCG1CJ

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_AEWb'#+BP

#pragma HLS INTERFACE s_axilite port=c register bundle=BUS_ALqYP0%7

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A-RLY.@'d-M

我们需要把 IP 的输入/输出定义为 s_axilite,这样才能使用 AXI4-Lite 协议。如果我们的代码中不包含此行,那么数据输入/输出将综合到基本连线中,并且将不含关联的握手信号。在此情况下,输入将保持稳定状态直至执行读取输入操作为止,一旦未谨慎执行此操作,就可能导致错误。|2Krxi3*

接口编译指示格式如下:v|K,

#pragma HLS interface port= (register) bundle=3p+V~n.+

其中:[TW?sW^0

:用于指定函数实参的接口协议模式。在此例中,我们选择的是 s_axilite。o[

Je

port=:用于指定 INTERFACE 编译指示所应用到的函数实参名称。xM+_rU

M|h

(register):这是可选关键字,用于寄存(即存储)信号和所有关联的协议信号。它会导致信号保持直至至少完成函数执行的最后一个周期为止。)7aUDsu>4

bundle=:此关键字支持您将端口信号手动组合到单一数据总线内。如果函数返回指定为 AXI4-Lite 接口(即代码示例中的第 25 行),那么所有数据端口都将被自动捆绑到单一总线中。如果未在此处明确提供捆绑名称,那么 Vitis HLS 将使用默认捆绑名称control。当使用其它器件(例如,CPU)来配置和控制块的启动和停止操作时,这是常见的做法。k^H&IS!

s_axilite port=return:用于设置类型为 s_axilite 的函数实参,端口名称“return”将在 IP 块中创建中断信号。您可通过 AXI4-Lite 接口和 C 语言驱动程序文件来完成中断编程。如需了解更多信息,请参阅 此处JJQS7,vG

https://china.xilinx.com/html_docs/xilinx2020_1/vitis_doc/programmingvitishls.html#auo1539734222936Mzg zOM

注:如果任意顶层函数实参指定为 AXI4-Lite 接口,则函数返回也必须指定为 AXI4-Lite 接口。w$)NW57[|

注 2:默认情况下,HLS 会为分组到同一个 AXI4-Lite 接口的每个端口分配地址。Vitis HLS 在C 驱动程序文件 (如下链接)中提供了分配的地址。要显式定义地址,可使用 offset 选项。在 AXI4-Lite 接口中,Vitis HLS 保留地址 0x0000 到 0x000C,用于块级 I/O 协议信号和中断控制。2\4ammwT

https://china.xilinx.com/html_docs/xilinx2020_1/vitis_doc/programmingvitishls.html#auo1539734222936e7_.Xr~[

函数主体7:M`k #oDP

*c += *a + *b;-$VP#%

在该函数中,可以精确定义希望此 IP 执行的操作,此 IP 将导入 2 个值(a 和 b)并将结果 (c) 存储在寄存器中。为测试功能,测试激励文件将为 a 和 b 提供 example() 函数,并将其与自己计算 a+b 所得的值进行比较。如果结果相匹配,那么测试激励文件应始终返回 0,并且 c 仿真即可通过。3P=I)q

3785

3785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?