今天小编给大家分享几个跟时钟树综合,clock tree相关的典型问题。

数字SoC芯片复杂时钟结构设计时钟树综合典型案例(最复杂的时钟案例也不过如此!)

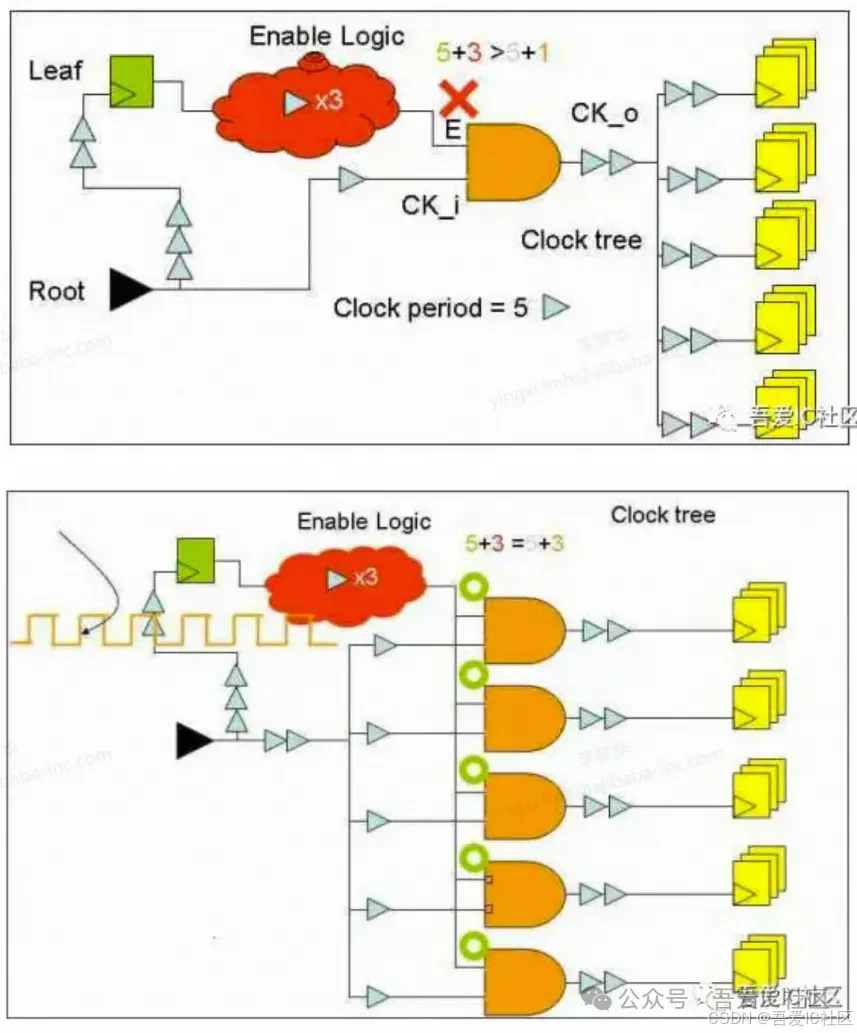

Q1:星主好,下面的图是通过duplicate icg来解setup违例的示意图。我没看懂这个 duplicate操作在cts阶段是怎么实现的,用什么命令实现的吗?为什么复制成5个icg之后,capture clk上的buffer会变多,然后就timing met了?

Innovus PR实现阶段可以通过下面的命令来复制或合并clock gating cell。

set_ccopt_property ccopt_merge_clock_gates trueset_ccopt_property cts_merge_clock_gates trueset_ccopt_property ccopt_merge_clock_logic trueset_ccopt_property cts_merge_clock_logic trueset_ccopt_property merge_clock_gates trueset_ccopt_property merge_clock_logic trueset_ccopt_property clone_clock_gates trueset_ccopt_property clone_clock_logic true

复制其他4路ICG后,每路ICG都可以摆放靠近各自控制的寄存器。所以等效于clock gating cell会被摆放至靠近leaf端。这样实现的结果是对我

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

873

873

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?