上周咱们社区IC后端训练营学员遇到下面这个LVS错误,自己尝试分析无法解决后,找小编申请远程协助解决。

手把手教你数字IC后端设计实现PR Innovus在线LVS检查方法

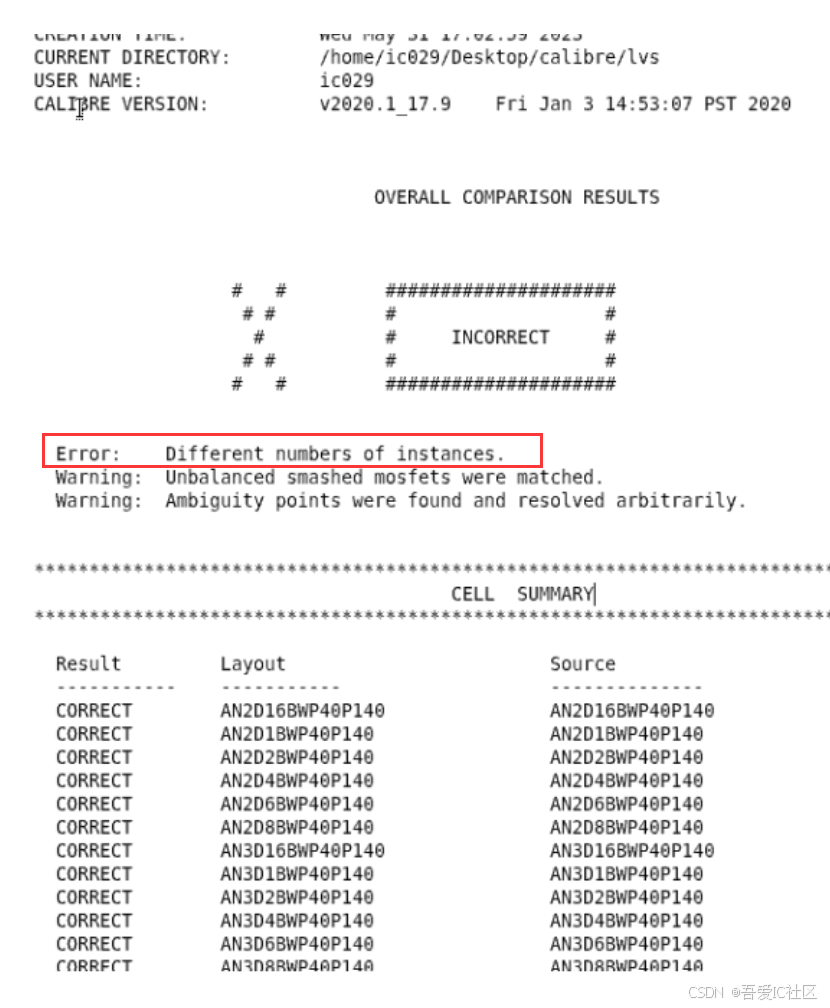

【思考题】如果在跑Calibre LVS过程中报如下图所示的ERROR,请问应该如何解决?这类错误通常是什么问题导致的呢?

从这位学员截图看,我第一反应是这个问题有两大原因。

1)数据版本不匹配(写gds和写netlist的数据用的不同一个database)

2)写netlist时可能把有device的cell 强制no output

今天我们就登录服务器来还原整个debug分析的思路和过程,希望对大家以后debug分析LVS有所帮助。

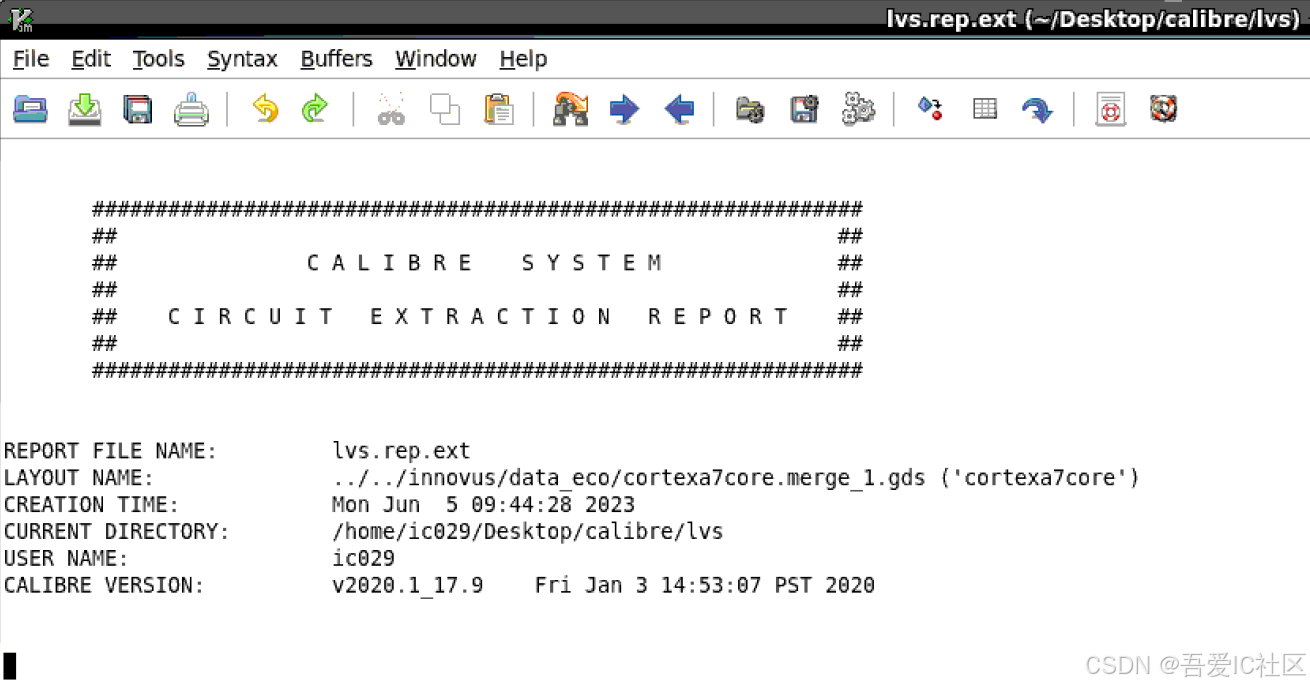

首先,分析LVS结果我们需要查看下LVS的gds抽取报告。

从这个报告我们看出,里面的report很干净,没有任何的警告和错误。所以工具在做gds抽取时并没有什么问题。

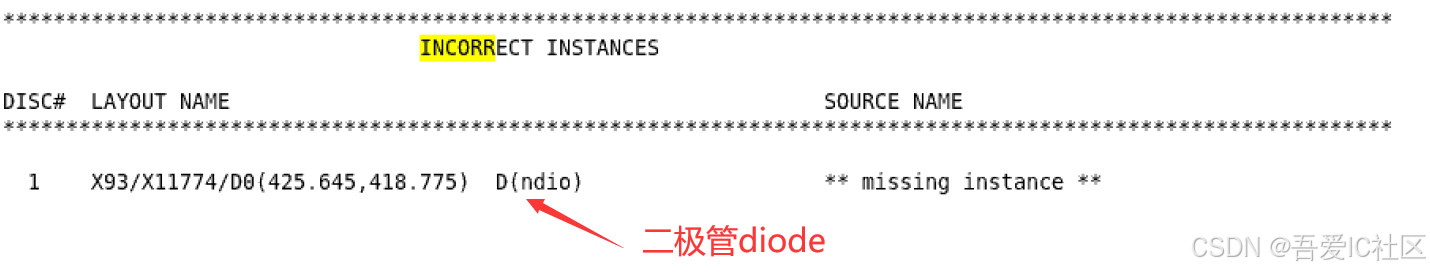

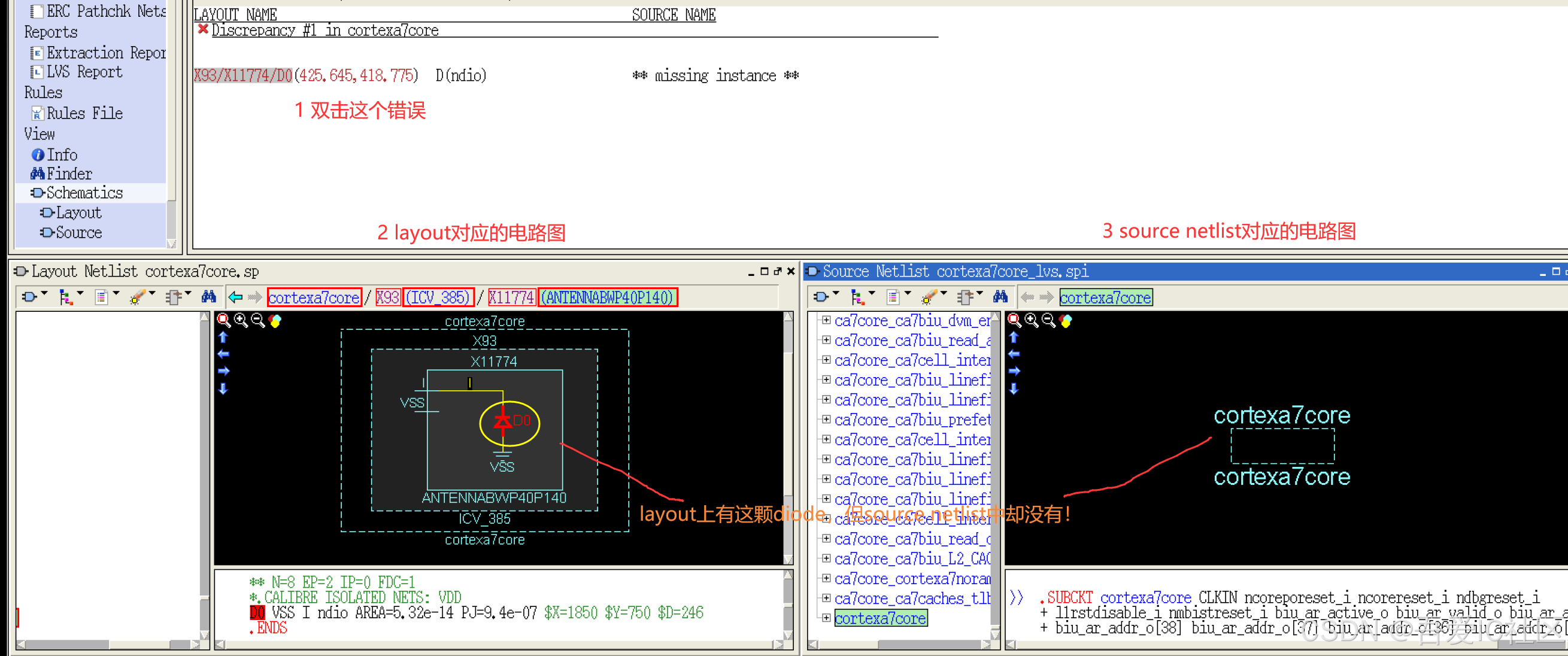

接着,我们打开lvs的结果报告,快速定位到"INCORRECT"位置,这里的错误是报Layout中多了一个ndio,因为source中提示missing instance,即我们用来做LVS用的spice netlist中并没有这颗cell。

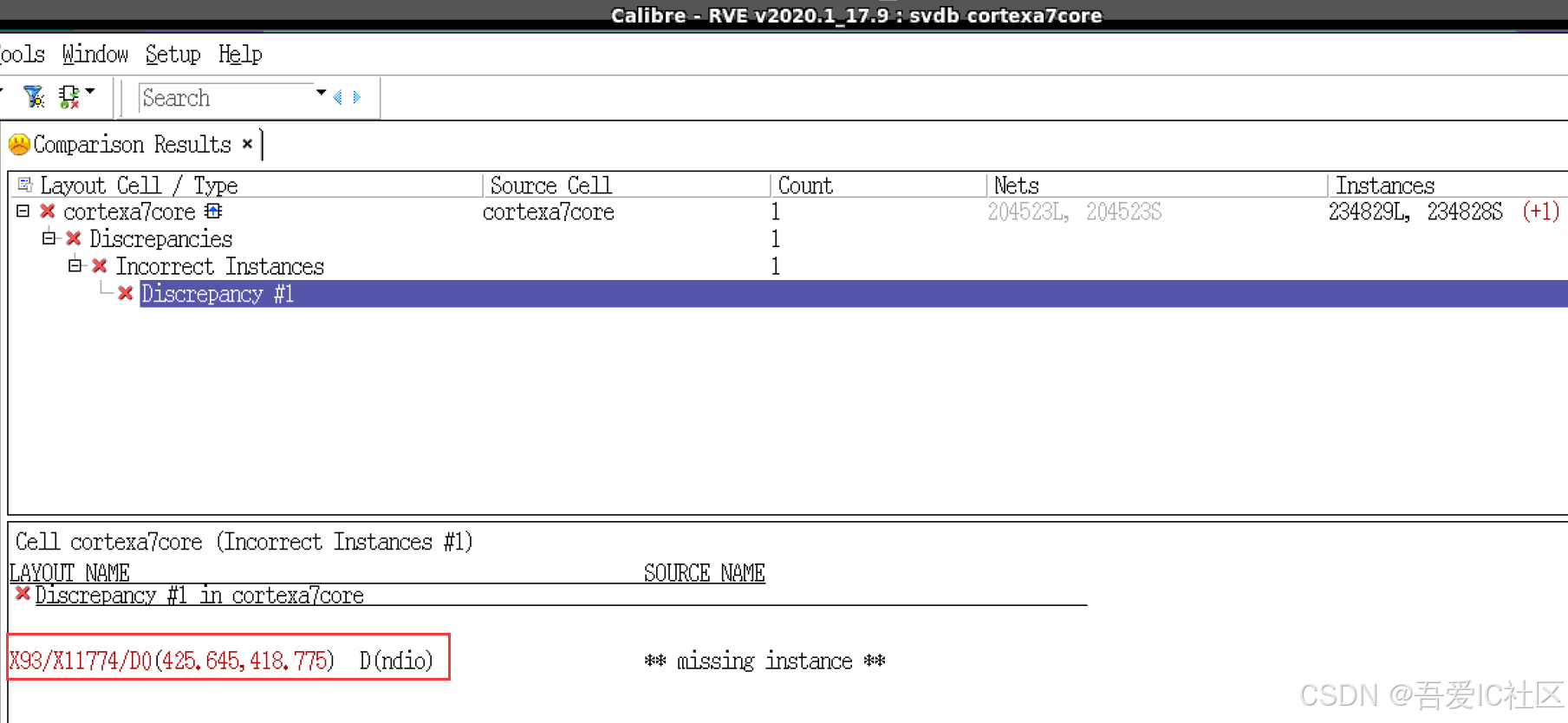

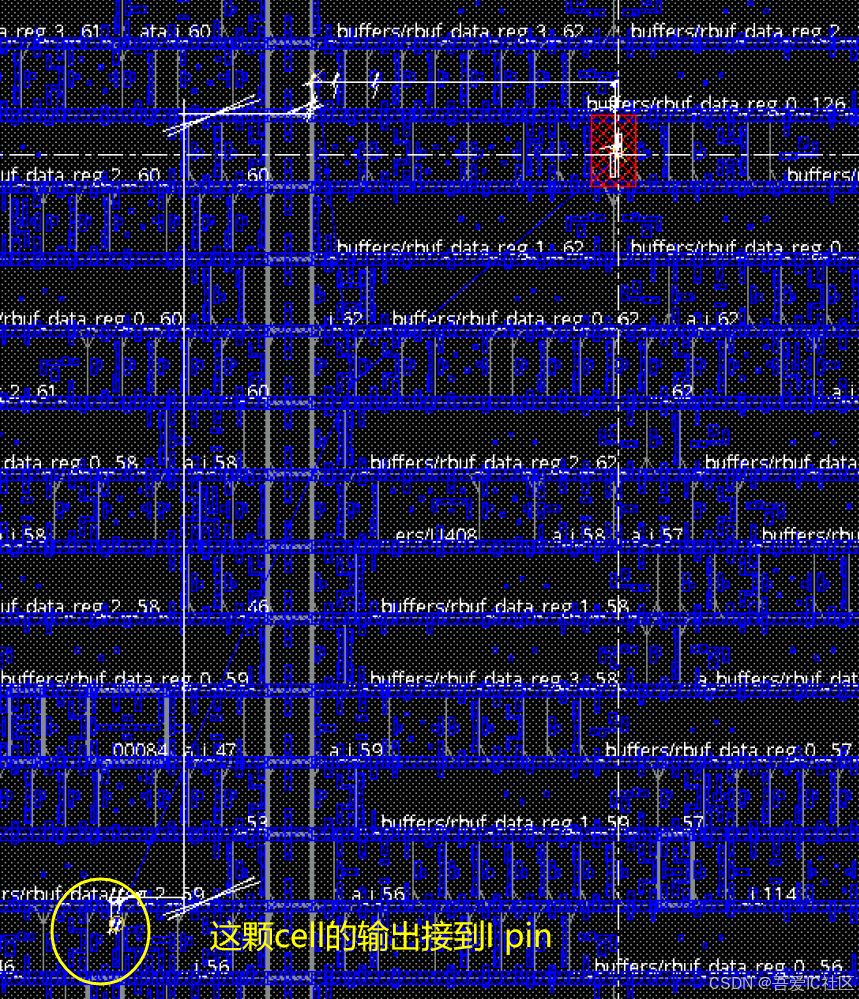

为了具体看下这个错误的详细信息,我们通过calibre打开设计merge后的gds,并load出LVS的svdb,结果如下图所示。这个通过GUI图形界面方式看到的错误信息和LVS report中看到的信息是一致的。只不过这里我们可以通过双击错误的地方快速定位到layout中具体的位置。

所以,我们双击这个错误的地方,自动就会加载出Layout netlist和Source netlist的电路原理图,如下图所示。

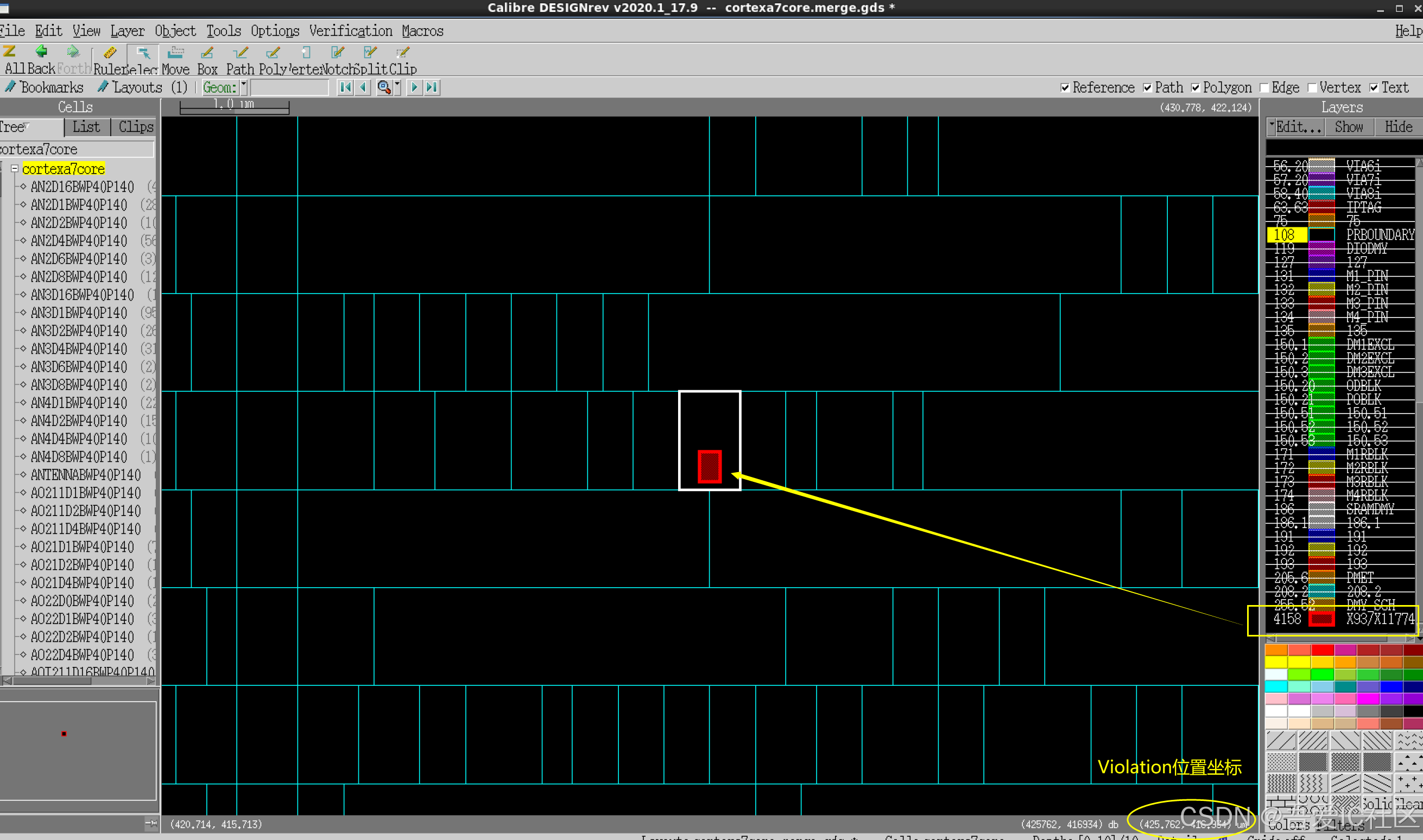

同样在calibre的GDS界面也会高亮出具体violation的位置。通过这个我们可以看到具体violation的具体坐标。

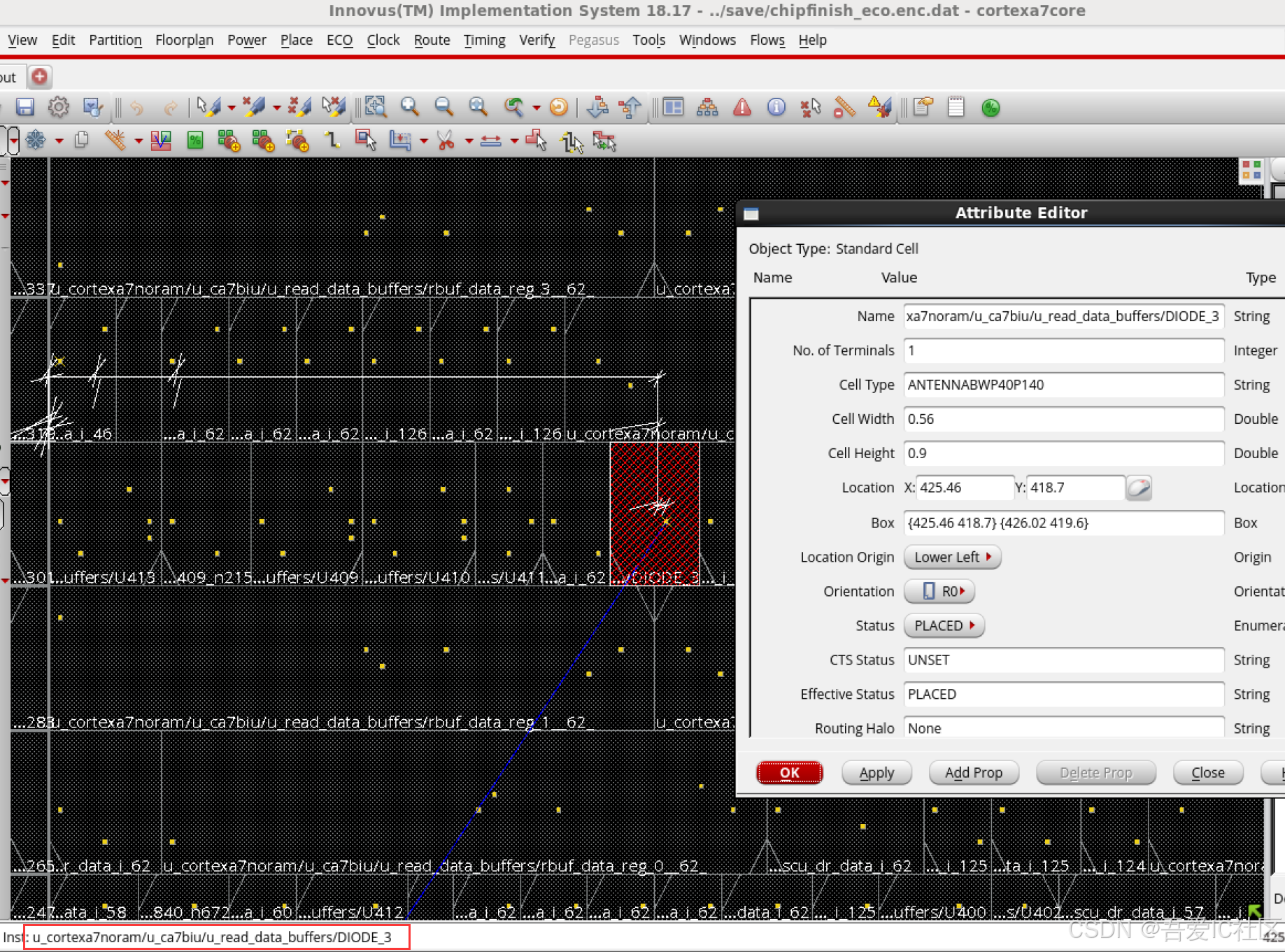

如果你不太习惯在calibre中看,我们可以拿着这个坐标去innovus中去寻找这颗cell到底是什么。其中从上面我们已经知道这颗cell其实是二极管ANTENNA cell。

这说明layout中的确有这颗cell,而且它的名字叫DIODE_3。那我们这时候就应该去看下LVS用的spice netlist。经过搜索我们发现这个spice netlist中的确没有叫DIODE_3的cell,只找到DIODE_1和DIODE_2。

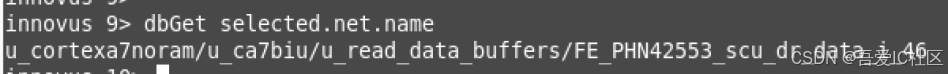

所以,为了让这个LVS比过,小编准备给这个netlist添加这样一个cell。但这个ANTENNA CELL有个I pin是需要连线,所以我还得去layout中去看到底这个I Pin是要连接到哪一条net上去。

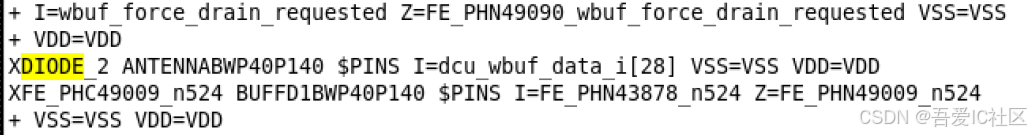

经过这么一分析,它应该连接到FE_PHN42553_scu_dr_data_i_46这条net。

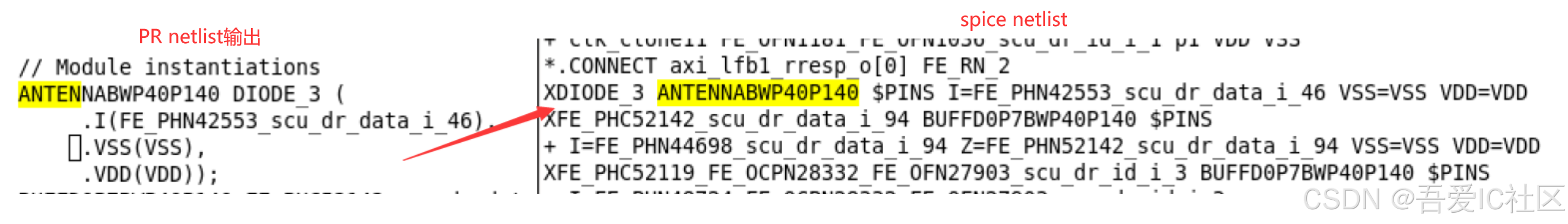

所以改后的spice netlist如下图右侧所示。左侧也一并贴出来,目的是希望大家能够把pr netlist和spice netlist做一个对比,这样才能知道他们的对应转换关系。

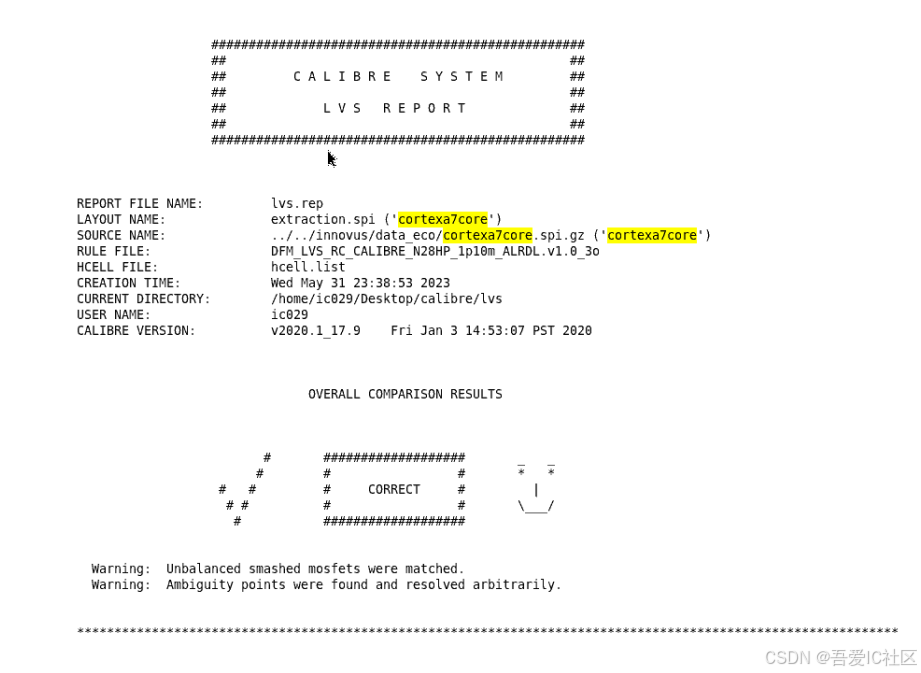

经过这么修改后,我们可以重新跑下LVS,结果如下所示。

至此这个LVS问题就解决了。但是小编认为这个spice netlist不会凭空少掉一颗diode cell。所以初步怀疑是学员误删了。为了证实这个猜想,我们来看看PR netlist输出的netlist是否有DIODE_3这颗cell。经查果然pr netlist中就是有这颗cell。

那会不会是v2lvs转换出的问题呢?那我们重新来做下v2lvs并查看是否会丢失这颗cell。从最新的结果看也并没有少这样的diode。所以v2lvs转换过程也没有问题。

所以,在我们实际项目中经常会因为工程师的误操作或者不良的工作习惯而出现一些比较奇怪的问题。但是只要我们掌握了正常分析问题的思路,我们还是可以把很快定位到有问题的点并高效解决这类问题。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?