在做我们IC后端训练营项目时,我们反复强调在placement阶段做完都要做一些检查。这些检查主要有以下几方面。

1)setup timing可以接受

2)max transition,max cap符合要求

3)congestion overflow控制在1.5%以内

4)最关键路径timing path是否合理(不要出现过渡优化或者优化不到位的情况)

5)VT Ration比例统计

6)input floating检查

7)low power相关检查,比如isolation cell input是否被插buffer了?

关于芯片流片Tapeout需要逐个review的事项,小编已经整理了一个非常全面的Tapeout checklist表格,感兴趣的可以前往下载。当然,各位在芯片Tapeout review上有拿不定的时候,也可以联系小编进行技术咨询(提供技术咨询,Tapeout Review等服务)。

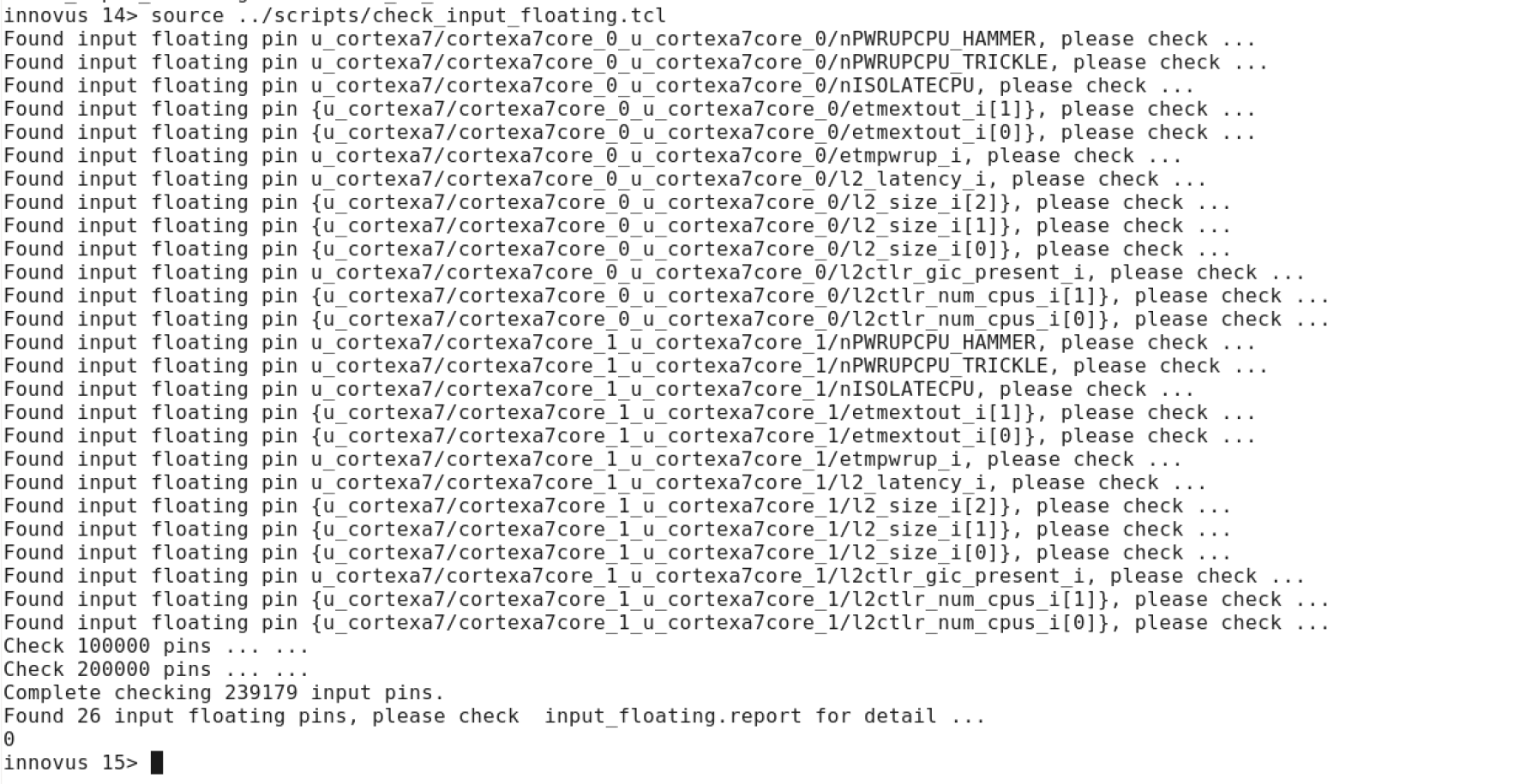

下图所示为学员跑完placement后做的input floating检查的报告。这里报告cpu子模块的input端口存在很多悬空的情况。

本案例报告的子模块input端口悬空是因为netlist中把这些端口接到0或1电平,但是我们没有给这类信号加tie cell!

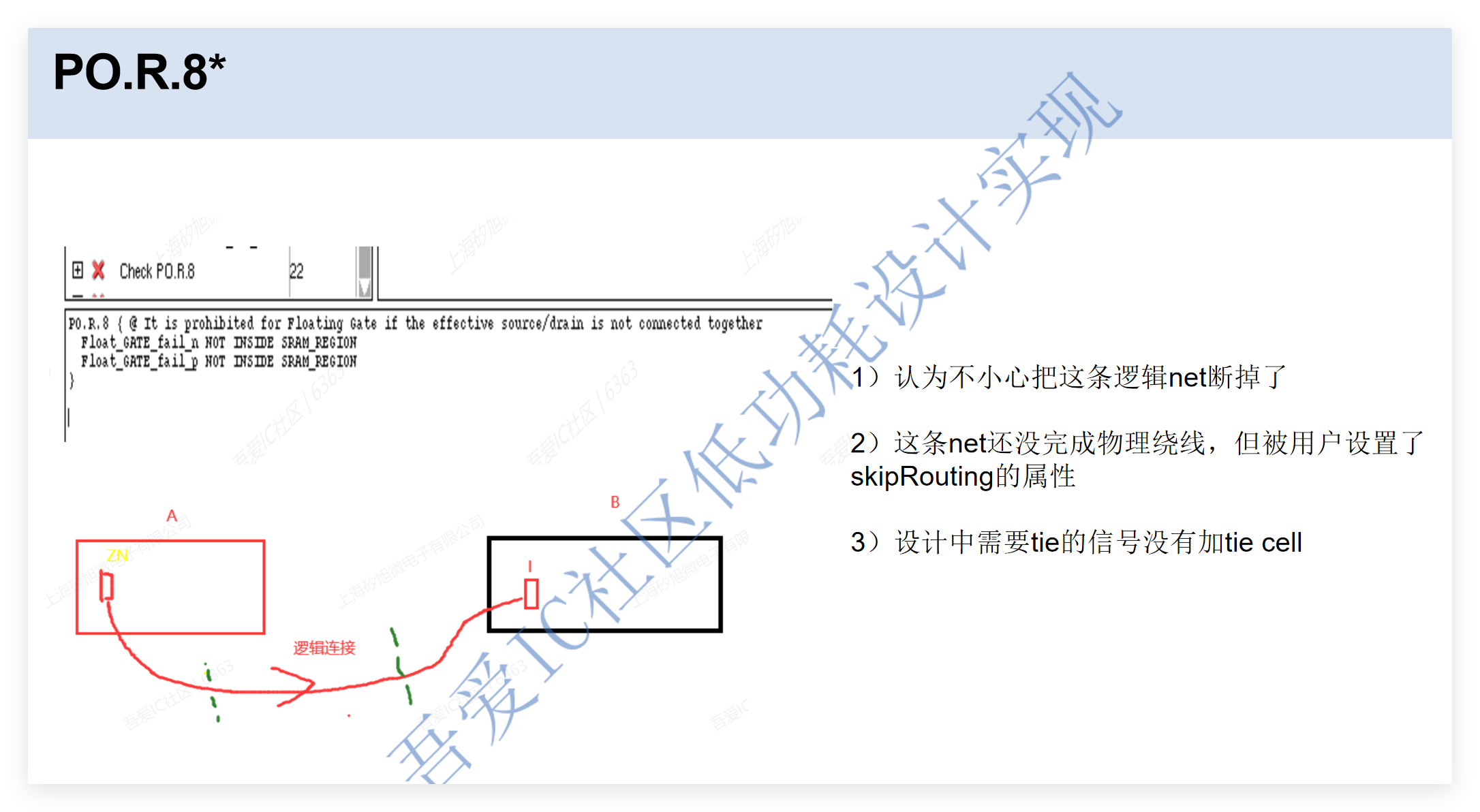

这类input floating(gate floating)问题将来在calibre DRC检查中也会报对应的DRC Violation,PO.R.8 Violation。

下面分享ICC2和Innovus两大工具添加tie cell的万能脚本。

ICC2添加tie cell的脚本:

set supply_net_list [list]

foreach_in_coll net [get_nets -all [list VDD VSS] {

lappend supply_net_list [get_attr $net full_name]

}

connect_tie_cells

-objects [get_pins -of_obj [get_nets -all $supply_net_list] -leaf]

-obj_type port_inst

-tie_high_lib_cell TIEHBWP16P90CPD

-tie_low_lib_cell TIELBWP16P90CPD

-max_wirelength 20

Innovus添加tie cell的脚本:

setTieHiLoMode -prefix Tie -maxFanout 8 -maxDistance 20 -cell “TIEHBWP16P90CPD TIELBWP16P90CPD”

##addTieHiLo

addTieHiLo -powerDomain PD_PSO

addTieHiLo -powerDomain PD_AW_ON

值得注意的是当我们设计中存在多个power domain时,务必针对每个power domain分别添加tie cell,否则工具默认只会对最顶层的power domain添加tie cell!

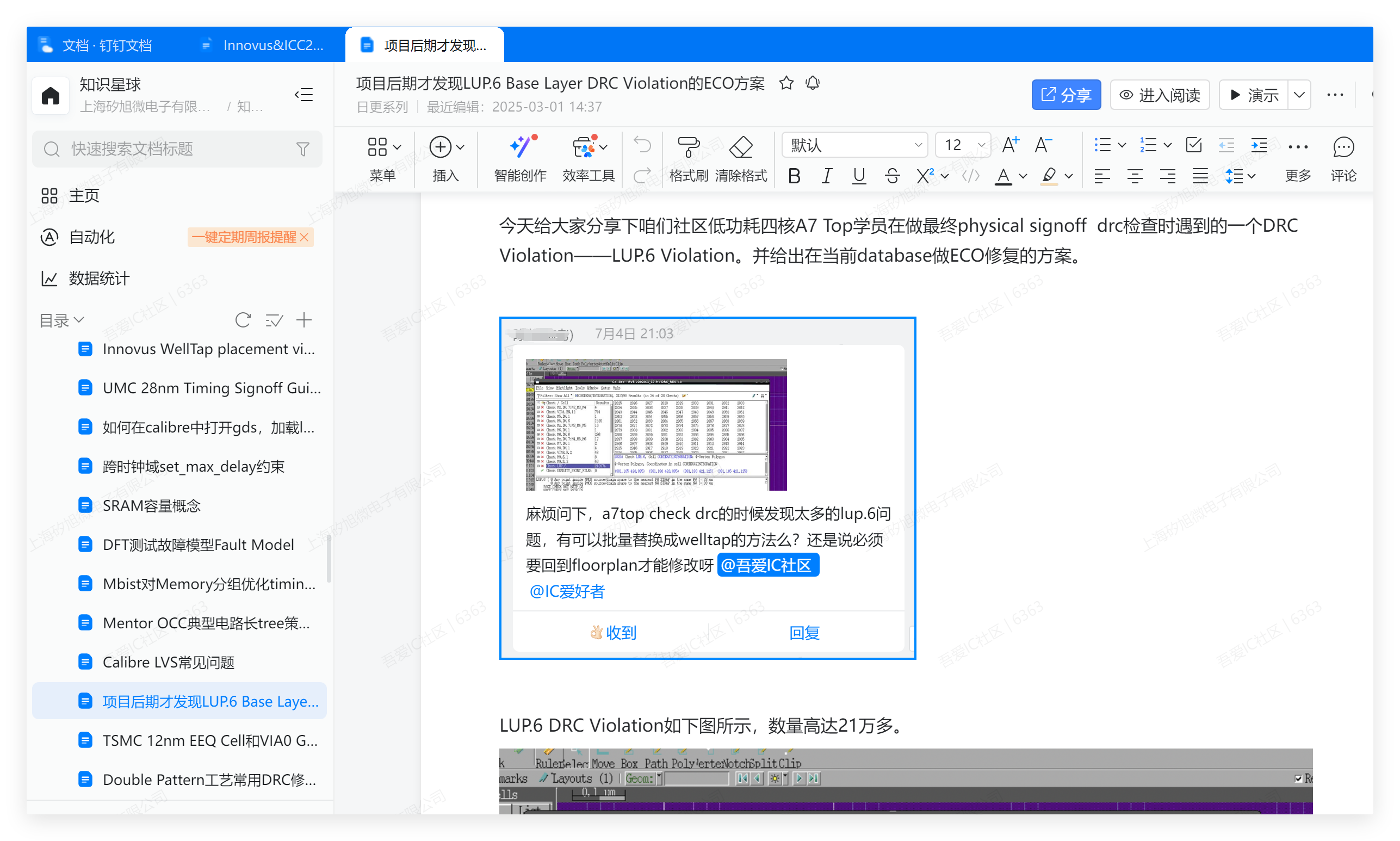

如果你在芯片tapeout review阶段才发现设计中存在大量input floating或LUP.6 DRC Violation的情况,我们也是可以通过ECO的方式来进行修复。

1490

1490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?