目录

大家好,这里是程序员杰克。一名平平无奇的嵌入式软件工程师。

Xilinx分享篇已经对GPIO、AXI DMA的总结进行了分享,本篇系列开始分享Ultrascale+ Zynq SOC的PS端UART的分享总结;

本篇系列总结的都是基于Ultrascale+ ZYNQ系列的内容,与其他系列会有一些内容上的差异,注意区别。

好的,话不多说,直接进入主题。

01 PS端 UART 控制器介绍

UART Controller 特性

-

波率可调

-

送/接收FIFOs可配置,有字节、半字、字的APB访问机制

-

数据位可配置为6bit、7bit、8bit

-

停止位可配置为1bit、1.5bit、2bit

-

校验位可配置为奇(Odd)、偶(Even)、空格(Space)、标记(Mark)、无校验(No Parity)

-

支持奇偶校验错误、帧错误、溢出错误检测

-

断行的生成以及检测

-

支持自动回显、本地环回、远程环回通道模式

-

可产生中断

-

支持Modem Control:CTS,RTS,DSR,DTR,RIDCD

-

时钟:APB时钟(100Mhz)以及uart_ref_clock([1,100]Mhz)

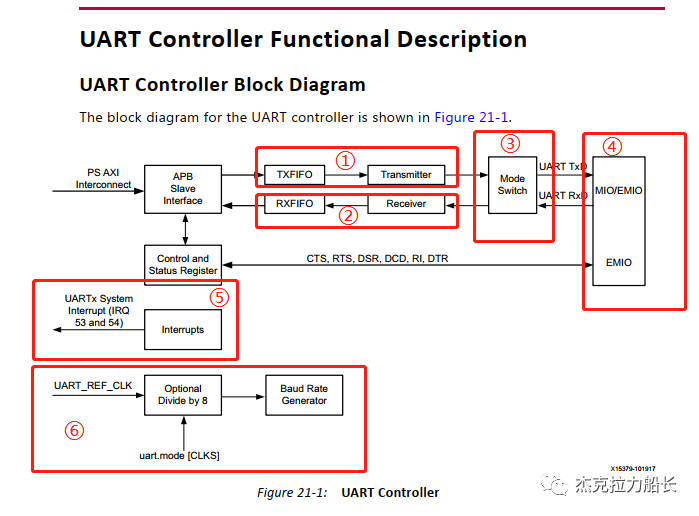

UART Controller功能模块图

| 模块 | 描述 |

| ①Transmit FIFO | TxFIFO存储来自APB Slave接口的数据,数据出FIFO到Transmitter的移位寄存器,TxFIFO最大数据位宽为8bit;FIFO深度为64字节; |

| ② Receiver FIFO | RxFIFO存储来自Receiver移位寄存器接收到的数据,RxFIFO最大数据位宽为8bit;FIFO深度为64字节; |

| ③Mode Switch | 控制UART的模式(普通、自动回传、本地环回、远程环回);通过mode寄存器的[CHMODE]位配置不同的模式; |

| ④MIO/EMIO | 实际与外部进行连接的物理引脚 |

| ⑤Interrupts | 中断模块,用于产生中断(IRQ); |

| ⑥Baud Rate Generator | 为Tx/Rx产生波特率时钟和比特周期时钟; |

-

Baud Rate Generator

| 说明 | |

| ①输入时钟选择 | 波特率模块输入时钟为UART_REF_CLK或者UART_REF_CLK/8,通过配置模式寄存器的[0(CLKS)]位进行选择;经过一个二选一选择器输出为sel_clk: sel_clk = (UART_Ref_clock) || (UART_Ref_clock/8); |

| ②生成波特率采样时钟 | sel_clk经过CD分频后,作为波特率的采样时钟,通过Baud Rate Generator寄存器的CD字段设置(CD=[1,65535]); Baud_sample = sel_clk/CD; 分频后的Baud Sample时钟分为两路:

|

| ③生成Tx、Rx传输时钟 | Baud Sample时钟经过[BDIV+1]分频后作为Rx、Tx的传输时钟,通过Baud Rate Divider寄存器的BDIV字段设置(BDIV=[4,255]): Baud_sample = sel_clk/[ CD * (BDIV + 1) ]; |

-

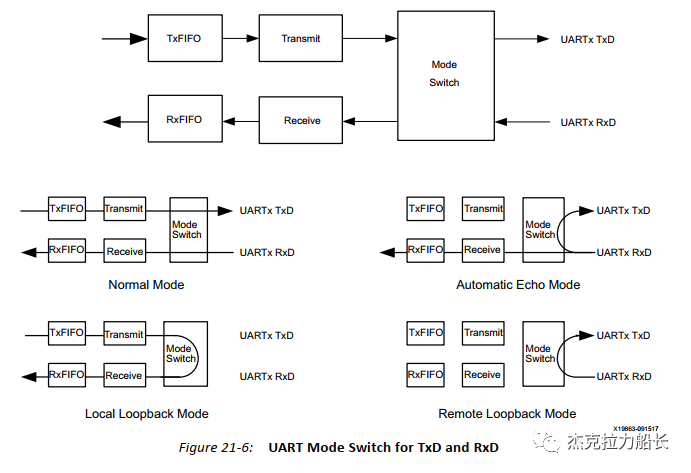

Mode Switch

| 模式 | 描述 |

| Normal Mode | 标准UART操作; |

| Automatic Echo Mode | 从RxD引脚接收数据,同时RxD引脚连接TxD引脚,接收的时候通过RxD返回; |

| Local Loopback Mode | TxD和RxD与Mode Switch没有物联引脚连接,数据从Transmit发送,到Receive接口; |

| Remote Loopback Mode | RxD引脚与TxD引脚直接连接,Controller不参与接发过程; |

UART Controller寄存器总览

串口寄存器如下表所示:

02 文章总结

本篇推文主要是对Ultrascale+ ZYNQ Uart Controller外设进行简单介绍,对于文档中数据的捕获、传输有效等内容并未在此描述。

参考文档:

《UG1085-zynq-ultrascale-trm.pdf》

940

940

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?