约束管理器是cadence allegro中设置规则的一个平台,在这里可以设置各种约束规则,是PCB设计的核心。在进行PCB走线时,如果提前设置好规则,可以节约人工检查时间,提高工作效率。

一、界面介绍

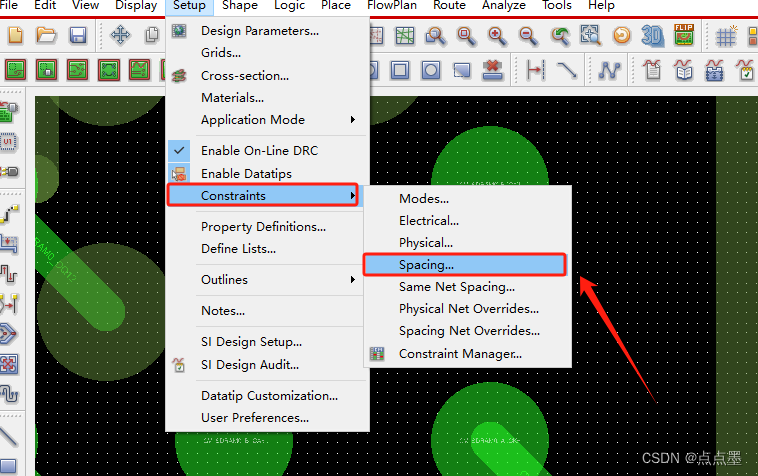

1、选择菜单“setup-constrains-spacing”,进入约束管理器界面。

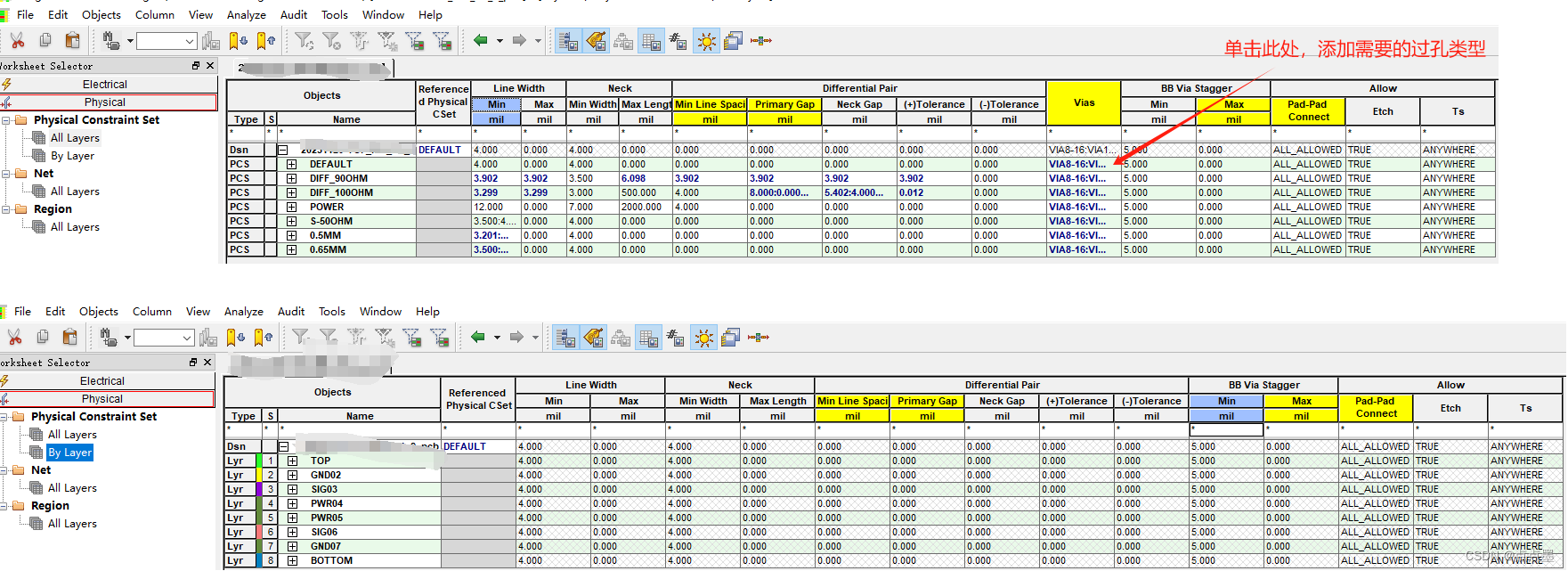

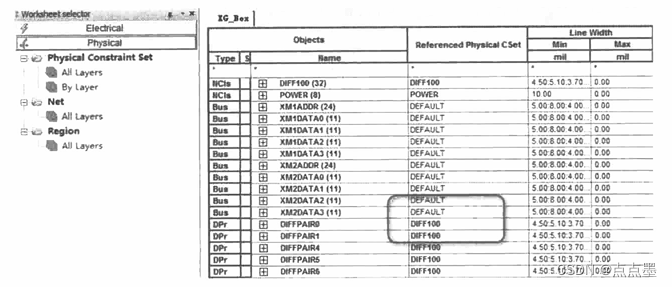

界面如下图

2、通过单击左侧约束管理器窗口左侧的的6个栏目进行对应的设置

Electrical: 电气规则设置,常规的等长、差分及走线长度均在此色好孩子

Physical: 物理规则设置,设置走线线宽、差分对的对内线距

Spacing:间距规则设置,设置对象之间的间距;

Same Net Spacing : 相同网络间距规则设置,设置相同对象之间的间距

Properties: 对象的属性设置

DRC: DRC设置

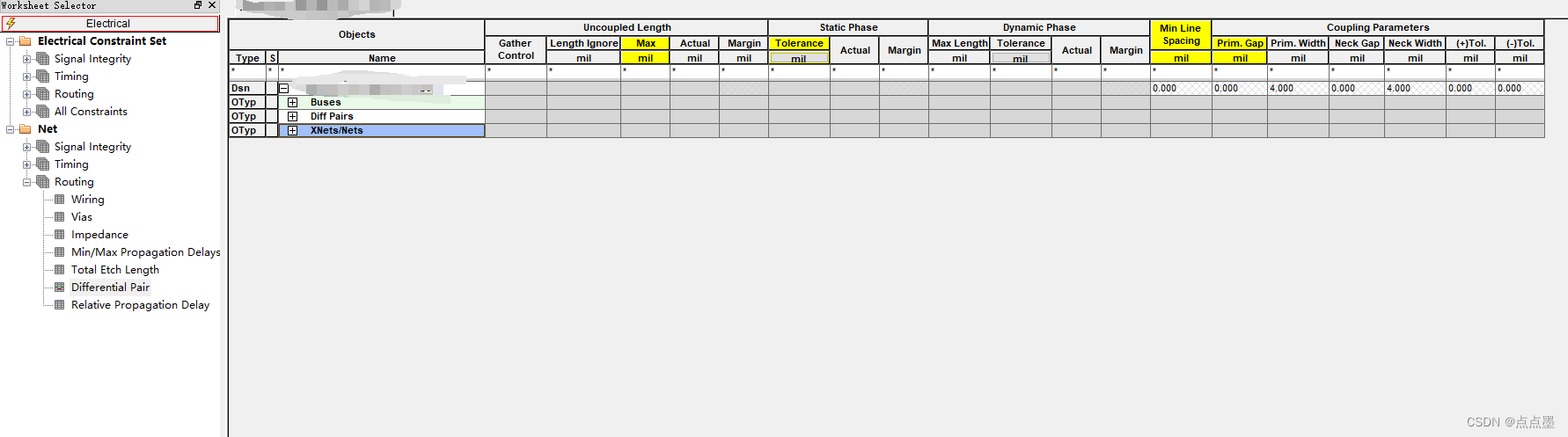

3、单击Electrical, 出现1-3界面

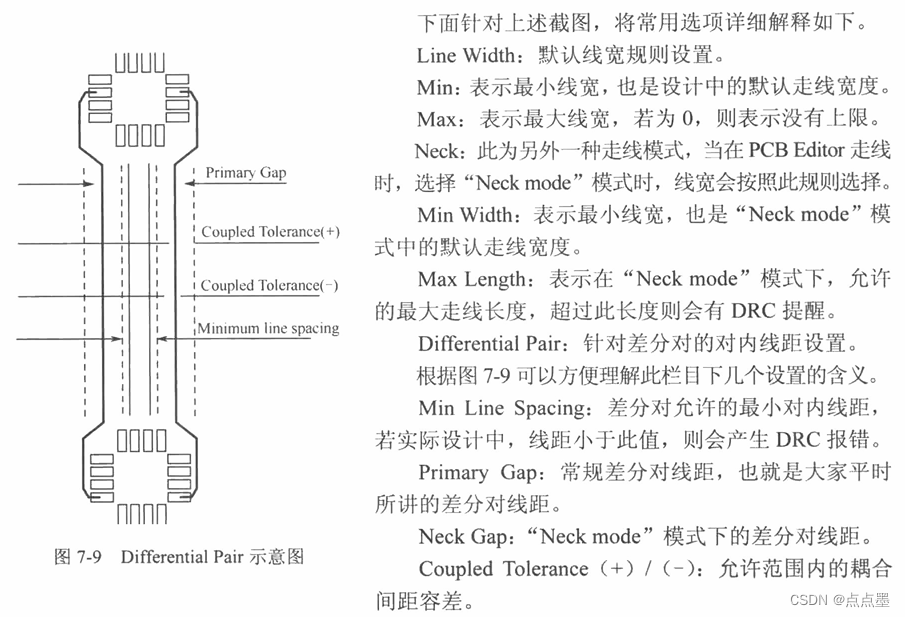

这个功能模块中,我们常用的是“Net”下的“Routing”中的“Total Etch Length”、"Differential Pair"及“Relative Propagation Delay”3 栏

Total Etch Length : 用来设置走线的实际走线长度规则;

Differential Pair : 用来设置于差分对相关的参数,如走线长度误差;

Relative Propagation Delay : 用来设置等长,如常见的DDR等长等;

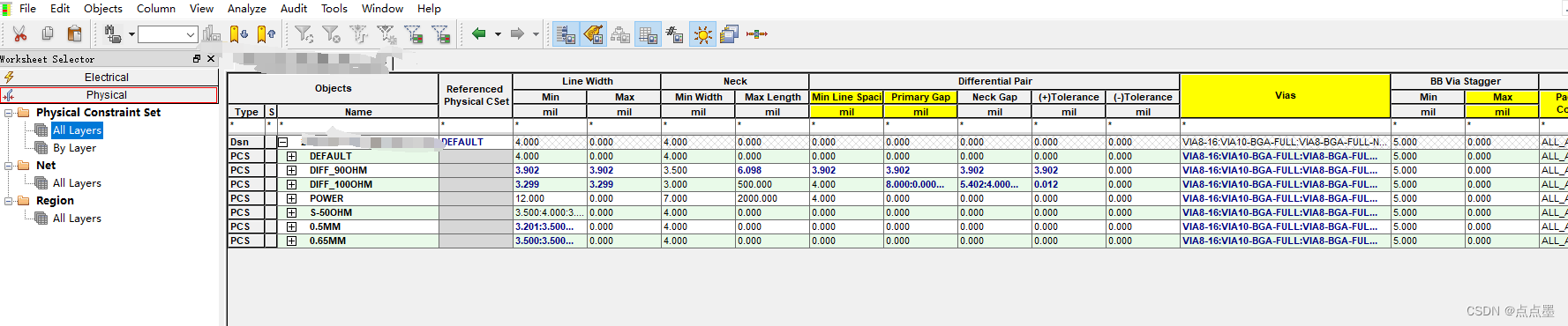

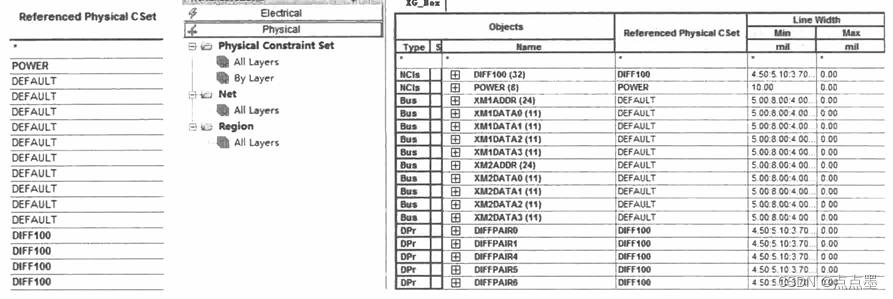

4、单击Physical, 出现1-4界面

Physical Constraint Set 栏目下的“All Layers”和"By Layer"用来设置线宽规则,可以将其中的规则赋予下面的Net中的网络,网络就会根据其规则走线;

注意:“All Layers”和"By Layer“里面的规则是相通的,设置“All Layers”后,“By Layer”中的也会同步更新。如下面两张图所示。

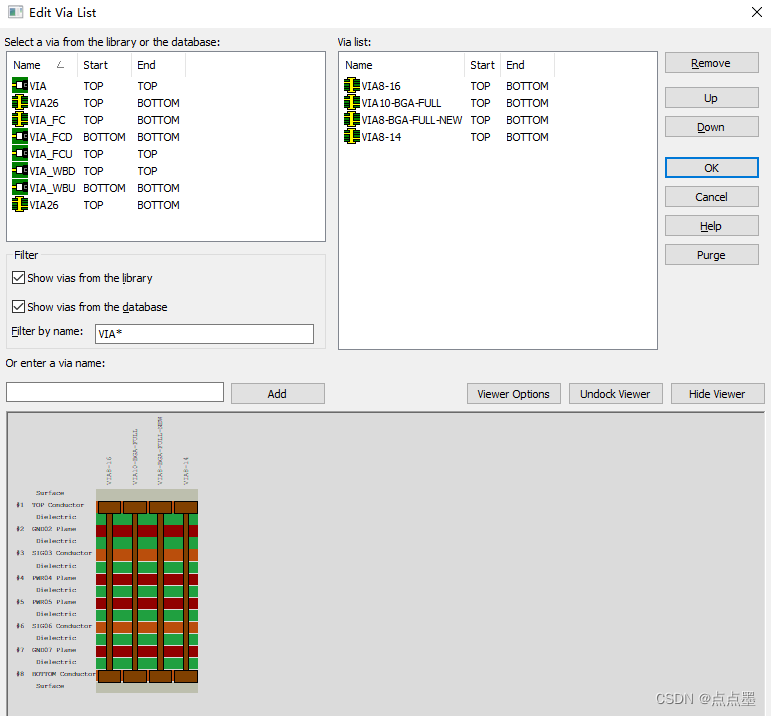

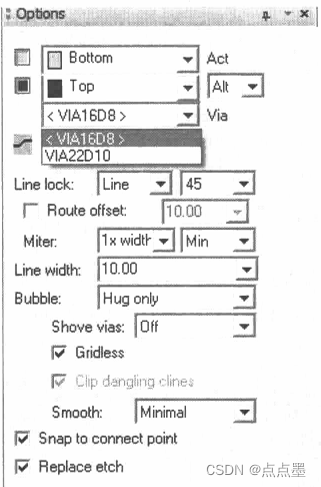

Vias :用于添加需要的过孔类型

双击左侧的焊盘,则会添加到右侧的 “Vialist” 处,在 “Vialist” 处,可以添加多种 Via 类型,并且可以将它们排序,从而设定优先级,

“Net” 栏目。

单击 “AULayers” 如图7-14 所示,网络就可以在此界面赋予规则或直接填写参数。

可以在对应的网络名后,从下拉菜单中选择规则,选择好对应的规则后,则后面的参数会随之变化。

在默认情况下,所有Net均选择 “DEFAULT” 规则。

在已选规则的情况下,我们可以更改“LineWidth” 等条目下的参数,此优先级更高,

“Region” 栏目。

此栏目用于设置区域规则,此规则优先级高于上述所讲规则设置;一般的应用场合是在一些密度较大的区域(比如EMMC,DDR等),将线宽、间距等规则数值设置得小些,方便设计。

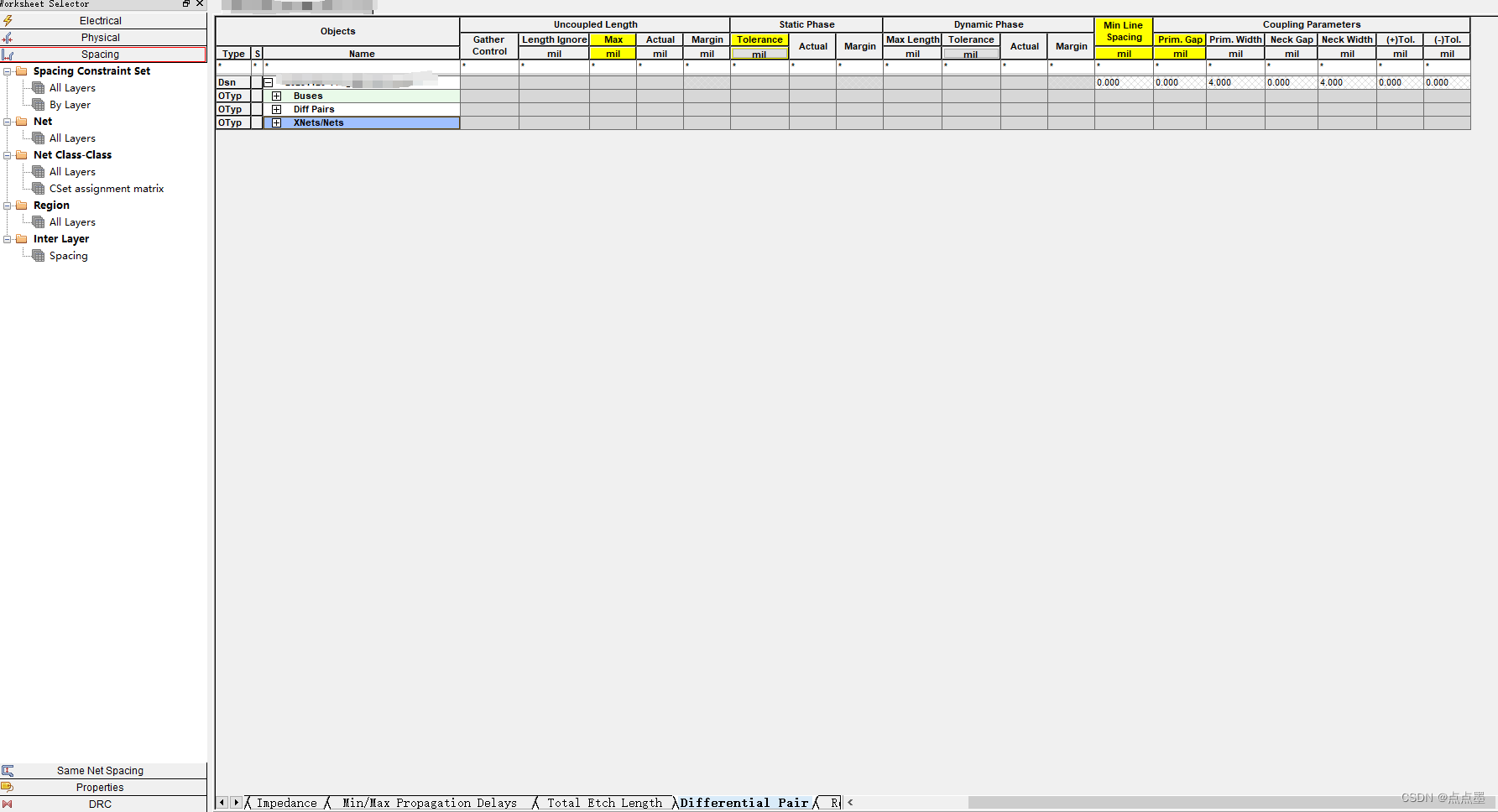

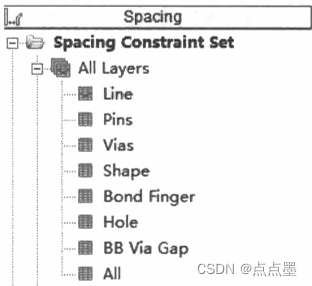

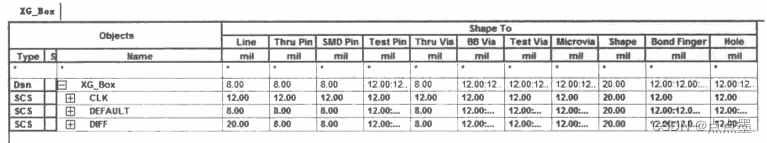

5、单击Spacing,

(1)Spacing Constraint Set 栏目

在Spacing Constraint Set 栏目下面的All Layers 和By Layer用来设置间距规则,可以将其中的规则赋予下面的Net中网络,网络就会根据规则来走线。

注:“All Layers”和“By Layer”里面的规则设置是相通的,设置“All Layers”后,“By Layer”

里面也会同步更新设置。

''All Layers下面有这些对象 在设置规则时,需要设置对象两两之间的间距;

在设置规则时,需要设置对象两两之间的间距;

选择 “Line” 时,要设置Line对象与Line 、ThruPin、 SMDPin、 TestPin 、ThruVia、 BBVia、 Test Via、 Microvia 、Shape、 Bond Finger、 Hole 这些对象之间的间距数值。

选择“Shape”时,同样要设置对应的选项;

在这里,要设置Shape对象与Line ThruPin SMDPin TestPin Thru Via BB Via Test Via Microvia Shape Bond FingerHole 这些对象之间的间距数值。

注意:当设置过Line To Shape的规则后,则Shape To Line中的数值会自动同步。

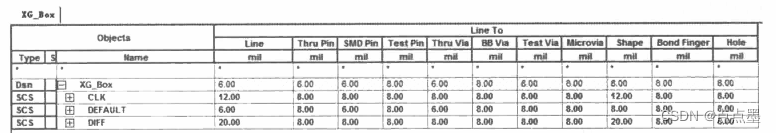

“Net” 栏目,单击“All Layers” ,网络就可以在此界面赋予规则或者直接填写参数。

技巧:在已选规则的情况下,我们可以更改后面对应的参数,此优先级更高。

③ “Region” 栏目。

“ Region” 栏目用于设置区域规则,此规则优先级高于上述所讲规则设置。一般应用的场

合是在一些密度较大的区域,将线宽、间距等规则数值设置得小些,方便设计。

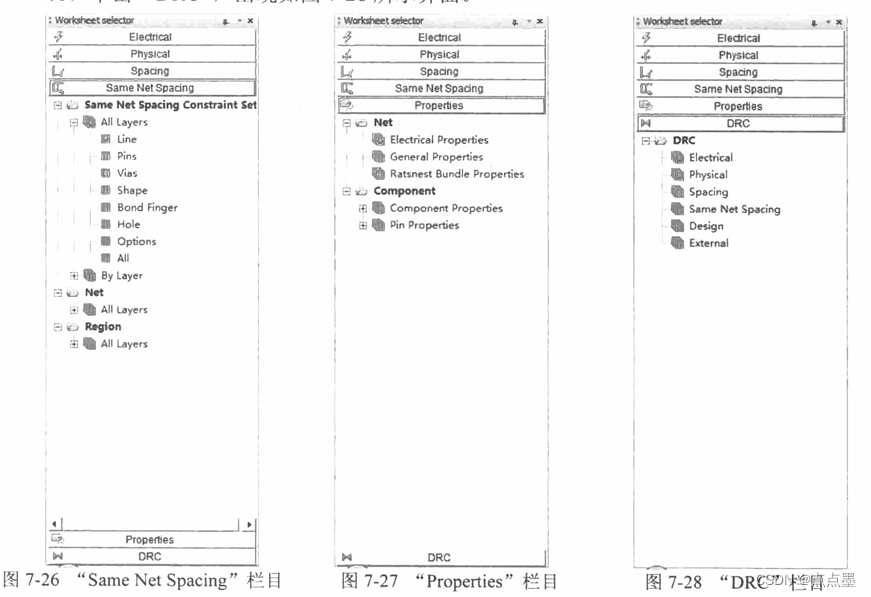

(6) 单击 “SameNetSpacing” 出现如图7-26 所示界面。

此栏目设置同 “Spacing” 栏目,不过其中的设置只对相同网络的对象之间生效。在实际

设计中,可以根据实际需要是否设置此栏目,以及是否开启此项规则设置检查。

(7) 单击 “Properties”,此栏目主要设置网络和元件的属性,添加及删除需要的特征属性,方便我们的设计。在PCB Editor 界面中,也可通过其他命令来添加及删除特征属性。

(8) 单击 “DRC”, 出现如图7-28所示界面。“DRC” 栏目主要设置与DRC规则检查相关的选项,一般可以保持默认即可。

1152

1152

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?