AMD/Xilinx Versal - Insert AI Engine into your custom PL design and take it to hardware in 15 min

AMD/Xilinx Versal - Insert AI Engine into your custom PL design and take it to hardware in 15 min

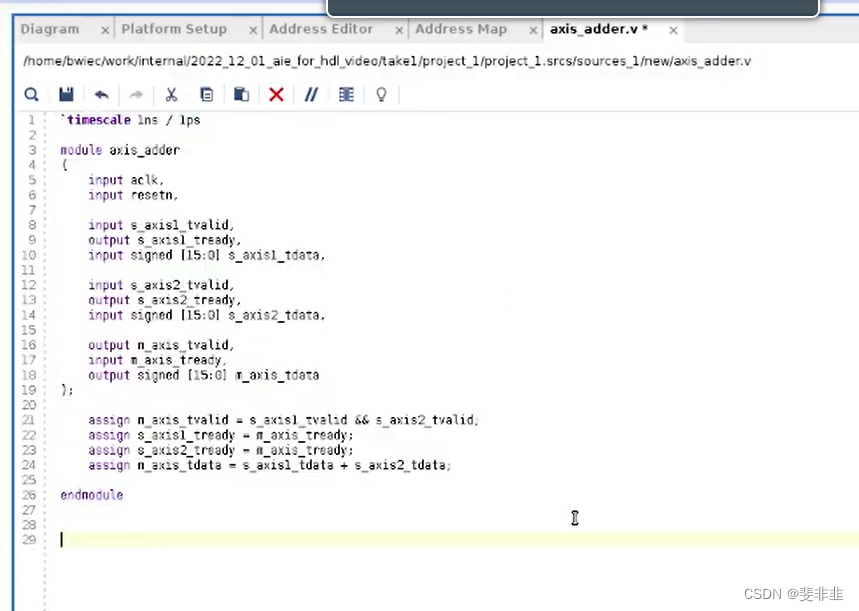

`timescale 1ns/ 1ps

module axis_adder(

input aclk,

input resetn,

/*

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TID" *)

// Uncomment the following to set interface specific parameter on the bus interface.

// (* X_INTERFACE_PARAMETER = "CLK_DOMAIN <value>,PHASE <value>,FREQ_HZ <value>,LAYERED_METADATA <value>,HAS_TLAST <value>,HAS_TKEEP <value>,HAS_TSTRB <value>,HAS_TREADY <value>,TUSER_WIDTH <value>,TID_WIDTH <value>,TDEST_WIDTH <value>,TDATA_NUM_BYTES <value>" *)

input [<left_bound>:0] <s_tid>, // Transfer ID tag (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TDEST" *)

input [<left_bound>:0] <s_tdest>, // Transfer Destination (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TDATA" *)

input [<left_bound>:0] <s_tdata>, // Transfer Data (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TSTRB" *)

input [<left_bound>:0] <s_tstrb>, // Transfer Data Byte Strobes (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TKEEP" *)

input [<left_bound>:0] <s_tkeep>, // Transfer Null Byte Indicators (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TLAST" *)

input <s_tlast>, // Packet Boundary Indicator (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TUSER" *)

input [<left_bound>:0] <s_tuser>, // Transfer user sideband (optional)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TVALID" *)

input <s_tvalid>, // Transfer valid (required)

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 <interface_name> TREADY" *)

output <s_tready>, // Transfer ready (optional)

*/

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 s_axis1 TVALID" *) input s_axis1_tvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 s_axis1 TREADY" *) output s_axis1_tready,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 s_axis1 TDATA" *) input signed[15:0] s_axis1_tdata,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 s_axis2 TVALID" *) input s_axis2_tvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 s_axis2 TREADY" *) output s_axis2_tready,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 s_axis2 TDATA" *) input signed[15:0] s_axis2_tdata,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 m_axis TVALID" *) output m_axis_tvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 m_axis TREADY" *) input m_axis_tready,

(* X_INTERFACE_INFO = "xilinx.com:interface:axis:1.0 m_axis TDATA" *) output signed[15:0] m_axis_tdata

);

assign m_axis_tvalid = s_axis1_tvalid && s_axis2_tvalid;

assign s_axis1_tready = m_axis_tready;

assign s_axis2_tready = m_axis_tready;

assign m_axis_tdata = s_axis1_tdata + s_axis2_tdata;

endmodule

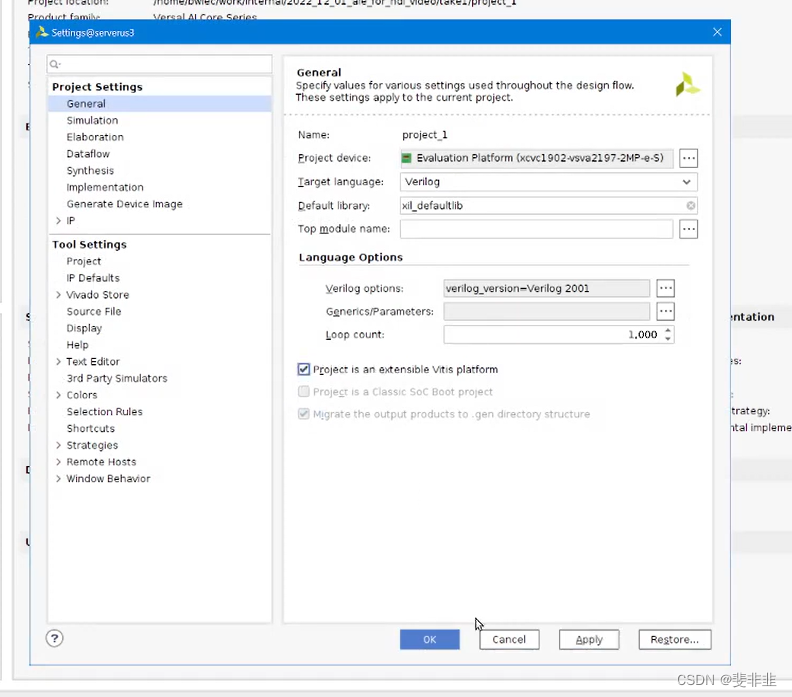

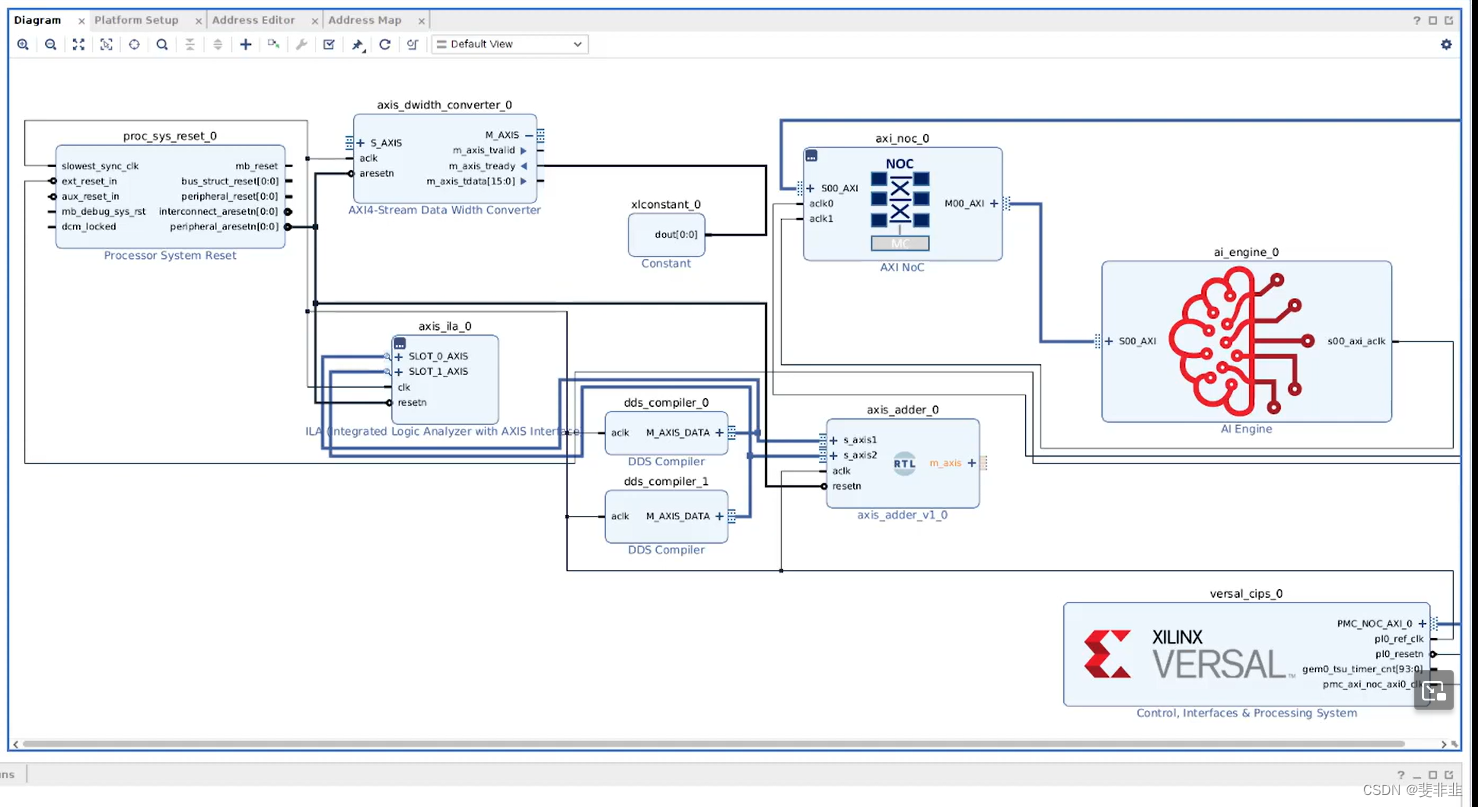

platform setup

axi 列表里的port都是 bd里边没有的编号, 也不用在bd里边手动增加这些编号的port

#include "graph.h"

fir_filter uut;

int main(int argc, char ** argv)

{

uut.init();

uut.run();

uut.end();

return 0;

}

//

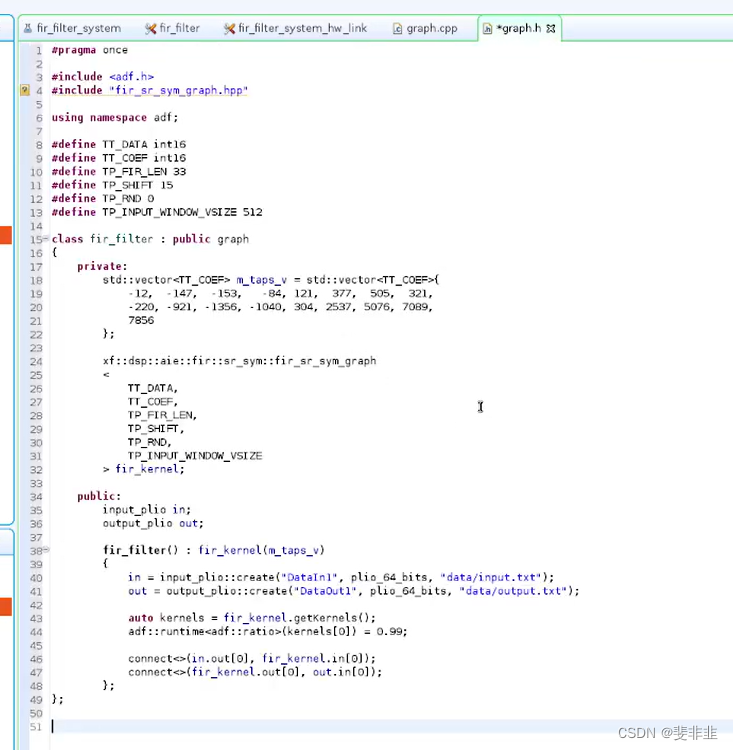

#pragma once

#include <adf.h>

#include "fir_sr_sym_graph.hpp"

using namespace adf;

#define TT_DATA int16

#define TT_COEF int16

#define TP_FIR_LEN 33

#define TP_SHIFT 15

#define TP_RND 0

#define TP_INPUT_WINDOW_VSIZE 512

class fir_filter : public graph

{

private:

std::vector<TT_COEF> m_taps_v = std::vector<TT_COEF>{

-12, -147, -153, -84, 121, 377, 505, 321,

-220, -921, -1356, -1040, 304, 2537,5076,7089,

7856

};

xf::dsp::aie::fir::sr_sym::fir_sr_sym_graph

< TT_DATA,

TT_COEF,

TP_FIR_LEN,

TP_SHIFT,

TP_RND,

TP_INPUT_WINDOW_VSIZE

> fir_kernel;

public:

input_plio in;

output_plio out;

fir_filter() : fir_kernel(m_taps_v)

{

in = input_plio::create("DataIn1", plio_64_bits, "data/input.txt");

out = output_plio::create("DataOut1", plio_64_bits, "data/output.txt");

auto kernels = fir_kernel.getKernels();

adf::runtime<adf::ratio>(kernels[0])= 0.99;

connect<>(in.out[0], fir_kernel.in);

connect<>(fir_kernel.out, out.in[0]);

//connect<>(in.out[0], fir_kernel.in[0]);

//connect<>(fir_kernel.out[0], out.in[0]);

//connect<>(in.out[0], kernels[0].in[0]);

//connect<>(kernels[0].out[0], out.in[0]);

};

};

1465

1465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?