接上篇

PCIE5.0规范学习(中文版)(1)_pcie学习课程-CSDN博客

PCIE5.0规范学习(中文版)(2)_pcie培训文档-CSDN博客

目录

2.2.4 Routing and Addressing Rules

2.2.4.1 Address-Based Routing Rules

2.2.4.2 ID Based Routing Rules

2.2.6 Transaction Descriptor事务描述符

2.2.6.4 放松排序(Relaxed Ordering,RO)和基于ID的排序(ID-Based Ordering,IDO)

2.2.6.6 事务描述符——Traffic Class(TC)

2.2.3 TLP Digest Rule

- 对任何TLP来说,TD中1b的值TLP摘要域的存在,包括TLP的末尾end-to-end的CRC值。

- TD bit值与观察到的大小(计算data payload)不一致的TLP是畸形TLP

- 这是与接收端有关的汇报错误

- TD bit值与观察到的大小(计算data payload)不一致的TLP是畸形TLP

- 如果TLP的中间或最终的PCIE接收机不支持ECRC检查,则接收机必须无视TLP摘要。

- 如果TLP的接收方支持ECRC检查,接收机在TLP根据摘要规则,将TLP摘要域的值解释为ECRC值。

2.2.4 Routing and Addressing Rules

TLP路由有三条原则机制:地址、ID和隐式路由。本章定义了地址和ID路由的规则。隐式路由只用于Message请求,会在2.2.8中覆盖。

2.2.4.1 Address-Based Routing Rules

- 地址路由用于内存和IO请求

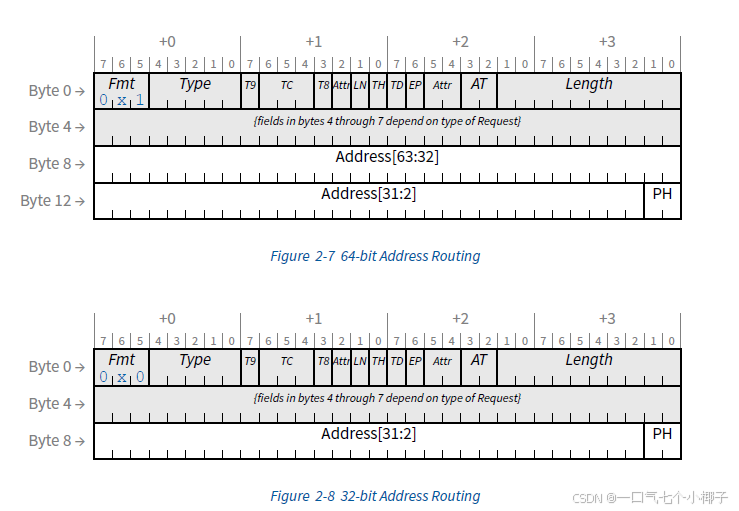

- 具体描述了两种地址格式,64-bit格式使用4DW header和32-bit模式使用3DW header。

- 对于内存读内存写和原子化操作请求,地址类型(AddressType,AT)域是被编码的表10-1编码的。对于所有其他的请求,AT域被保留除非明确的状态。轻量(LN)读和轻量写有具体的需求,见第六章。

- 如果TH为1,则PH域编码见表2-15。如果TH为0,则PH域保留。

- 地址映射到TLP header见表2-5

表2-5 地址域映射

| Address bit |

32-bit Addressing |

64-bit Addressing |

| 63:56 |

Not Applicable |

Bits 7:0 of Byte 8 |

| 55:48 |

Not Applicable |

Bits 7:0 of Byte 9 |

| 47:40 |

Not Applicable |

Bits 7:0 of Byte 10 |

| 39:32 |

Not Applicable |

Bits 7:0 of Byte 11 |

| 31:24 |

Bits 7:0 of Byte 8 |

Bits 7:0 of Byte 12 |

| 23:16 |

Bits 7:0 of Byte 9 |

Bits 7:0 of Byte 13 |

| 15:8 |

Bits 7:0 of Byte 10 |

Bits 7:0 of Byte 14 |

| 7:2 |

Bits 7:0 of Byte 11 |

Bits 7:0 of Byte 15 |

- 内存读写和原子操作请求可以使用任何格式。

- 对于小于4GB的地址,Requester必须使用32-bit格式。如果64-bit格式地址的请求地址小于4GB,则接收机的行为不会被指定(例:地址高32bits均为0)。

- IO读请求和IO写请求使用32-bit格式。

- 所有的Agent必须解码在header中的地址,不允许出现地址混叠。

2.2.4.2 ID Based Routing Rules

- ID路由被用在配置请求、ID路由消息和完成中。本规范定义了一些ID路由消息(表F-1),其它规范被允许定义额外的ID路由消息。

- ID路由使用总线、设备和Function号(如有)以指定TLP的目的地。

- 对于非ARI路由ID,总线、设备和(3-bit)Function号到TLP header的映射见表2-6,图2-9及2-11。

- 对于ARI路由ID,总线和(8-bit)Function号到TLP header的映射见表2-7,图2-10及图2-12。

表2-6 非ARI ID路由的header域布局

| Field |

Header位置 |

| 总线号Bus Number[7:0] |

Byte8[7:0] |

| 设备号Device Number[4:0] |

Byte9[7:3] |

| Function号[2:0] |

Byte9[2:0] |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2471

2471

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?