3.电气规范

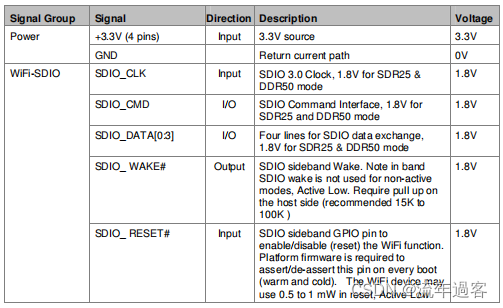

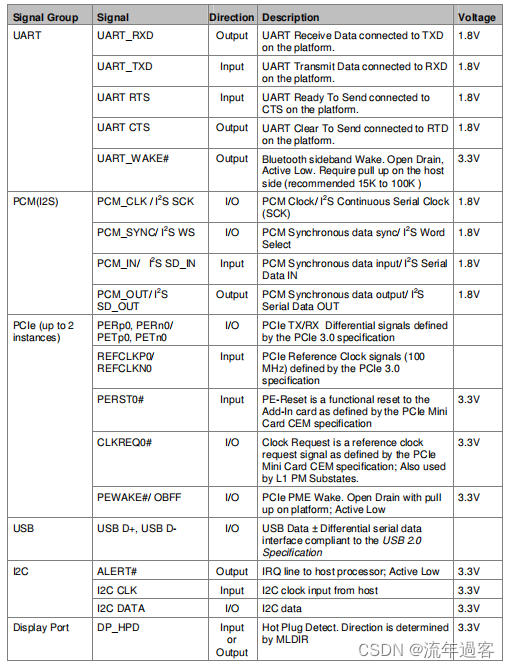

3.1 Connectivity Socket 1 系统接口信号

表15适用于Socket 1-SD和Socket 1-DP输出版本。

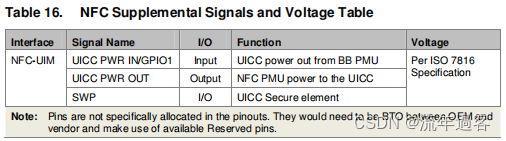

3.1.1.补充NFC信号

当一个SIM设备被用作安全元素时,NFC解决方案可以与表16中列出的附加信号相结合。

3.1.2.电源和地

PCI Express M.2 Socket 1使用一个3.3 V电源。电压源,+3.3 V,预计在系统的备用/暂停状态期间可用,以支持通信卡上的唤醒事件处理。

一些较高频率的信号需要与周围的信号进行额外的隔离,使用交错接地(GND)引脚的概念,分离连接器内的信号。这些引脚应视为普通地脚,在卡设计中立即连接到地平面。

3.1.3.PCIE接口

PCI Express接口支持x1 PCI Express接口(一车道)。一个车道由一个输入和一个输出的高速差分对组成。还支持一个PCI快速参考时钟。有关PCI Express接口信号的功能要求的更多细节,请参阅PCI Express基础规范。

注:车道极性:

- 默认情况下,PETp0和PETn0引脚(连接器的发射器差分对)应连接到系统板上的PCI Express发射器差分对和PCI Express M.2插卡附加卡上的PCI Express接收器差分对。同样,默认情况下,PERp0和PERn0引脚(连接器的接收器差分对)应连接到系统板上的PCI Express接收器差分对以及PCI Express M.2插卡附加卡上的PCI Express发射器差分对。

然而,p和n连接可以反向连接,以简化PCB跟踪路由,并在需要时最小化通孔。所有PCI Express接收器都将自动车道极性倒置作为链路初始化和训练的艺术,并将独立地纠正每个车道上的极性。有关链路初始化和培训的更多信息,请参考PCI快速基础规范的第4.2.4节。

请求说明:链接电源管理

- PCI Express基础规范要求使用实现基于PCI Express的应用程序的PCI Express M.2插件卡来实现链路电源管理状态,包括支持L0和L1(除了主L0和L3状态)。对于PCI Express M.2卡的实现,L0s和L1状态的活动状态PM也应默认启用。有关活动状态PM的更多信息,请参阅PCI快速基础规范的第5.4节。

Socket 1输出提供了一个额外的PCI快速通道。这些额外的PETx1和PERx1信号集可以作为原始PCI快速接口的第二通道,或者,它们可以使用第二组REFCLKx1和相邻保留针上的一组辅助信号来形成完整的第二个PCI快速x1接口。

3.1.4.PCIE辅助信号

辅助信号提供在系统连接器上,以协助实现某些系统级别的功能。PCI Express体系结构不需要这些信号,但诸如PCIExpressM.Card2等特定实现可能需要这些信号。高速信号电压水平与先进的硅工艺兼容。可选的低速信号被定义为使用+3.3V电源,因为它是可用的最低公共电压。大多数ASIC工艺具有与+3.3V兼容的高压(厚栅氧化物)I/O晶体管。+3.3V电源的使用允许PCI快速信号与现有的控制总线结构一起使用,避免了一组缓冲的信号和总线之间的桥梁。

PCI Express M.2卡插件卡和系统连接器支持以下章节中描述的辅助信号。

3.1.4.1.参考时钟

REFCLK+/REFCLK信号用于协助板卡的PCIE接口定时电路的同步。在卡接口处的参考时钟的可用性可以通过第3.1.4.2节中所述的CLKREQ#信号进行门控。当参考时钟不可用时,它将处于停放状态。停车状态是当时钟不是由时钟驱动器驱动,而REFCLK+和REFCLK-都被接地终端电阻拉到地面时。有关参考时钟信号的功能和公差要求的更多细节,请参阅PCIE卡机电规范。

3.1.4.2.CLKREQ#信号

CLKREQ#信号是一个开漏、主动低信号,由PCI快速M.2插I卡功能驱动低,请求PCI快速参考时钟可用(活动时钟状态),以允许PCI快速接口发送/接收数据。CLKREQ#信号的操作由链路控制寄存器中的启用时钟功率管理位的状态决定(偏移量为010h)。禁用时,在向卡施加电源时,应始终维护CLKREQ#信号,但在L1 PM子状态期间可能断言它除外。启用后,CLKREQ#信号可能会在L1链路状态下失效。

CLKREQ#信号也被L1 PM子状态机制所使用。在这种情况下,可以通过系统或插件卡断言CLKREQ#,以启动L1退出。有关实现L1 PM子状态时CLKREQ#信号的功能要求的详细信息,请参阅PCI快速基本规范。每当启用动态时钟管理,并且当一个卡停止驱动CLKREQ# low时,它表示设备已准备好让参考时钟从活动时钟状态转换为停放(不可用)时钟状态。当CLKREQ#被取消断言时,参考时钟不能保证被主机系统停放,并且即使当CLKREQ#被模块取消断言时,模块设计也应容忍一个有效的参考时钟。

在通电时,每当复位时,以及每当需要参考时钟处于活动时钟状态时,板卡必须驱动CLKREQ#信号过低。每当断言PERST#,包括当设备不在D0时,应断言CLKREQ#。需要注意的是,PCI快速设备必须延迟取消确认其CLKREQ#信号,直到它准备好停放其参考时钟。当设备需要将其链路放回L0链路状态时,设备必须能够断言其时钟请求信号,无论参考时钟是否活动或停放。最后,该设备必须能够感知其上游定向接收端口上的电空闲中断,并断言其时钟请求,无论参考时钟是活动的或停放的。

CLKREQ#的断言和取消断言与引用时钟相比是异步的。未实现PCI Express接口的插卡应在卡上不连接。CLKREQ#比标准的开放漏极信号有额外的电气要求,允许它在断电的设备和其他可能通电的设备之间共享。附加要求包括仔细的电路设计,以确保施加于CLKREQ#信号网络的电压不会造成组件损坏,即使没有施加特定组件的电源。此外,设备必须确保不会降低CLKREQ#,除非在所有情况下都有意断言CLKREQ#;包括当相关功能处于D3冷状态时。这意味着任何实现CLKREQ#的组件都必须被设计为:

无电源的CLKREQ#输出电路,如果对CLKREQ#的其他电源施加电压,则不会损坏。

当从其CLKREQ#生成逻辑卸下电源时,未供电输出不存在低接地或任何其他电压的阻抗路径。

这些额外的要求确保了当供电和非供电组件的CLKREQ#输出线结合在一起时,CLKREQ#信号网络继续正常工作。值得注意的是,最常用的开式漏极和三态缓冲电路设计并不满足CLKREQ#的额外电路设计要求。

3.1.4.2.1.通电要求

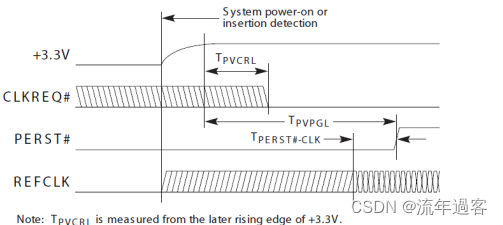

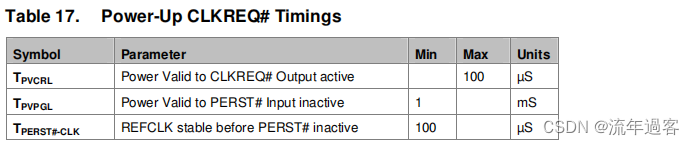

CLKREQ#是响应PERST#断言的断言。通电时,必须由PCI快速设备在延迟(TPVCRL)内确认CLKREQ#,以达到指定的操作限制和PERST#断言(参见图75)。这个延迟是为了让卡上的电源有足够的时间稳定,并在卡启动之前让某些系统功能启动。当断言PERST#时,CLKREQ#不能被取消断言。

在设备通电之前,系统需要让PCI Express设备处于停车时钟状态的参考时钟状态。在设备通电期间,参考时钟的状态未定义,但在PERST#取消断言之前,设置时间TPERST#-CLK必须处于活动时钟状态。表17列出了通电的CLKREQ#计时。

在设备通电之前,系统需要让PCI Express设备处于停车时钟状态的参考时钟状态。在设备通电期间,参考时钟的状态未定义,但在PERST#取消断言之前,设置时间TPERST#-CLK必须处于活动时钟状态。表17列出了通电的CLKREQ#计时。

3.1.4.2.2.动态时钟控制

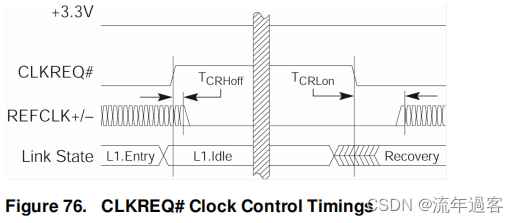

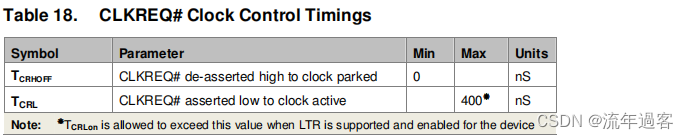

PCI Express设备通电后,当其上游链路进入L1链路状态时,应允许其参考时钟关闭(进入停车时钟状态)。为了实现这一点,设备取消了CLKREQ#(高),并且必须允许参考时钟在延迟内过渡到停车时钟状态(TCRHoff)。图76显示了CLKREQ#时钟控制时序图。要退出L1,设备必须断言CLKREQ#(low)才能重新启用参考时钟。在设备断言CLKREQ#(low)之后,它必须允许参考时钟在转换到活动时钟状态之前继续处于停放时钟的延迟(TCRLon)状态。设备断言CLKREQ#和系统将引用时钟返回到活动时钟状态所需的时间将根据L1恢复的其余部分进行序列化。当设备报告其L1退出延迟时,必须考虑到这个时间。

当PCI Express设备支持并启用延迟容差报告(LTR)时,设备必须允许参考时钟转换到活动时钟状态可能额外延迟到与LTR机制要求一致的最大值。在此延迟期间,参考时钟必须保持停车状态。当在延迟后退出停车状态时,时钟必须在400 ns内稳定且有效。

连接到PCI Express设备的所有链路都必须完成到L1的转换。在设备可以取消断言CLKREQ#之前的空闲状态。当该设备检测到任何接收器端口上的电气空闲中断时,该设备必须断言CLKREQ#。设备必须确认CLKREQ#,同时中断其任何发射机端口上的电气空闲,以最小化L1出口延迟。CLKREQ#时钟控制定时见表18。

TCRHoff没有最大规格,TCRLon也没有最小规格。这意味着系统不需要实现参考时钟停车,或者该实现可能并不总是作用于取消断言CLKREQ#的设备。当一个设备的链接在L2或L3中时,它也应该取消断言CLKREQ#,就像它在L1时一样。

3.1.4.3.时钟请求支持报告和启用

动态时钟协议应使用PCI快速链接功能寄存器中的第18位报告对CLKREQ#的支持。为了启用动态时钟管理,提供了链路控制寄存器的第8位(偏移量010h)。默认情况下,板卡应在初始通电时启用CLKREQ#动态时钟协议。系统软件随后可能会根据需要禁用此功能。有关这些位的更多信息,请参阅PCI快速基础规范,版本1.1(或更高版本)。

3.1.4.4.PERST#信号

取消PERST#信号,指示系统电源在其规定的电压容差范围内并稳定。一旦电源稳定,应使用

PERST#初始化卡功能。

PERST#是在电源关闭时断言的,系统也可以用来强制板卡上的硬件复位。

系统可能会使用PERST#来导致外插件卡的热重置。有关PERST#信号的功能要求的更多细节,请参见PCI快速卡机电规范。

3.1.4.5.WAKE#信号

如果该卡支持唤醒功能或OBFF机制,则PCI Express M.2卡必须实现WAKE#。有关WAKE#信号的功能要求的更多细节,请参阅PCI快速卡机电规范。

3.1.5.USB接口

USB接口支持所有三种模式下的USB2.0(低速、全速和高速)。由于没有单独的USB控制的电压总线,在PCI Express M.2卡插件卡上实现的USB功能有望报告为自供电设备。此接口的所有枚举、总线协议和总线管理特性都由通用串行总线规范,2.0版定义。实现唤醒过程的基于USB的M.2卡需要使用通用串行总线规范中定义的带内唤醒协议(跨USB_D+/USB_D-引脚)。

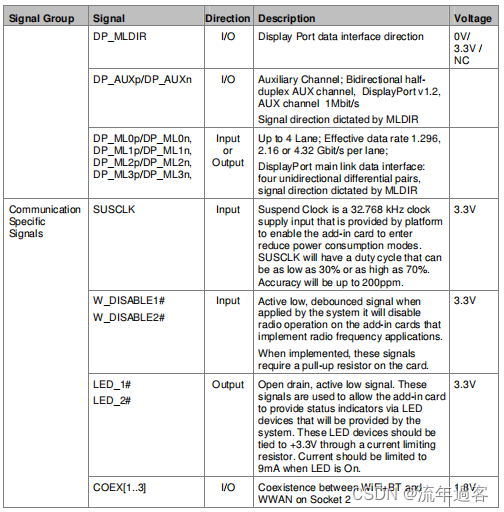

3.1.6.显示端口接口

显示端口接口支持在引用的显示端口规范中定义的全功能实现。支持主链路、辅助通道和热插拔检测(HPD)的全四车道实现。此外,还提供了一个系统级信号MLDIR,以便在安装显示-m.2卡时协助配置该平台。

3.1.6.1.HPD

HPD信号连接到显示端口接口的标准热插头检测信号。此信号的目的是向显示端口源指示活动显示器已连接。HPD的逻辑方向由MLDIR的状态决定。对于无线显示器应用程序,被断言的HPD还应表明系统和远程显示器之间的无线链路已完全运行。当断言HPD时,主机系统软件将知道如何定位和配置远程显示。

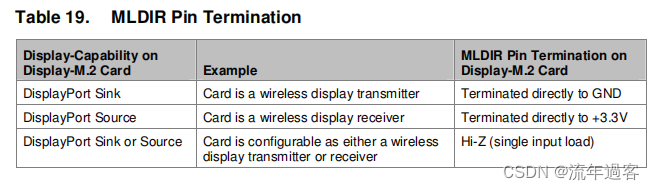

3.1.6.2.MLDIR

MLDIR信号指示M.2卡上的显示端口数据和辅助接口的功能方向;即作为显示相关接口的接收器或源。根据安装在插座中的M.2卡的特定显示端口功能,该卡上的MLDIR信号终端应如表19所示。对于提供双向显示端口功能的M.2卡,配置显示界面方向的机制是应用程序和/或产品特定的,并没有由本规范定义。

3.1.7.SDIO接口

M.2 SDIO接口由以下标准SDIO信号组成:

四个双向数据信号,每个数据速率可高达100Mbits/秒(总计400Mbits/秒)

一个双向CMD信号。

一个时钟信号高达50MHz,这些信号符合标准的SDIO规范。

有关SDIO接口信号的功能要求的详细信息,请参考SDIO规范。M.2 SDIO接口还包括两个非标准信号,以支持与SDIO接口相关的新功能。这包括以下信号:

SDIO_Wake#此信号是从设备(通信模块)到平台的输出,用于触发唤醒主机,并启动设备和平台之间的SDIO接口通信。这个信号是一个开式的漏极输出,需要被平台拉高到1.8V始终打开。

SDIO_RESET#此信号是从该平台对设备的一个输入,它用于重置SDIO接口。模块输入处的信号为1.8V。

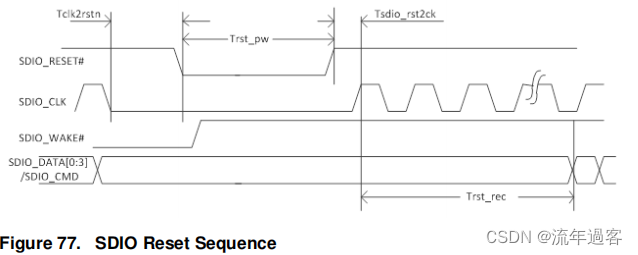

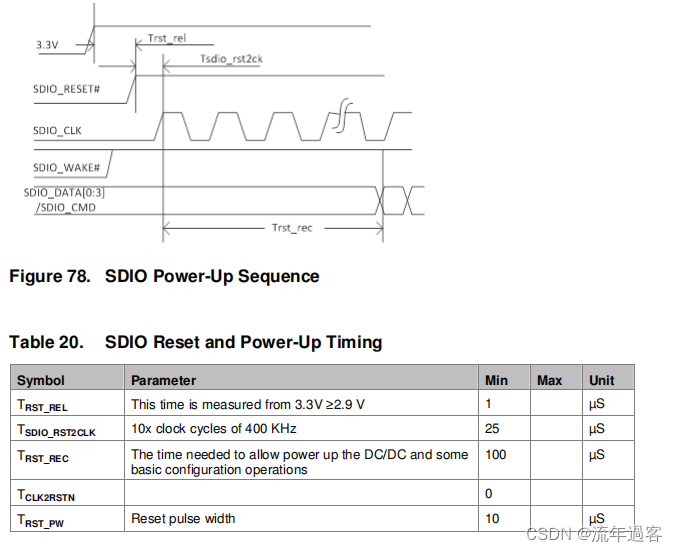

由于SDIO_RESET#和SDIO_WAKE#不是标准SDIO规范的一部分,因此图77和图78中所示的计时图显示了它们预期的计时行为。表20列出了SDIO复位和上电定时参数。

SDIO_WAKE可以在任何给定时间断言,它不受时间约束的约束。然而,从功能的角度来看,预计只有当主机处于睡眠状态且设备需要从主机上获得的服务时:

SDIO_Wake#才会被断言(“0”)。

SDIO_Wake#将被断言,并且在设备中提供断言的源之前不会取消断言。

3.1.8.UART接口

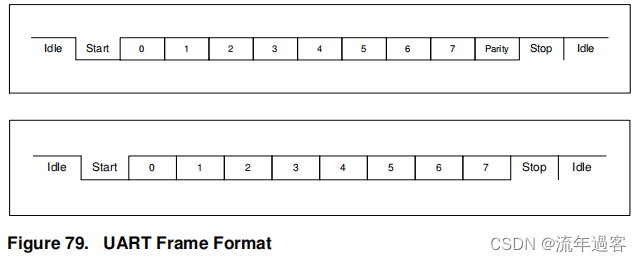

片上异步接口(UART、通用异步接收器和发射器)可用于与其他主机控制器或系统的通信。UART可以处理8位数据帧,并插入一个起始位和一个停止位(有/没有奇偶校验)。UART帧的格式如图79所示。

3.1.8.1.UART唤醒

UART电源管理协议支持以下4线和5线接口:

RDX(输入):接收数据

RTX(输出):传输数据

RTS(输入):发送请求(主机流控制)

CTS(输出):清除发送(设备流控制)

主机唤醒(输出):主机唤醒线是可选的,如果主机支持带唤醒的协议

基于更改传输电源状态之前的三个消息交换和设备和主机之间的握手。双方都可以启动低功率模式或唤醒模式。支持以下信息:

睡眠请求

睡眠请求响应

唤醒:如果主机不支持使用信息进行带内唤醒,则设备应使用带外主机唤醒信号。

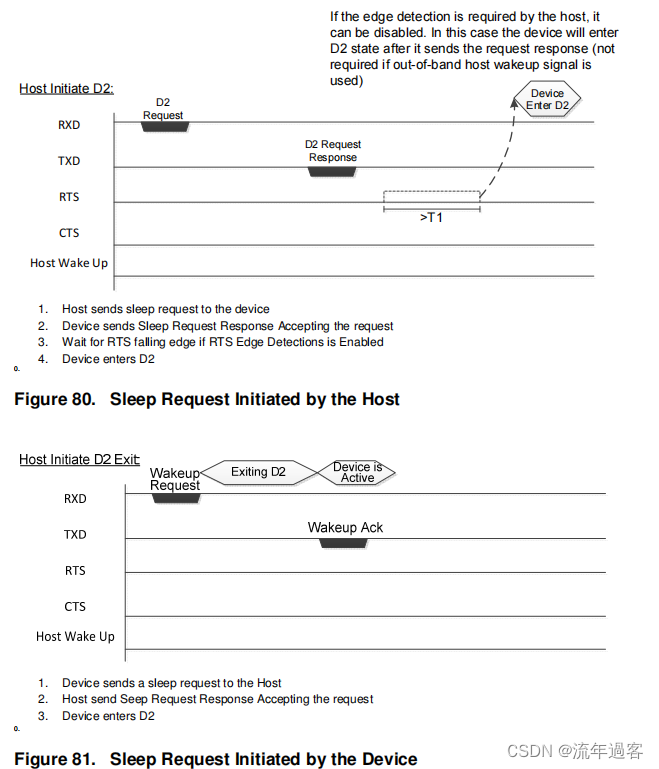

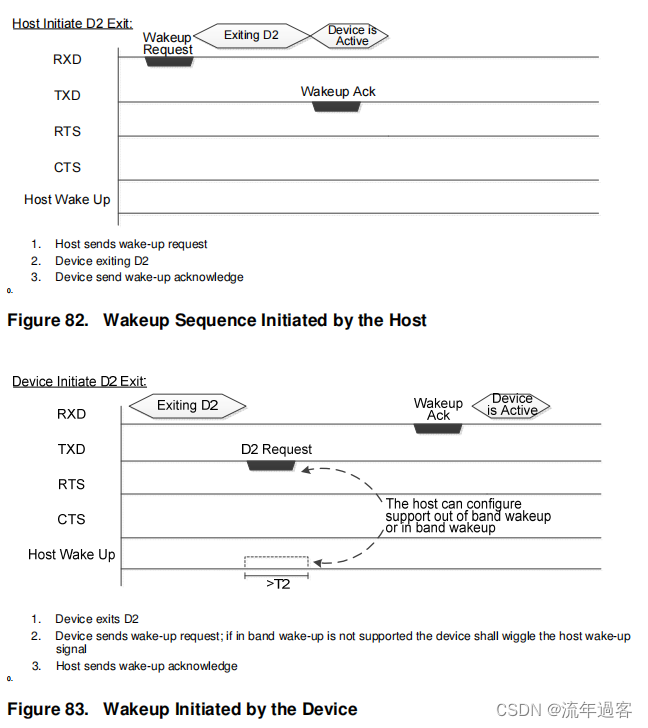

图80到图83描述了功率状态的转换。

3.1.9.PCM/I2S 接口

PCM接口支持以下功能:

(1)四线接口

时钟信号:

PCM_CLK/I2S SCK;输出主,输入从

两帧信号PCM_SYNC/I2S WS:输出主,输入从PCM_CLK/I2S SCK:输出主,输入从

数据在PCM_IN/I2S SD_IN:输入

数据输出信号PCM_OUT/I2S SD_OUT:输出

(2)单双向PCM通道

(3)16-位和24位数据字

(4)各种PCM数据采样率包括。支持8个kHz和16个kHz

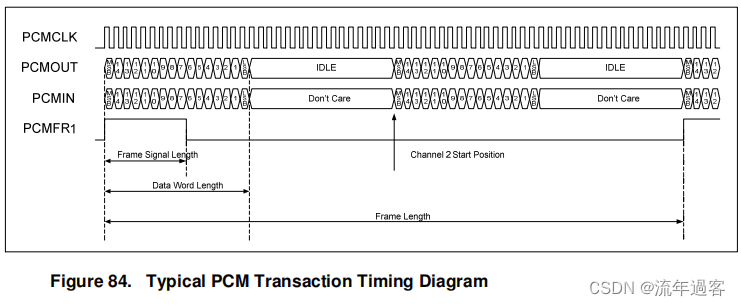

PCM/I2S模式用于标准(窄频)单声道语音或宽带单声道语音。I2S也将用于从主机卸载立体声音频数据(A2DP卸载)。PCM接口由四个信号组成,如图84所示。

时钟信号PCMCLK是PCM接口中其他信号的定时基。在时钟主模式下,蓝牙设备使用分数分法器从内部系统时钟生成PCMCLK。在时钟从属模式下,PCMCLK是对蓝牙设备的输入,并且必须由外部源提供。PCM接口支持一个双向通道。数据在PCMOUT上传输,在PCMIN上接收;总是先使用最重要的位。支持16位线性音频样本和8位A律或µ律压缩音频样本。

3.1.10.I2C接口

3.1.10.1警报#信号

旨在向平台/系统表明I2C设备需要注意。此GPIO可用于建立从设备到主机的特定通信/信令。此信号为活动低。

3.1.10.2.I2C数据信号

I2C数据信号被用来根据I2C协议将数据包从主机发送到设备。该线路支持的速度取决于平台SMBus的速度和设备处理能力。

3.1.10.3.I2C时钟信号

I2C时钟信号提供从主机到设备的时钟信号,以能够解码I2C数据线上的数据。

3.1.11.NFC补充UIM接口

UIM电源输入、电源输出和UIM SWP信号是补充NFC信号,可在UIM设备作为安全元件实现时使用。这些信号没有在插脚中定义,但可以根据OEM供应商之间的协议分配给一些预留插脚。

3.1.11.1.UIM电源输入

在一个M.2卡上有WWAN设备和NFC解决方案在另一个M.2卡上的系统中,WWAN UIM电源应路由到NFC设备所在的M.2卡的UIP电源引脚。该UIM功率信号基本上通过NFC设备传递,并通过下文段落中描述的UIP功率输出信号输出。

3.1.11.2.UIM电源输出

有关UIM_PWR电源的电压和电流容差要求的更多细节,请参阅ISO/IEC 7816-3。请注意,UIM的接地要求可以通过使用任何GND引脚来提供。只有支持UIM卡的PCI Express M.2卡附加卡才能连接到此引脚。如果插件卡具有UIM支持能力,则它必须在ISO/IEC 7816-3中定义的每一类操作条件(例如,电压)的适当电压下支持UIM_PWR电源。UIM_PWR映射到ISO/IEC 7816-2中定义的联系号C1。UIM_PWR映射到ISO/IEC 7816-2中定义的联系号C1。

3.1.11.3.UIM SWP

NFC包括一个使用ETSI TS102.613协议版本v7.8.0,v8.1.0,v9.1.0的SWP主服务器。SWP是一个全双工,自动时钟接口。NFC(S1)使用V-Domain发送,UICC/ SE(S2)使用I-Domain发送,如第8章(物理传输层)中的ETSI TS102.613所述。

3.1.12.通信特定的信号

3.1.12.1暂停时钟

暂停时钟是一个运行在32.768 kHz的慢速时钟信号。它是一个来自RTC平台的缓冲信号。暂停时钟在平台正常和暂停运行模式下可用,在此期间,模块可以根据需要利用该SUSCLK信号作为关键保持激活电路的时钟源。SUSCLK在平台硬关闭模式下不可用,此时,到模块的3.3 V电源也会关闭。SUSCLK的占空比可低至30%或高达70%。精度将高达200 ppm。

3.1.12.2.状态指示器

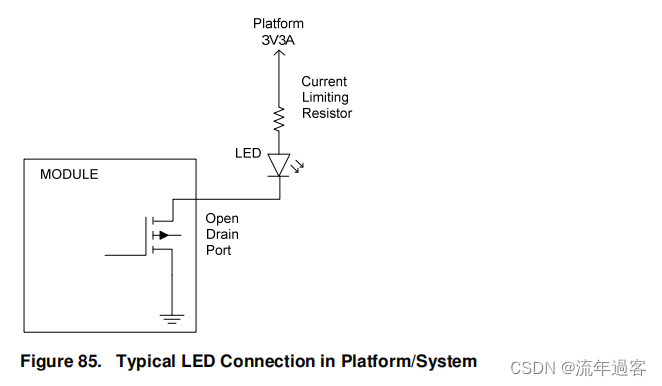

提供两个LED信号,使无线通信插件卡通过系统提供的指示器向用户提供状态指示。LED1#和LED2#输出信号激活低,用于驱动系统安装的LED指示灯。这些信号应能够在最大VOL为400 mV时至少下沉至地面9.0 mA。图85显示了这些led通常如何在使用3.3V的平台/系统中连接的示例。

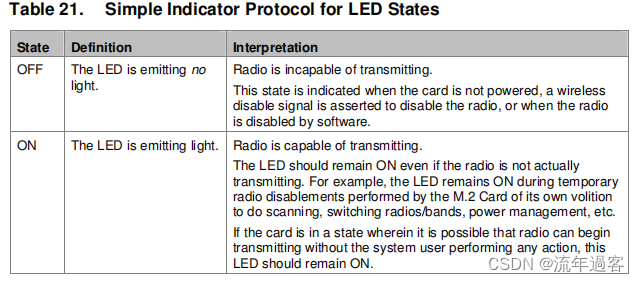

在一个典型的LED连接情况下,电流限制电阻值将在100 Ω范围内,以启用点亮LED所需的9 mA电流。其他平台LED连接,包括其他备用电压源。然而,应谨慎防止在各种电源状态下通过LED针背偏。表21给出了适用于无线无线电操作的两种已定义的LED状态中的每一种的简单指示器协议。尽管指标协议的实际定义是由OEM系统开发人员建立的,但这些解释可能有助于建立跨许多平台的最小通用实现。

允许使用由OEM系统开发人员所定义的更高级的指示器协议。高级功能可能包括使用闪烁或间歇性ON状态,可用于指示无线电操作,如扫描、关联或数据传输活动。此外,使用闪烁状态可能有助于降低LED的功耗。

3.1.12.3.W_DISABLE#信号

W_DISABLE1#和W_DISABLE2#是为无线通信插件卡提供的无线禁用信号。这些信号允许用户通过系统提供的开关禁用附加卡的无线电操作,以满足公共安全法规或当其他需要时。对于实现射频功能的系统和所有附加板卡,都需要实现该信号。提供多个无线禁用信号,以方便管理一个附加卡上的多个无线电。如果系统只实现了一个无线禁用信号,则断言单个信号应用于集体禁用插件卡上的所有无线电。

无线禁用信号是活跃的低信号,当系统声称(驱动低)时,应禁用无线电工作。当实现时,在每个无线禁用信号和+3.3 V之间需要一个上拉电阻,并且应该在100 kΩ到200 kΩ的范围内。每个无线禁用信号的断言和取消断言与任何系统时钟都是异步的。所有由机械开关产生的瞬态现象都需要被系统电路所抑制。当宣布有无线禁用信号时,与该信号相关的所有无线电都应被禁用。当无线禁用信号没有被断言时,如果没有通过软件等其他方式禁用,相关的无线电可以传输。这些信号可以在多个M.2卡之间共享。

在正常操作中,网卡应与无线网络分离,并在确认无线禁用信号后尽快停止任何进一步的操作(发送/接收)。鉴于与无线网络的优雅分离未能及时完成,M.2卡应中断与网络的任何通信,并确保其无线操作在最初断言无线禁用信号后不迟于30秒内停止。一旦禁用过程完成,特定于收音机的LED应向用户指示禁用状态。

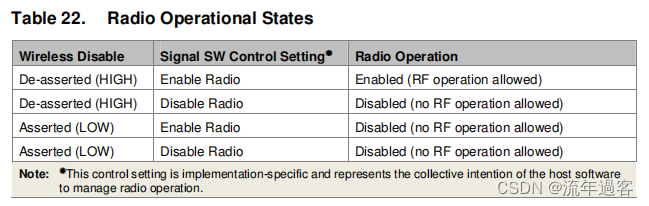

该板卡应在无线禁用信号中断后的非第二秒内启动并向用户指示恢复正常操作的过程。由于可能存在软件禁用状态,因此在恢复正常操作之前,必须先确定软件状态和无线禁用信号断言状态的组合。表22将此要求定义为无线禁用信号和软件控制设置的功能,这样,除非硬件和软件都被设置为启用板卡的射频功能,否则无线电的射频操作仍然被禁用。系统需要在应用电源时,确保每个无线禁用信号处于确定性状态(断言或取消断言);例如,存在+3.3 V。

3.1.12.4.共存信号

COEX1、COEX2和COEX3,以允许在M.2卡上的无线电(s)和其他卡外无线电(s)之间实现无线共存解决方案。这些其他无线电可以位于位于同一主机平台上的另一个M.2卡上,或作为替代无线电实现(例如,使用PCI Express M.2 CEM或专有的外形因素插件解决方案)。这些引脚的功能定义是特定于OEM的,应该在主机平台OEM和板卡供应商之间进行协调。本规范中对这些信号的有序标记是为了在实际的情况下跨主机平台中的多个卡实例建立一致的实现。

3.1.13.保留插脚

预计保留插脚不会终止在插件卡或连接器的系统板侧。这些引脚保留在本规范的未来修订中进行定义。这些引脚的非标准使用可能导致与未来修订一致的解决方案不兼容。在这里添加供应商特定的部分。

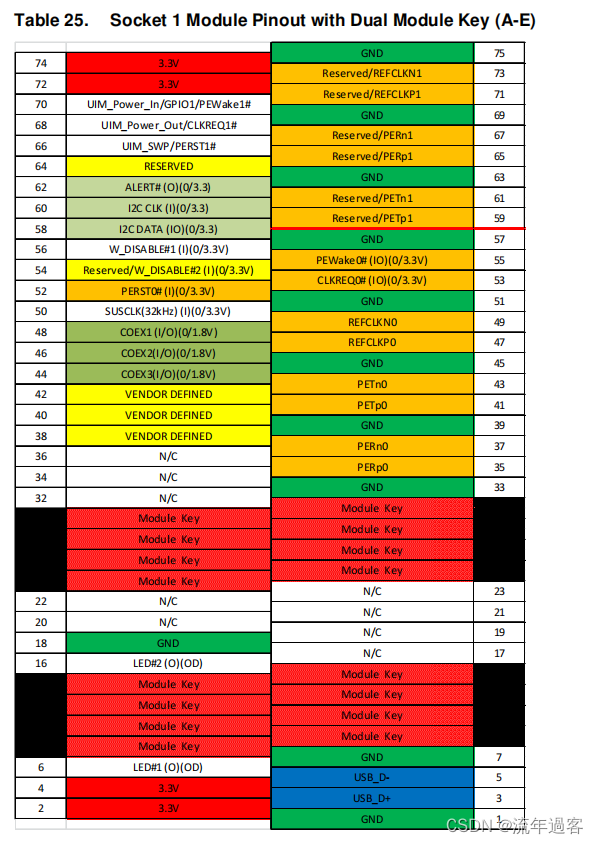

3.1.14.插座1连接器插脚定义

下表说明了模块边缘卡连接器的信号插脚。

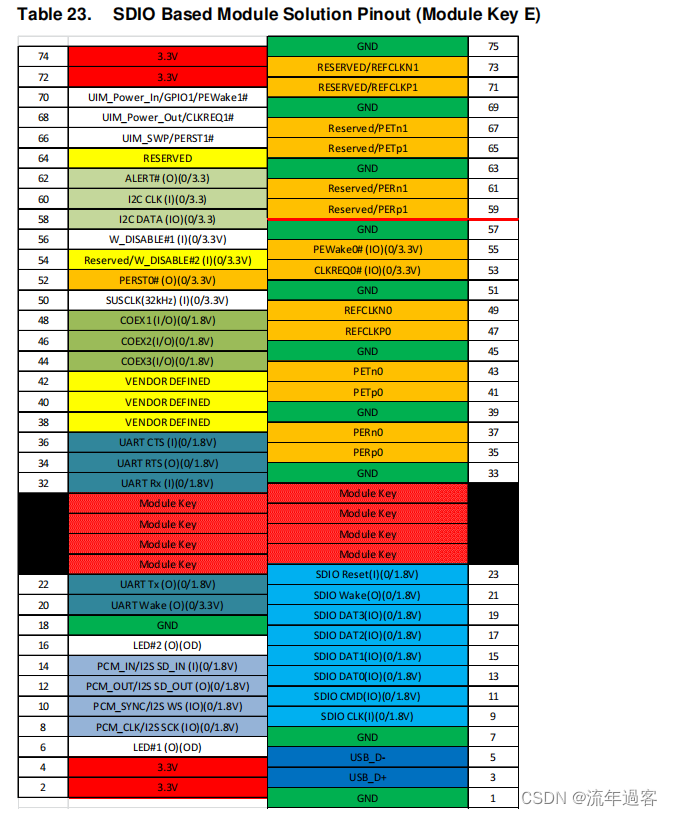

表23列出了基于SDIO的解决方案的输出。

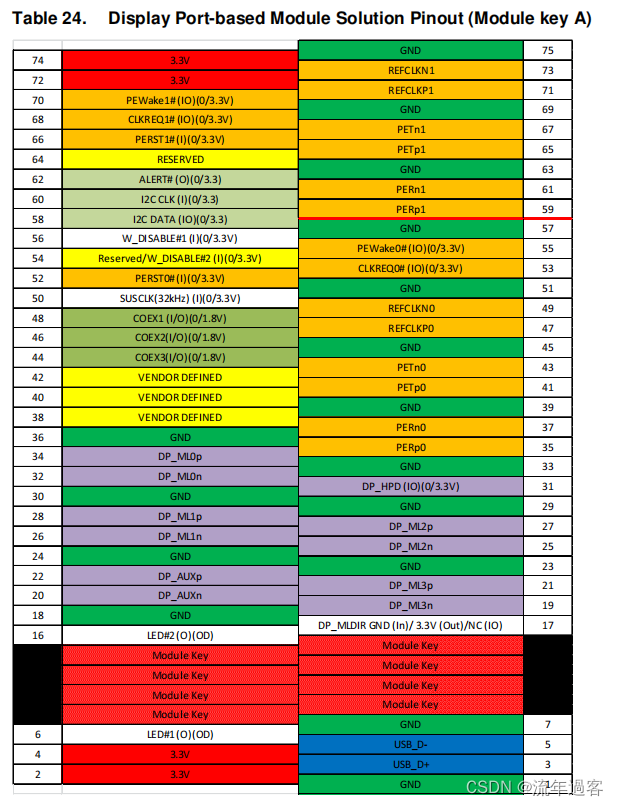

表24列出了基于显示端口的解决方案的输出。

表25列出了使用公共主机接口的基本模块解决方案的插输出,并利用双模块密钥,使其能够插入两种套接字1类型(密钥)。在第3.1.15节,基于插座1的焊接模块引脚图中,还有1216型、2226型和3026型LGA焊接模块的模块引脚图定义。

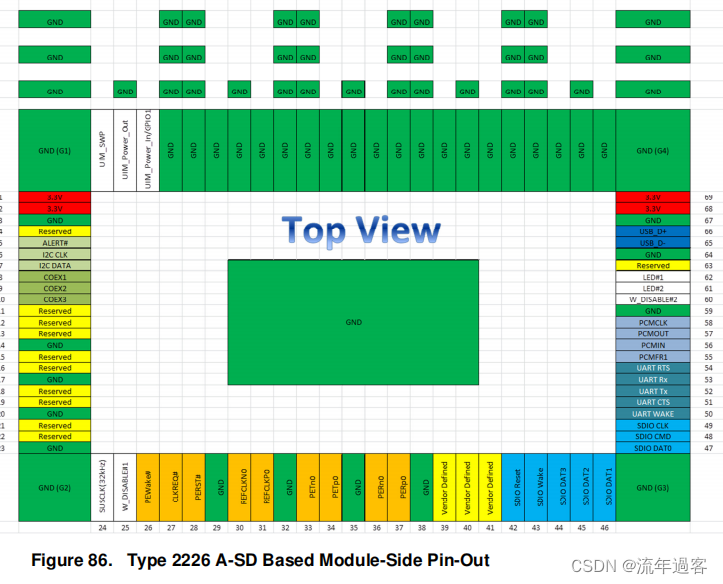

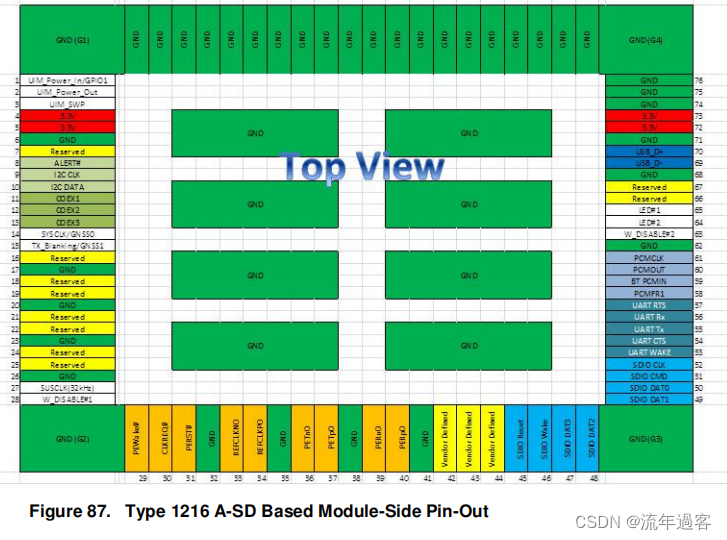

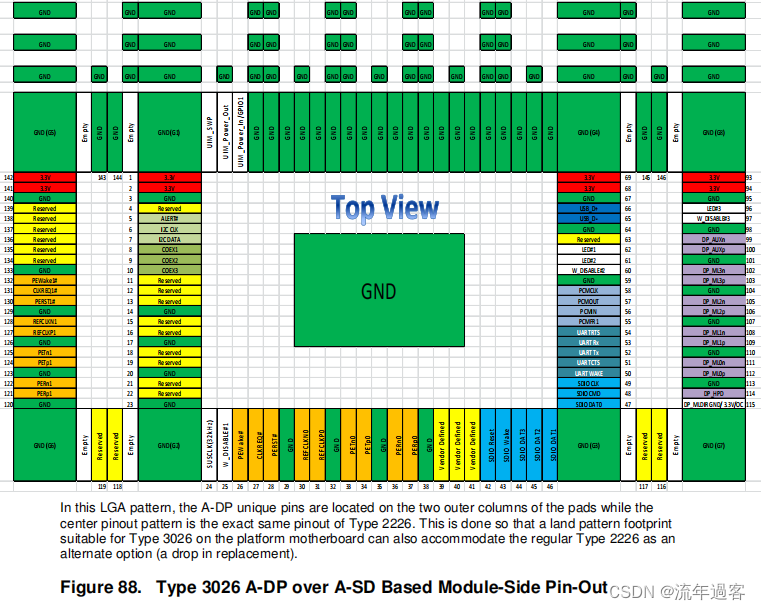

3.1.15.基于插座1的焊接模块引脚输出

本节包含2226型、1216型和3026型LGA焊接模块的模块定位图。

图86显示了基于2226 A-SD的模块侧输出。

图87显示了基于1216 A-SD型的模块侧出

图88显示了3026 A-DP型基于A-SD的模块输出

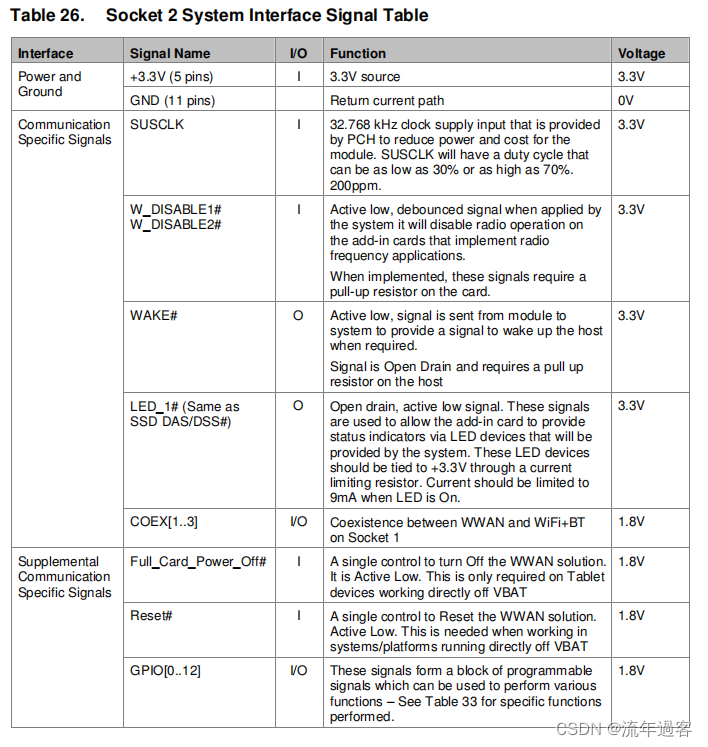

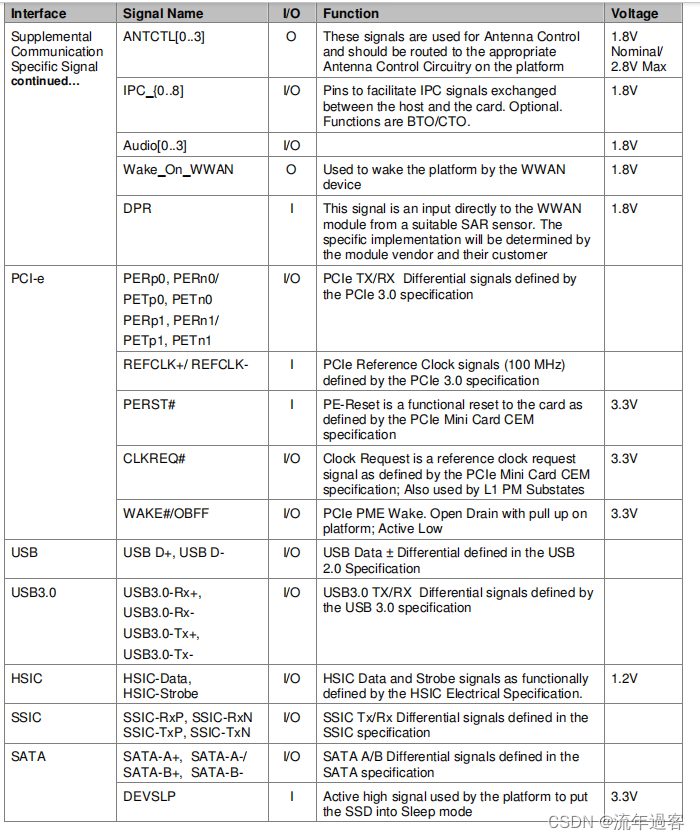

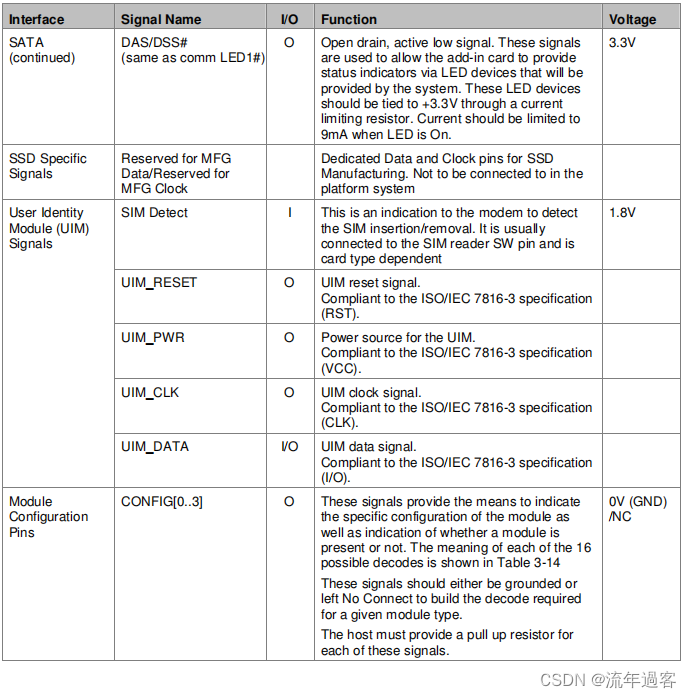

3.2.WWAN/SSD/其他套接字2系统接口

信号套接字2系统接口信号列表见表26

3.2.1.电源和接地

PCI Express M.2插座2使用了一个类似于插座1的单一电源(3.3 V)。电压源(+3.3 V)预计在系统的备用/暂停状态期间可用,以支持通信卡上的唤醒事件处理。在插座2中,有5个3.3 V引脚,可以在需要时提供更高的连续电流。一些较高频率的信号需要与周围的信号进行额外的隔离,使用交织接地(GND)引脚的概念,分离连接器内的信号。这些引脚应视为普通地脚,在卡设计中立即连接到地平面。

3.2.2.PCI快速接口

Socket 2中支持的PCI快速接口是一个双Lane接口,专门用于WWAN、SSD或其他需要这类主机接口的设备。更多信息见本规范第3.1.3节“PCI快速接口”和3.1.4节“PCI快速辅助信号”。

3.2.3.USB接口

详情请参见第3.1.5节,USB接口。

3.2.4.HSIC接口

高速芯片间USB(HSIC)是一种低功耗的芯片互连,100%主机驱动兼容传统USB电缆连接拓扑。HSIC是一个2信号(频闪器,数据)串行接口,它只支持USB高速480 Mbps的数据速率。HSIC可以通过连接接口使用,考虑到HSIC标准确定的电气限制:

数据/频闪迹长度(TL)< 10 cm

数据/频闪迹传播歪斜(TS)< 15 ps

HSIC规范的当前版本可在: http://www.usb.org/developers/docs/获得

3.2.5.SSIC接口

超高速USB芯片间接口(SSIC)是一个芯片到芯片的互连接口,定义为对USB 3.0规范的补充。SSIC增强了USB 3.0,因为互连的物理层是基于MIPI®联盟的M-PHYSM,而不是传统的超高速USB的外部电缆能力的PHY。该方法更好地优化了适用于嵌入式芯片间接口的功率、成本和EMI鲁棒性。所有高层方面(软件、事务协议等)的SSIC遵循USB 3.0规范。SSIC-USB3.0规范的芯片间补充,截至2012年5月3日修订1.0;可从http://www.usb.org/developers/docs/获得,并位于USB 3.0规范下载包内。

3.2.6.USB3.0接口

USB3.0规范定义了所有的电气特性、枚举、协议和管理特性,以支持USB3.0(超速)。超速差分传输线(SSTX+,SSTX-)需要实现一个USB 3.0超高速接口的传输路径。这些引脚应连接到系统中的发射器差速器对和模块上的接收器差速器对。同样,需要高速差分接收线(SSRX+,SSRX-)来实现USB 3.0高速接口的接收路径。这些引脚应连接到系统中的接收器差速器对和模块上的发射器差速器对。当前版本的USB 3.0高速规格可在http://www.usb.org/developers/docs/:。也请参考关于USB3.0的SSIC接口。

3.2.7.SATA接口

SATA是一个高速串行ATA数据链路接口(指定Phy、硬盘和固态传输和应用层)。

3.2.8.用户身份模块(UIM)接口

UIM接口信号定义在系统连接器上,以提供可移动UIM、用户身份模块(SIM)的扩展和驻留在M.2附加卡上的无线广域网(WWAN)无线设备之间的接口。UIM包含WWAN设备在无线广域网无线电环境中操作所需的参数。支持离卡UIM接口的M.2插件卡的UIM信号。

3.2.8.1.UIM_PWR

关于UIM_PWR电源的电压和电流容差要求的更多细节,请参见ISO/IEC 7816-3。请注意,UIM的接地要求可以通过使用任何GND引脚来提供。只有支持UIM卡的M.2外插件卡才能连接到此引脚。如果插件卡具有UIM支持能力,那么它必须在ISO/IEC 7816-3中定义的每一类操作条件(例如电压)的适当电压下支持UIM_PWR电源。UIM_PWR映射到ISO/IEC 7816-2中定义的联系号C1。

3.2.8.2.UIM_RESET

UIM_RESET信号向UIM卡提供复位信号。有关UIM_RESET信号的功能和公差要求的更多细节,请参考ISO/IEC 7816-3。只有支持UIM卡的M.2插件卡应连接到此引脚。UIM_RESET映射到ISO/IEC 7816-2中定义的联系号C2。

3.2.8.3.UIM_CLK

此信号向UIM卡提供时钟信号。有关UIM_CLK信号的功能和公差要求的更多细节,请参考ISO/IEC 7816-3。只有支持UIM卡的M.2外插件卡才能连接到此引脚。UIM_CLK映射到ISO/IEC 7816-2中定义的联系号C3。

3.2.8.4.UIM_DATA

此信号用作串行数据的输出(UIM接收模式)或输入(UIM传输模式)。有关UIM_DATA信号的功能和公差要求的更多细节,请参考ISO/IEC 7816-3。只有支持UIM卡的M.2外插件卡才能连接到此引脚。UIM_DATA映射到ISO/IEC 7816-2中定义的联系号C7。通信特定的信号。

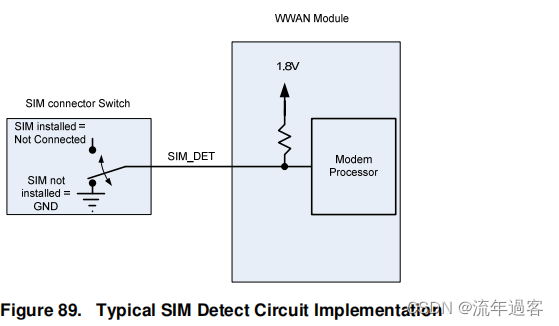

3.2.8.5.SIM_DET

此信号用于检测SIM插座中SIM设备的插入和拆卸。使用普通短SIM卡接头,PUSH-PUSH类型,当没有插入SIM卡时,检测开关通常对地短路。当插入SIM卡时,SIM_DETECT将从逻辑0状态转换到逻辑1状态。上升边表示插入SIM卡。当SIM卡被拔出时,SIM_DETECT将从逻辑1转换为逻辑0。这个下降边将表示拔出SIM卡。监控该信号的M.2模块将把上升/下降边缘或实际逻辑状态视为中断,当触发时,模块将相应地行动。这将需要对连接在其1.8 V电源轨道上的模块进行弱上拉。在图89中可以看到一个典型实现的示例。

3.2.9.通信特定的信号

3.2.9.1。暂停时钟

见第3.1.12.1节,暂停时钟对SUSCLK信号的更详细的描述。

3.2.9.2.状态指示灯

有关LED1#信号的更详细描述,请参见状态指示灯第3.1.12.2节。

3.2.9.3.W_DISABLE#信号

见3.1.12.3节的描述,W_DISABLE#信号的W_Disable1#和W_Disable2#信号。

3.2.9.4.共存信号

请见第3.1.12.4节,共存信号,以获得对COEX信号的更详细的描述。

3.2.10.补充通信特定信号

3.2.10.1全卡电源关闭

全卡电源关闭信号是一个主动低输入,在断言高(≥1.7V)时,模块打开,在断言低(≤0.2V)或三状态时,强制模块关闭。FULL_CARD_POWER_OFF#大头针需要内部拉低与一个弱下拉电阻的>20Kohms。模块设计必须确保此引脚的操作与任何其他接口操作异步。输入必须是3.3V容受的,但可以由1.8V或3.3V GPIO驱动。模块供应商将定义此信号的主机端实现,包括时序图、操作顺序等。这都是特定于实现的。

3.2.10.1.1.通电/断电顺序的示例

下面是一个全卡电源开/关序列的例子:

1.调制解调器电源打开:高水平将触发调制解调器电源打开顺序。

2.调制解调器断电:调制解调器首先通过AT命令断电,然后在主机和调制解调器之间进行握手。 3.FULL_CARD_POWER_OFF#大头针将转到低水平或三种状态来关闭调制解调器的PMU。

3.2.10.1.2.平板电脑电源开关顺序的示例

以下示例序列仅供说明性目的,因为模块供应商可以提供替代的解决方案和要求。

1.电池始终连接到调制解调器上。

2.主机在FULL_CARD_POWER_OFF#销

3.上触发GPIO到高。调制解调器将打开。

4.主机发出AT命令以关闭调制解调器。

5.调制解调器和主机

6.之间的握手。主机在FULL_CARD_POWER_OFF#引脚上将GPIO设置为低(或三态),这将关闭调制解调器PMU适当的关机握手过程。

7.PC主机发送到+CFUN=0到调制解调器

8.调制解调器响应OK。

调制解调器将在发送OK之前完成必要的关机任务:

a)从蜂窝网络正确分离。

b) SW清理功能,保存必要的NVM参数等。

c)激活SIM/EBU关闭序列。

d)上述任务可能需要几毫秒到几秒,这取决于调制解调器的状态。

9.调制解调器在完成基本任务后向AP发送OK。

10.如果AP收到错误,它应该对AT+CFUN=0重试。

11.调制解调器完成PMU断电序列/寄存器访问。以下过程需要不到1秒钟:

a)禁用所有调节器(VPMU和VRTC LDOs除外)。

b)断言复位信号。

c)释放26 MHz的系统时钟请求信号。

12.AP在固定延迟一秒后切断电源或开关引脚低/三状态。在极少数情况下,如果AP在发出+CFUN=0后的_*_秒内没有收到任何响应,AP将假设它是可以的。可能有时,USB可能被过度加载,当它准备发送OK时,驱动程序关闭将已经启动,OK可能无法到达AP。

*注:响应时间将由主机决定。

3.2.10.1.3.极薄的笔记本电脑的电源开关顺序的例子

非常薄的笔记本不使用FULL_CARD_POWER_OFF#信号。以下是非常薄的笔记本电脑的电源开关顺序:

1.调制解调器电源打开时,调制解调器为3.3V。

2.调制解调器打开,因为FULL_CARD_POWER_OFF#引脚被主机拉得很高(引脚6连接到1.8V或3.3V)。

3.主机发出AT命令以关闭调制解调器。

4.调制解调器和主机之间的握手。当握手完成后,主机将切断对调制解调器的供应。

3.2.10.2.重置

异步重置引脚,激活值过低。当此引脚激活时,调制解调器将立即置于通电复位状态。除非出现关键故障,并且与WWAN子系统恢复控制和/或通信的所有其他方法都失败,否则应注意不要激活此引脚。

注意:触发重位#信号将导致调制解调器中所有数据丢失,删除系统驱动程序。它还将断开调制解调器与网络的连接,从而导致呼叫中断。

3.2.10.3.通用输入输出引脚

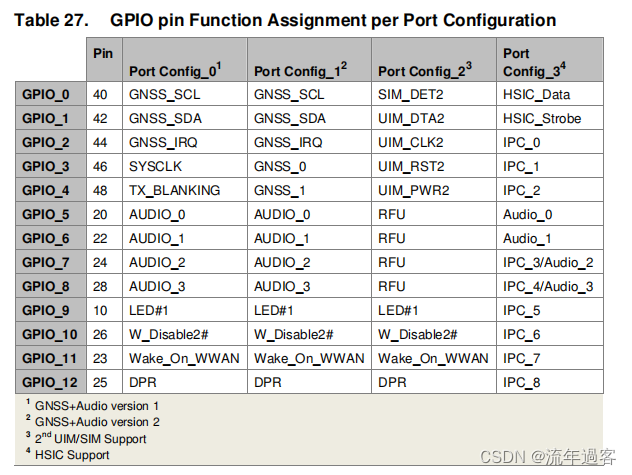

GPIO0-12引脚具有可配置的分配。有四种可能的功能针形配置。这四种配置分别被称为端口配置0-3。在每个端口配置中,每个GPIO都被定义为一个特定的功能销。表27列出了GPIO引脚分配。

3.2.10.3.1.GNSS信号

GNSS_SCL

输入时钟的I2C接口,用于传输位置数据。外部设备为总线主机。当主机CPU处于低功耗模式时,用作位置数据的低功耗接口。

GNSS_SDA

针对I2C的双向数据接口。用于从外部设备(如传感器中心)传输位置数据。

GNSS_IRQ

中断信号-双向,从外部设备(如传感器集线器)按需提供GNSS数据。目标是在主机CPU处于低功耗模式时,为位置数据提供一个低功耗接口。

SYSCLK

由模块生成的一种时钟,用于提供一种将模块上的内部WWAN子系统与外部GNSS设备同步的方法。与Tx_Blanking信号一起使用。操作的频率(和时钟类型)将取决于所使用的具体实现。这超出了本标准的范围,必须被确定为BTO特性。

TX_BLANKING

该信号被激活高,当WWAN子系统进行活动时,该活动将淹没外部设备接收的GNSS信号。该信号与SY_CLK信号特定的操作一起使用,将取决于所使用的具体实现。这超出了本标准的范围,必须被确定为BTO特性。

GNSS0.1

这些是为专有的GNSS功能而保留的引脚,它将在供应商特定的基础上成为BTO的一部分。

3.2.10.3.2.音频信号

音频0-3

这些针脚是保留为音频使用。然而,具体的实现是由模块供应商及其客户具体决定的BTO选项的一部分。支持此功能是可选的。

3.2.10.3.3.第二个UIM信号

UIM接口

支持双SIM操作-该接口包括以下信号;

SIM_DET2#、UIM_DAT2、UIM_CLK2、UIM_RST2、UIM_PWR2

支持双SIM操作是可选的-但是这些引脚不能用于此配置矩阵中的替代功能。对于具体的引脚定义,请参见第3.2.7节

RFU-保留以供将来使用

这些引脚尚未作为本标准的一部分进行分配,但将根据需要进行分配。这些引脚不能用于此配置矩阵中的任何功能,此时应避免并视为无连接。

3.2.10.3.4.IPC[0…8]信号

这些引脚可用于主机和板卡之间的处理器间通信。分配给引脚的信号为BTO/CTO。

3.2.10.3.5.DPR信号

可选的DPR(动态功率降低)信号用于无线设备,以协助满足射频暴露的调节SAR(特定吸收率)要求。该信号由主机系统接近传感器提供给该无线设备,以提供导致无线电发射输出功率降低的输入触发器。

断电的所需值将在不同的主机系统之间有所不同,并由主机平台OEM和卡供应商来决定,以及具体的实现细节。DPR的断言和取消断言对任何系统时钟都是异步的。所有由接近传感器产生的瞬态现象都需要被系统电路所阻挡。

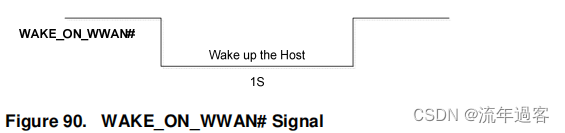

3.2.10.3.6.WAKE_ON_WWAN信号

WAKE_ON_WWAN#信号用于唤醒主机。它是开放式的排水沟,应在主机侧向上拉出。当WWAN需要唤醒主机时,它将输出一秒钟的低脉冲,如图90所示。

3.2.10.4.天线控制

天线支架(0-3),以便实现天线调谐解决方案。所需的天线控制线路数量将取决于应用程序和天线/频带要求。天线控制引脚的功能定义是OEM特有的,应在主机平台OEM和卡供应商之间进行协调。本规范中对这些信号的有序标记旨在帮助跨主机平台中的多个板卡实例建立一致的实现.

3.2.11.SSD特定的信号

3.2.11.1DEVSLP DEVSLP

(设备休眠)大头针用于通知SSD应进入较低功率状态。

3.2.11.2.DAS/DSS#

DAS(驱动器活动信号)由SSD驱动,以指示正在进行访问。有关LED信号引脚的信息,请参见第3.1.12.2节,状态指示器。

3.2.11.3.为MFG时钟和数据

有两个模块引脚专用作为SSD制造引脚。它们的目的取决于供应商的实现。这些引脚必须在主板上没有连接。在平台/系统侧,这些引脚应保持不连接。

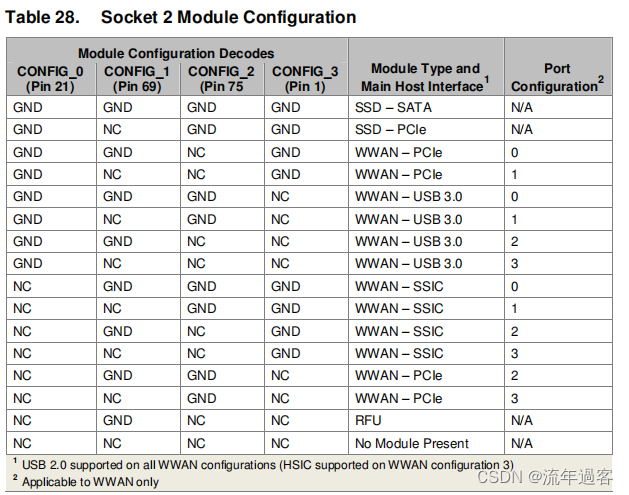

3.2.12.配置引脚

套接字2包含四个配置引脚,可以帮助平台识别插卡和识别卡类型,主机I/F,在WWAN的情况下,GPIO0-7接口引脚的端口配置。此配置接口的操作如下:

引脚CONFIG_0…3这些插脚在插入插座2时,根据主机设备的所需配置接地或留在模块上。所有配置引脚都应由主机平台读取和解码,以识别如表28中所示的指示模块配置和支持的主机接口。

在平台侧,每个CONFIG_0…3信号都需要安装一个上拉电阻器。根据模块上的配置引脚的状态,被绑定到GND或左不连接(NC),被感知到的引脚将创建一个需要解码的4位逻辑状态。

此配置方案将确保始终可以检测到一个模块和它的配置

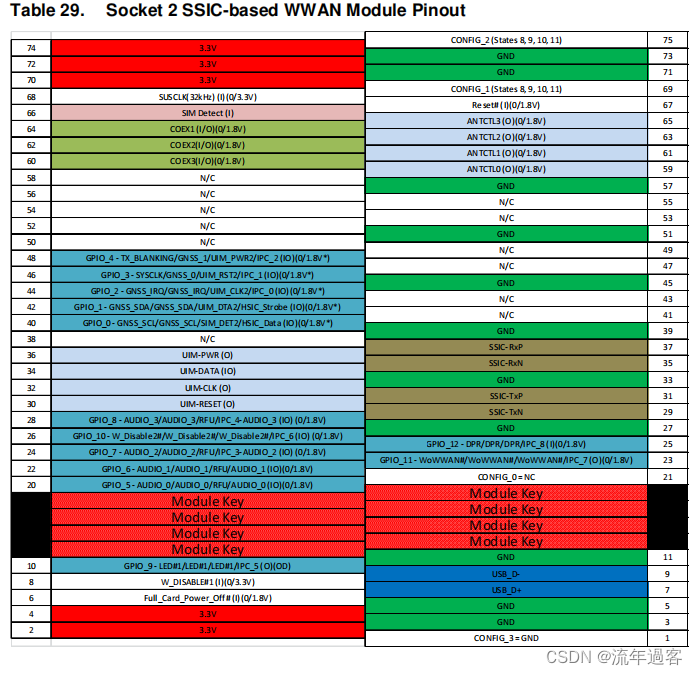

3.2.12.1.插座2接头输入输出定义

下表列出了模块边缘卡接头的信号输出输出。

表29,基于SSIC的WWAN解决方案

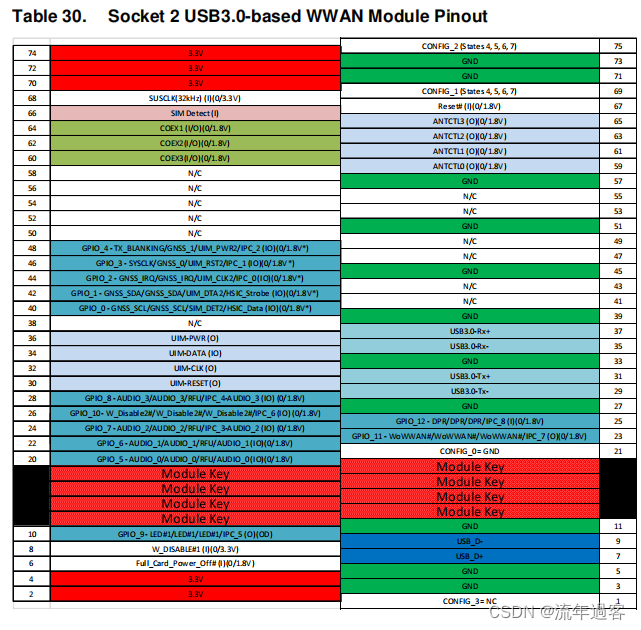

表30,基于USB3.0的WWAN解决方案

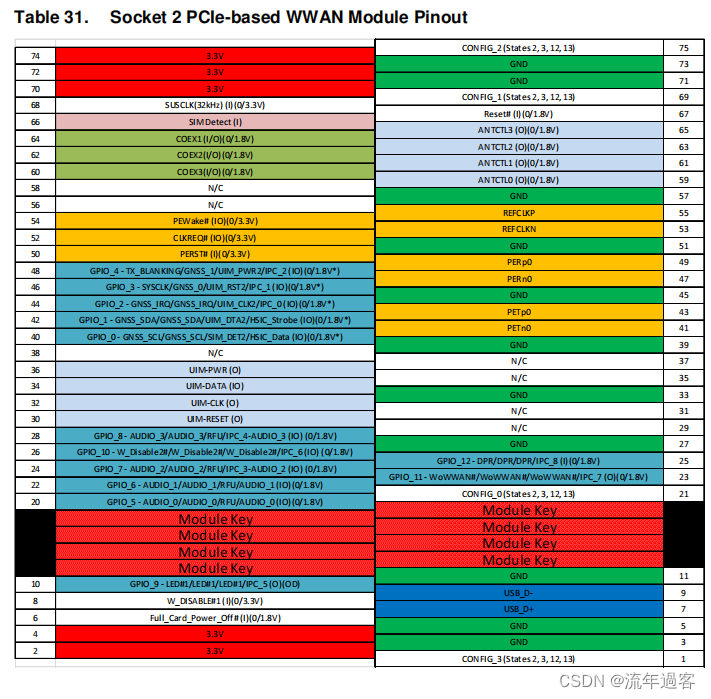

表31,基于PCIe的WWAN解决方案

所有这三种WWAN解决方案都支持传统的USB2.0-based WWAN解决方案或选择性的HSIC

用于识别所需插出和端口配置的模块上的套接字2配置位列表见表28。本节还包含以下表包含信号输出:

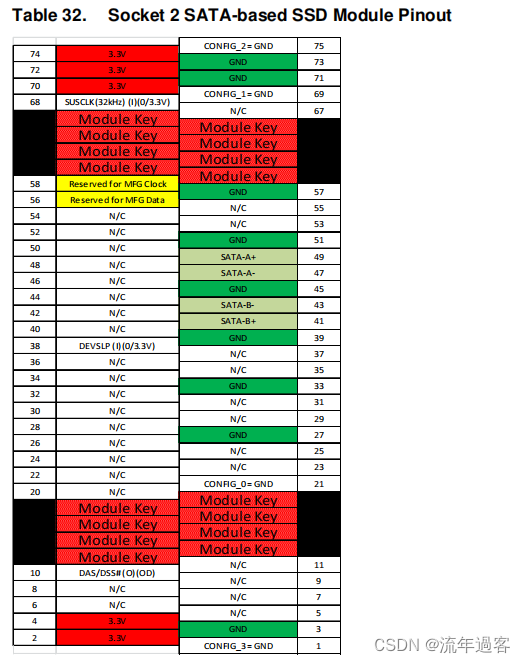

表32,基于SATA的SSD解决方案

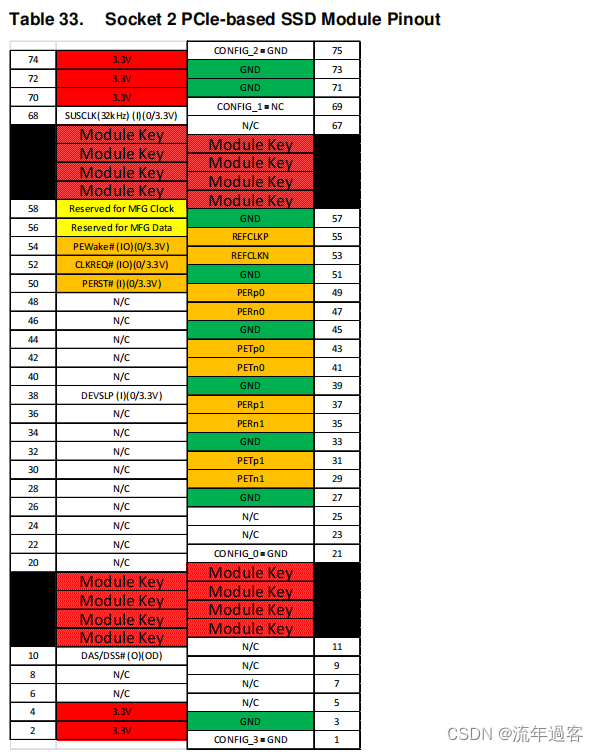

表33,PCIe多车道SSD解决方案

这两个表利用双模块关键方案,使这些解决方案也插到插座3连接器如果可用的平台。这些针形针钉中的CONFIG_1引脚相当于套接字3中使用的PEDET信号。

3.3.SSD插槽3系统接口信号

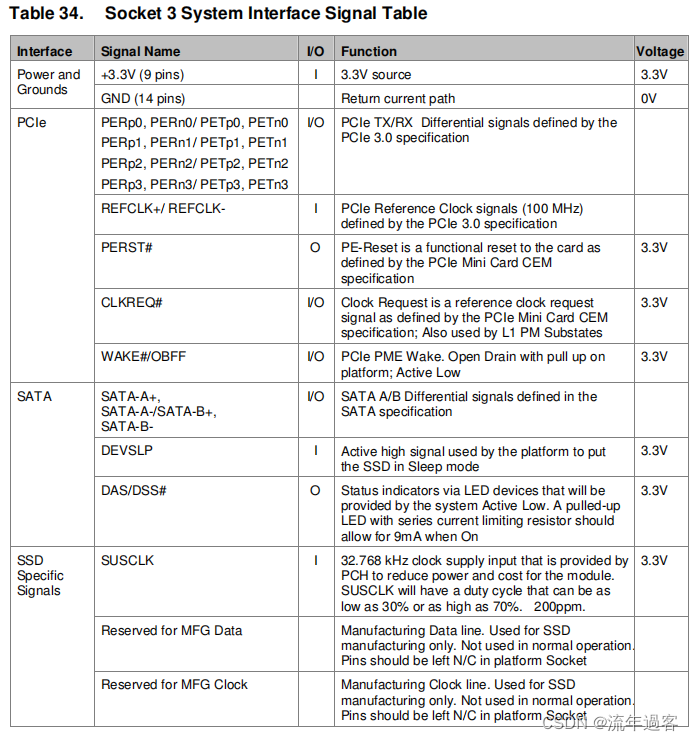

表34包含了一个关于Socket 3系统接口信号的列表

3.3.1.电源和地

PCI Express M.2插座3使用了一个单一的3.3 v电源,类似于插座1和2。电压源,+3.3V,预计在系统的备用/暂停状态期间可用,以支持通信卡上的唤醒事件处理。在插座3中,有9个3.3 V引脚以实现高连续电流,如果需要,与2插座相同。更多的引脚将有助于进一步减少连接器上的红外线下降。一些较高频率的信号需要与周围的信号进行额外的隔离,使用交织接地(GND)引脚的概念,分离连接器内的信号。这些引脚应视为普通地脚,在卡设计中立即连接到地平面。

3.3.2.PCIE接口

Socket 3支持的PCI Express接口是一个四车道PCI Express接口,专门用于需要这种主机接口的高级SSD设备。Socket 3还可以支持仅使用两通道PCI Express的SSD设备,并且能够通过双模块键插入Socket 2。关于PCIe信号的详细描述,请见本规范中的第3.1.3节。

3.3.3.SATA接口

SATA是一个高速串行ATA数据链路接口(指定Phy、硬盘和固态传输和应用层)。

3.3.4.SSD特定信号

3.3.4.1SUSCLK

关于SUSCLK(挂钟)信号的详细描述,请参见本规范中的第3.1.12.1节。

3.3.4.2.PEDET

接口检测可由主机使用来确定M.2卡使用的通信协议;SATA信令(低)或PCIe信令(高)。

3.3.4.3.DEVSLP

DEVSLP(设备休眠)大头针用于通知SSD应进入低功率状态。

3.3.4.4.DAS/DSS#

DAS(驱动器活动信号)由SSD驱动,以指示正在进行访问。有关LED信号引脚的信息,请参见第3.1.12.2节。

3.3.4.5.MFG时钟和数据

有两个模块针,专用作为SSD制造针。它们的目的取决于供应商的实现。这些引脚必须在主板上没有连接。

3.3.4.6.插座3连接器信号输出定义

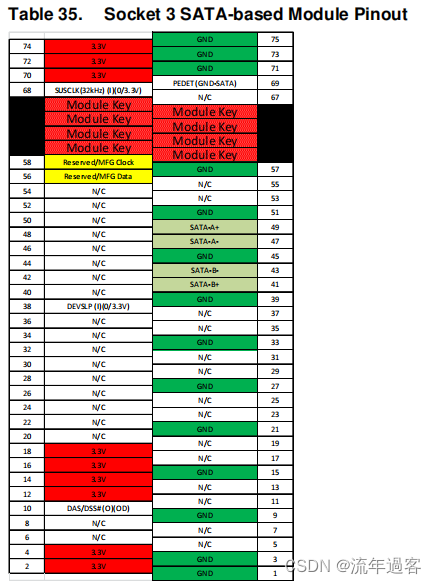

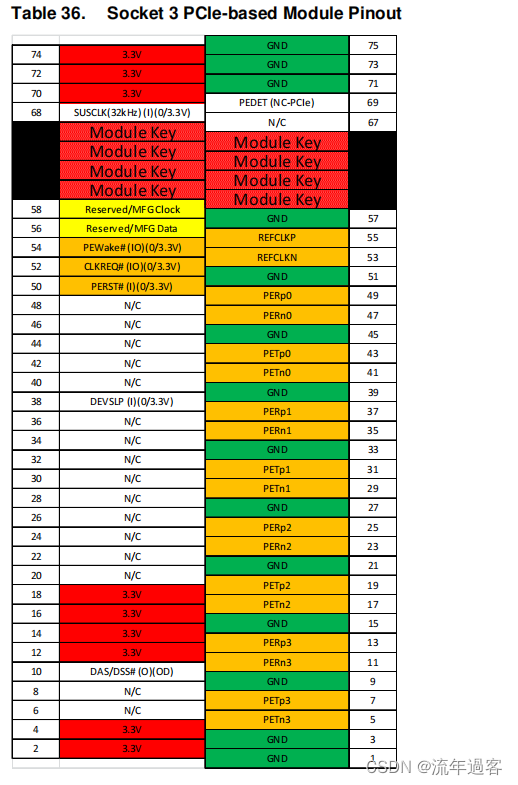

表35和表36列出了模块边缘卡连接器的信号信号输出。表35列出了基于SATA的解决方案。表36列出了基于PCIe多车道的解决方案。

1088

1088

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?