default语句的对case语句综合的影响

之前看书都说case语句不加default会产生不必要的latch,浪费资源,有时候还会产生错误的时序。然后我写了点简单的程序测试一下,加不加default到底会对电路产生怎样的影响。

时序电路

加default

input clk;

input [2:0] sel;

output [3:0] out;

reg [3:0] out;

always@(posedge clk) begin

case(sel)

3'b000: out <= 4'd1;

3'b001: out <= 4'd2;

3'b010: out <= 4'd3;

3'b011: out <= 4'd4;

3'b100: out <= 4'd5;

default: out <= 4'd1;

endcase

end

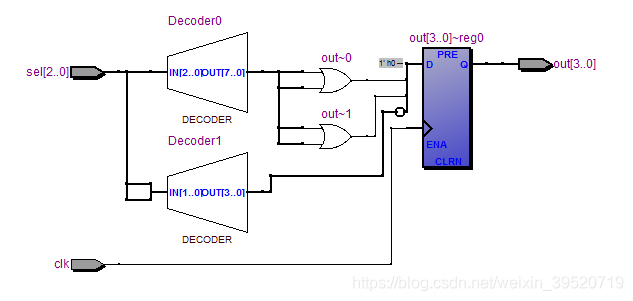

产生的RTL电路为

不加default

由于这里case语句分支没有覆盖所有可能情况,但是在时序电路中没有生成latch,而是生成了一些额外的同步电路(三个数据选择器和D触发器)来保持out值不变

组合电路

加default

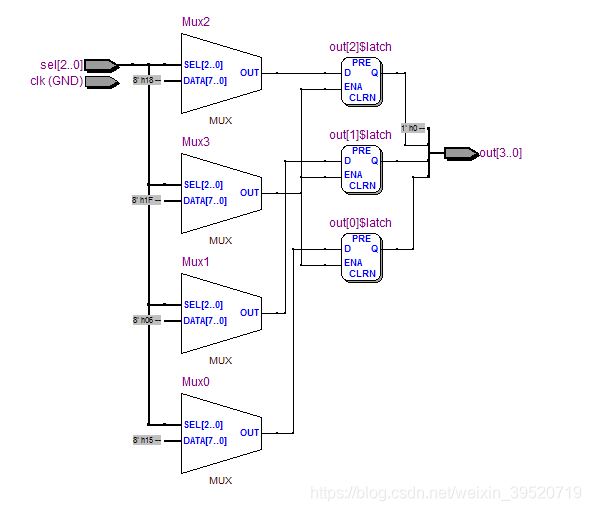

不加default

额外生成了三个latch,并且使用一个数据选择器来使能控制这些latch。

但是有时候在时序电路中,故意不加default或者加 default: out <= out; 来生成保持电路。

探讨了在Verilog中,default语句对case语句综合的影响,特别是在时序和组合电路中,加与不加default如何改变电路结构,包括latch的生成与否,以及对资源利用和时序准确性的影响。

探讨了在Verilog中,default语句对case语句综合的影响,特别是在时序和组合电路中,加与不加default如何改变电路结构,包括latch的生成与否,以及对资源利用和时序准确性的影响。

7712

7712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?