1)实验平台:正点原子达芬奇FPGA开发板

2) 摘自【正点原子】达芬奇之Microblaze 开发指南

3)购买链接:https://detail.tmall.com/item.htm?id=624335496505

4)全套实验源码+手册+视频下载地址:http://www.openedv.com/docs/boards/fpga/zdyz_dafenqi.html

5) 正点原子官方B站:https://space.bilibili.com/394620890

6)对正点原子FPGA感兴趣的同学可以加群讨论:876744900

在前面的实验中,都是不带DDR的系统结构,本次实验将学习带DDR的MicroBlaze系统搭建过程。

点击“Open Block Design”,在Diagram窗口中进行硬件设计。

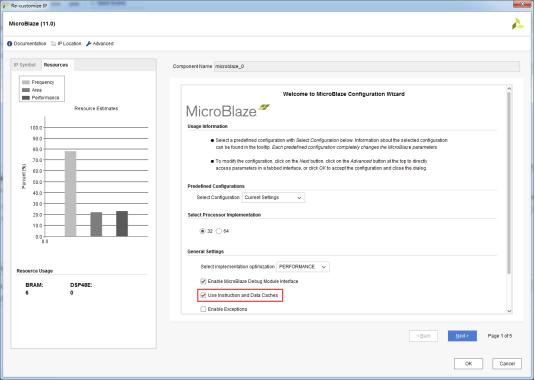

首先打开MicroBlaze IP核,点击该IP进行配置,这里启用存储于指令优化选项,如图 9.3.11所示:

图 9.3.11 MicroBlaze设置

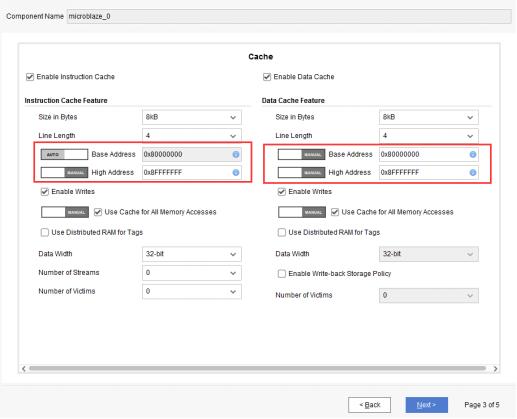

继续点击“Next”至第3页Cache页,将地址设置如图 9.3.12所示:

图 9.3.12 地址设置

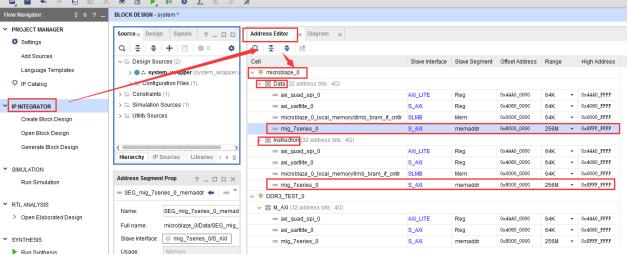

上处地址值必须与IP INITRATOR->Adress Editor->microblaze_0->的mig_7series_0数据和指令的地址值保持一致,如图 9.3.13所示:

图 9.3.13 MicroBlaze地址设置参考值

MicroBlaze IP核设置完毕。

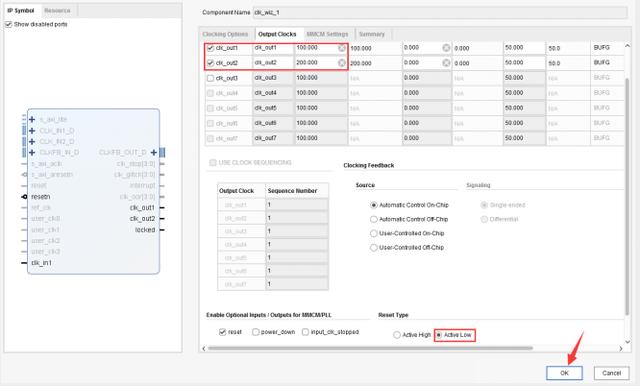

双击Clocking Wizard时钟IP核,在Output Clocks页面,选中clk_out1和clk_out2,时钟频率分别设置为100和200,复位设为低电平,如图 9.3.14所示:

图 9.3.14 设置输出时钟

clk_out1是给microblaze_0、uart、spi等模块提供时钟;clk_out2给mig_7series_0模块提供时钟。

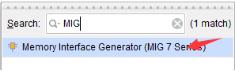

接着添加MIG(Memory Interface Generalor) IP核,点击“+”按钮,输入“MIG”,双击Memory Interface Generator,添加IP核,如图 9.3.15所示:

图 9.3.15 添加MIG IP核

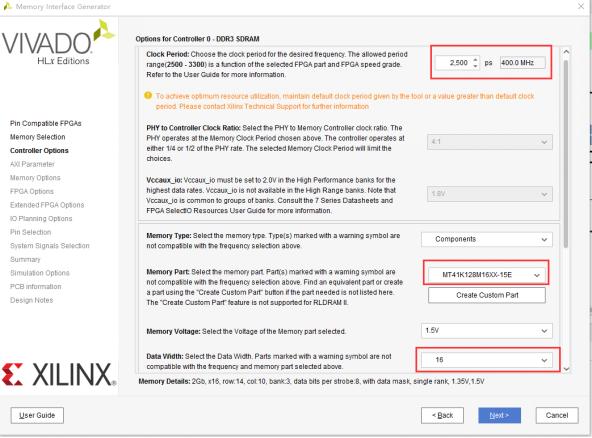

双击添加的MIG IP,进入配置页面,我们在达芬奇开发板FPGA设计部分,已经对MIG的配置操作有过详细讲解,这里我们简略说明一下配置需主要的配置步骤。

在Controller Options目录,DDR芯片的运行时钟设为“400M”,DDR3芯片型号选择“MT41K128M16XX-15E”,数据位宽这里设为“16”。如图 9.3.16所示:

图 9.3.16 时钟及物理芯片配置

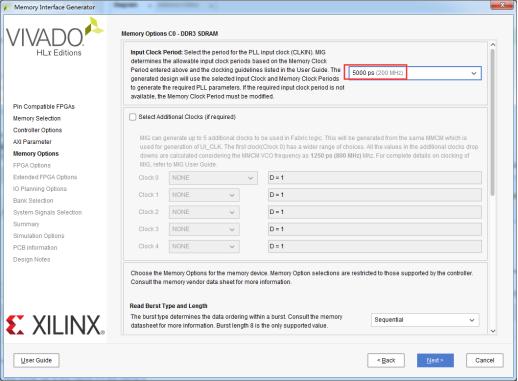

在Memory Options目录, Input Clock Period我们选择“200M”。如图 9.3.17所示:

图 9.3.17 储存器配置

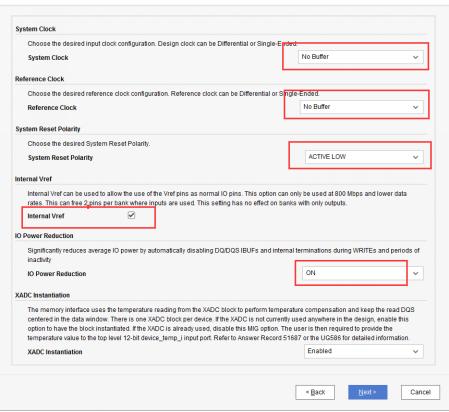

在FPGA Options目录,按照图 9.3.18所示进行配置。

图 9.3.18 系统时钟配置

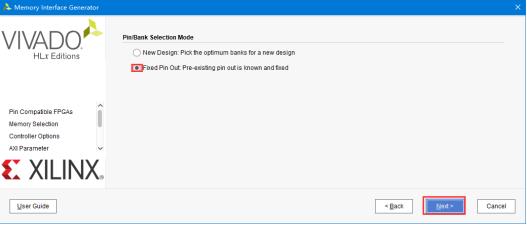

“Pin/Bank Selection Mode”我们选择第二项,后面我们会使用.xdc文件。

图 9.3.19 Pin/Bank Selection Mode选项卡

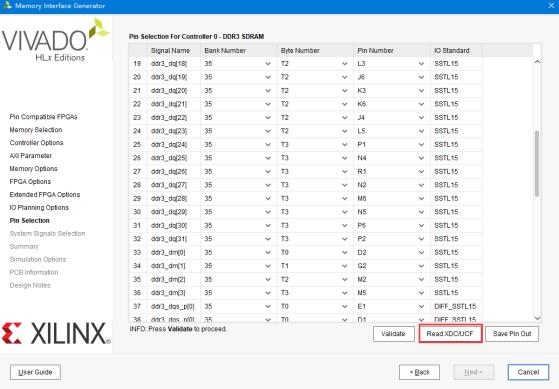

在Pin Selection目录我们选择第二个选项“Read XDC/UCF”直接导入管脚分配文件,如图 9.3.20所示。

图 9.3.20 管脚分配导入选项卡

如下图所示,在工程目录下,我们已经为大家准备好了一个ddr3_rw_test.xdc文件,用户只要直接导入这个.xdc文件就可以完成ddr3的管脚分配。ddr3_rw_test.xdc文件的路径为G:/tis_pro/axi4_ddr_rw。

导入后我们点击“Validate”,此时会跳出对话框,表明已经验证通过,我们点击“OK”,此时“Next”变成可选,点击“Next”完成管脚分配。如图 9.3.21所示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4701

4701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?