欢迎FPGA工程师加入官方微信技术群

点击蓝字关注我们FPGA之家-中国最好最大的FPGA纯工程师社群

第二篇以德州仪器(TI)的高速ADC芯片——ads52j90为例,介绍完了4线SPI配置时序。本篇将以该芯片SPI结构为例,具体介绍如何利用verilog 实现4线SPI配置时序。

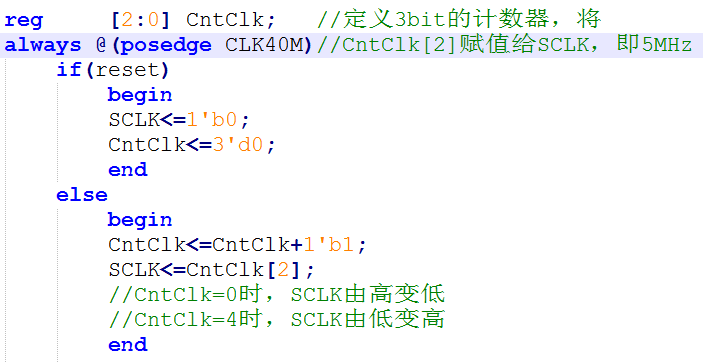

无论实现读还是写功能,都先要提供SCLK。假如FPGA系统工作时钟40MHz,我们可以利用计数器产生一个n分频的时钟作为SCLK,本例中n取8,SCLK频率5MHz。SCLK产生的代码如下:

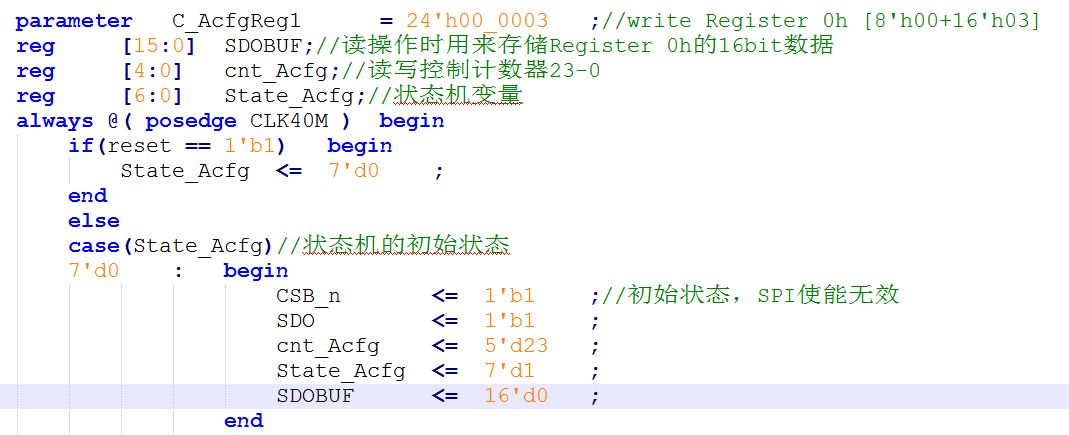

SCLK时钟有了,接下来我们建立一个状态机实现读和写功能:

初始化状态的下一个状态就是写寄存器操作了ÿ

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3258

3258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?