半导体器件

CMOS的特点

CMOS-Complementary Metal-Oxide-Semiconductor

- 静态功耗低

- 逻辑摆幅大

- 抗干扰能力强

- 可在较广泛的电源电压范围内工作

- 速度快

- 在模拟电路中性能比NMOS好

- 集成度比NMOS稍低

- 自锁效应,影响电路正常工作

多晶硅作为栅极的优点:

- 可通过掺杂不同极性及浓度的杂质改变功函数(阈值电压)

→金属变更栅极阈值需要更换材料,改变工艺

2.Si-SiO2界面缺陷少

→金属-绝缘体界面缺陷较多

3.多晶硅熔点比大多数金属高,在高温下沉积栅极材料增进器件性能

多晶硅作为栅极的缺点:

1.导电性不如金属,限制信号传输速度

→金属硅化物 Silicide

钨/钛/钴/镍

Salicide工艺:Self-Aligned Silicide 自我对准金属硅化物

2.多晶硅耗尽

→多晶硅的完全合金化

FUSI-Fully Silicide Polysilicon Gate

→金属栅极

钽/钨/氮化钽/氮化钛+铝/钨

器件持续缩小带来的影响

问题:

源极与漏极距离缩短,沟道除了受栅极影响,还受漏极电场影响

压阈值漏电 Sub Threshold Leakage

短沟道效应 Short-Channel Effects

影响:

1.影响开关速度&效率

2.功耗,集成,可靠性

解决方向:

1.新材料

High-K电介质,金属栅极(HKMG-High K Metal Gate),隐埋应变硅源漏

2.新结构

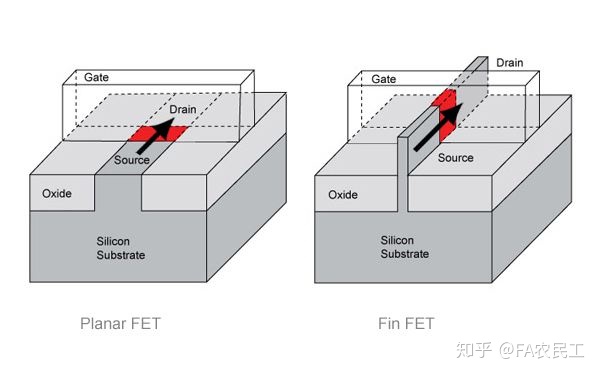

鳍式场效应晶体管 FinFET

1.平面型晶体管只能从沟道一侧控制器件的导通与关闭

栅电极从Finfet鳍形硅两侧及顶部控制

2.缩小了有源区在平面上的占地面积

3.增加了沟道的有效宽度

栅极对沟道电势控制更加完美

高静电完整性

增加器件电流驱动能力&器件抑制短沟道效应的能力

增加器件跨导,减少漏极感应势垒降低(DIBL)&阈值电压随沟道长度的变化量

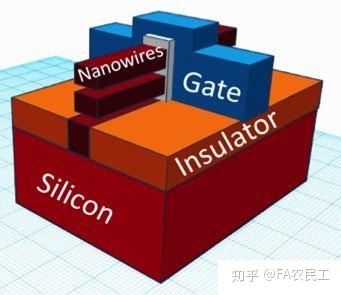

GAAR 全包围栅器件

Gate-All-Around Recentangular

栅极将鳍形沟道全部包裹起来

沟道多为长方形,锐角效应使矩形沟道截面中电场仍不均匀

GAAC 圆柱体全包围栅器件

Gate-All-Around Cylindrical

克服了锐角效应,改善了器件对端沟道效应的控制

1.多晶硅耗尽

2.隐埋应变硅源漏

3.费米能级

5050

5050

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?