本次分享华为公司的《大规模逻辑设计指导书》中的“同步电路设计技术及规则”的部分内容,为“同步电路设计“的最后一部分内容。

4 SET和RESET信号处理

在设计时应尽量保证有一全局复位信号 ,或保证触发器, 计数器在使用前已经正确清零和状态机处于确知的状态。 寄存器的清除和置位信号 ,对竞争条件和冒险也非常敏感。在设计时, 应尽量直接从器件的专用引脚驱动 。另外, 要考虑到有些器件上电时, 触发器处于一种不确定的状态, 系统设计时应加入全局复位/Reset ,这样主复位引脚就可以给设计中的每一个触发器馈送清除或置位信号 ,保证系统处于一个确定的初始状态 。需要注意的一点是 ,不要对寄存器的置位和清除端同时施加不同信号产生的控制, 因为如果出现两个信号同时有效的意外情况 ,会使寄存器进入不定状态。 对于状态机设计 ,由于有可能存在一些状态对于系统而言是 “非法的” (或称 “无关的”),所以除了在状态机设计时充分考虑各种可能出现的状态以及一旦进入 “非法” 状态后可以强迫状态机在下一个时钟周期内进入 “合法” 状态 (一般时初始状态) 外, 一定要保证系统初始化时状态机就处于 “合法” 的初始状态。这里最好的办法仍然是使用全局主复位信号强迫状态机进入已知的 “合法” 状态。5 时延电路处理

时延电路是指在可编程器件的设计中, 为了能够满足电路之间时序配合的要求 ,利用可编程器件的内部资源而进行时序调整 ,如 ,利用线延时或者若干串联 Buffer 电路, 使时钟或数据滞后一段时间。典型的, 该时间即不能太长, 又不能太短 以便满足 “特定” 需要。

然而, 这种时延电路严重依赖器件工艺 ,也依赖每次的布线结果, 给设计带来许多麻烦, 有时会引起严重后果 。因此 ,必须正确处理时延电路。

5.1 在设计中应尽量避免时延电路

绝大多数时延电路是由设计者在设计之初考虑不完善造成的。例如,在设计中没必要地存在多个时钟电路, 模块划分不合理 ,关键电路关键时序考虑不周等。

我们的设计经常是在功能模块划分完成之后 ,就急急忙忙去做具体电路 ,许多关键时序并没有考虑清楚 ,这不可避免的造成设计多次反复, 正确的做法是:

设计目标分析 ---> 功能模块划分 --->确定关键电路时序和模块间接口时序 --->具体电路设计设计电路, 尤其是数字电路 最关键的一环是 ,设计各模块间的接口时序, 确定关键电路的时序 ,这个工作必须在具体电路设计之前确定下来。

“时序是事先设计出来的 ,而不是事后测出来的, 更不是凑出来的”。

5.2 若实在无法 ,则尽量采用高频电路

若实在无法 ,则尽量采用高频电路, 对所需信号加触发器进行延时。该延时只跟时钟频率和触发器个数有关, 而与工艺基本无关。

6 全局信号的处理方法

全局信号处理的原则是 :时钟信号 ,异步清零 ,置位信号上不允许存在毛刺 。不允许异步清零, 置位信号同时有效。

在下述几种情况下 ,时钟信号, 异步清零, 置位信号上可能会有毛刺:

6.1 时钟信号 ,异步清零, 置位信号为组合逻辑输出

由于组合逻辑是电平敏感的, 比较容易产生毛刺, 而组和逻辑的细小毛刺一旦经过时序电路则其对电路的影响则会放大 。因此在设计中对时钟信号 ,异步清零 ,置位信号这些对时序电路来讲非常重要的信号应尽量采用同步电路, 而对于非用组合逻辑不行的地方则必须用卡诺图严格的分析时序电路, 确定彻底消除竞争与冒险后才可引入到时序电路中使用 ,下面举例说明:

对于必须用组合逻辑的输出作为时钟, 异步清零, 置位信号的电路 ,对其组合电路的输出必须采用卡诺图进行严格的分析, 保证彻底消除了竞争与冒险后才可引入到时序电路中使用。对于时钟信号 ,异步清零 ,置位信号是多个信号中选择的情况可按下述方法同步化。

对组合电路产生的时钟信号的处理

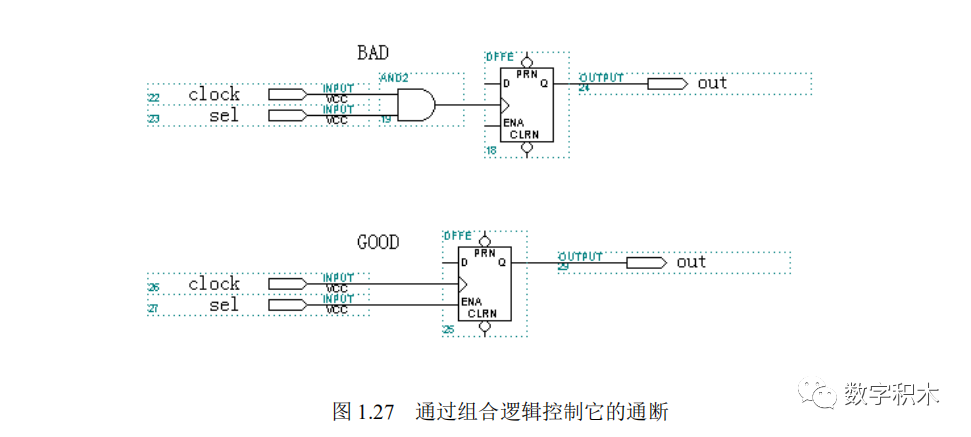

情况1 同一个时钟源 ,通过组合逻辑控制它的通断 ,如下图。

上面的图中, 触发器的时钟是由CLOCK与SEL相与后的输出, 目的是通过控制触发器的时钟的通断达到控制触发器的输出的目的。这种情况下由于CLOCK与SEL不是严格同步的 ,则有可能会在触发器的时钟脚产生毛刺, 而在FPGA中 ,触发器对时钟端的毛刺是敏感的, 上述毛刺可能导致触发器的误动作在下面的图中 。触发器的时钟是CLOCK ,而将SEL信号与触发器的使能端连接 ,这样同样达到了通过SEL信号控制触发器的输出的目的 。但由于CLOCK不会产生毛刺 ,可以保证触发器的可靠触发。

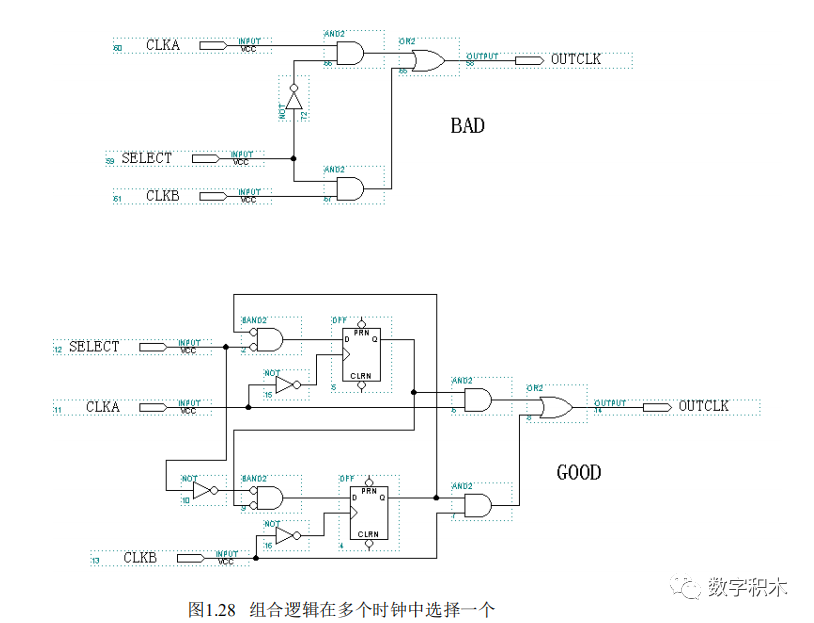

情况2 通过组合逻辑对触发器的时钟在多个时钟中选择一个, 如下图所示。

上图中 ,标为BAD的一个由于直接用组合逻辑实现在CLKA, CLKB两个时钟中二选一的功能 。而组合电路由于不同路径的延迟不同 ,所以在电路的时钟输出很容易产生毛刺, 而标为GOOD 的一个由于对选择信号SELECT分别用两个触发器进行了同步化 ,所以在时钟的输出端不会产生毛刺。

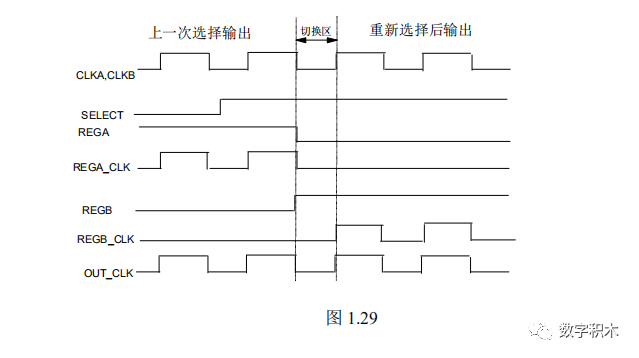

图1.29是图1.28中GOOD电路的原理时序图 ,其中REGA表示接CLKA的触发器, 其对应的与门输出为REGA_CLK, 同样定义REGB和REGB_CLKB ,很显然 ,当REGA或REGB前后有限 “漂移” 时, OUT_CLK是不会出现毛刺得对GOOD电路 。有两个问题 1. SELECT如果在CLK下降沿左右发生变化 该电路能否正常?2. 该电路的触发器能采用上升沿触发吗?

6.2 使用自我清除 ,自我置位和自我钟控的寄存器。

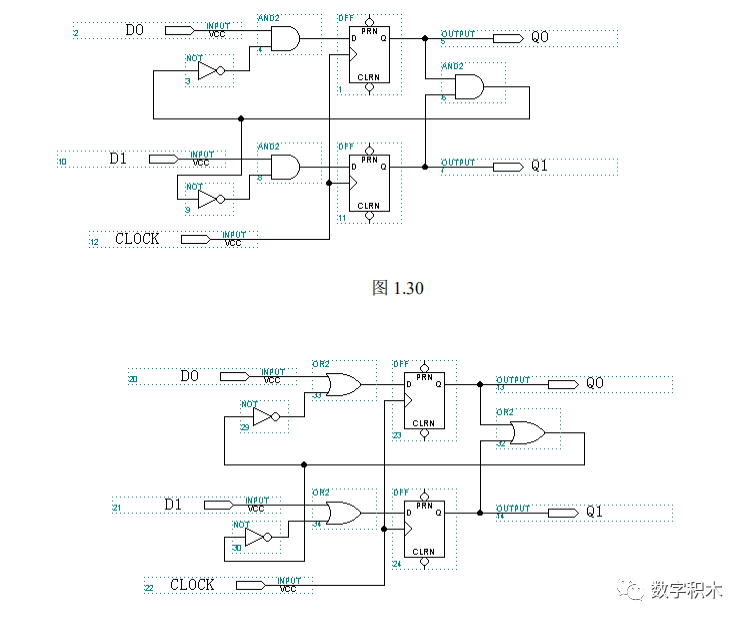

建议尽量使用触发器的使能端来达到钟控的目的。对于自我清除, 自我置位, 最好通过组合逻辑将其转变成对输入端数据的置位与清除 ,从而提高电路的可靠性, 具体说明如下二图。

图1.30是一个自我清除的电路图, 当输出端均为 1 时 ,电路复位, 这样消除了产生毛刺的隐患, 但使输出端体现出复位延迟了一个CLOCK。, 图1.31是一个自我置位的电路图 ,当输出端均为 0 时 ,电路置位, 这样做输出端体现出置 位延迟了一个CLOCK ,但消除了产生毛刺的隐患。

6.3 时钟信号 ,异步清零, 置位信号由外部输入 ,输入时有毛刺。

对于由外部输入的有毛刺的时钟, 异步清零 ,置位信号通常的处理方法是使用内部触发器锁存 ,使之同步化。

7 时序设计的可靠性保障措施

时钟偏差要加以控制。

在同步电路里, 时钟信号要连接到所有的寄存器, 触发器以及锁存器等器件上。这些巨大的负载就象一个大电容加在时钟线上, 再加上时钟线本身的分布电容和电阻 ,这样时钟线就象分布的RC线, 由于RC线的延时是线长的函数 ,这样就使得连到同一根时钟线上的时钟由于距离时钟源的远近不一而产生不同的延时 。因而造成了同一时钟到达各个器件的时间不一致 ,使得各个以时钟为基准器件的动作也不一致 ,而造成时序上的混乱 。这就是同步电路时钟偏差要让同步电路可靠地运行, 就要对时钟偏差进行控制, 以使时钟偏差减小到可用的范围, 影响时钟偏差的主要有以下几个因素。

-

- 用于连接时钟树的连线。

- 时钟树的拓扑结构。

- 时钟的驱动。

- 时钟线的负载。

- 时钟的上升及下降时间。

在通常的FPGA设计中对时钟偏差的控制主要有以下几种方法。

1. 控制时钟信号尽量走可编程器件的全局时钟网络.

在可编程器件中一般都有专门的时钟驱动器及全局时钟网络 ,不同种类, 型号的可编程器件 ,它们中的全局时钟网络数量不同。因此要根据不同的设计需要选择含有合适数量全局时钟网络的可编程器件 ,一般来说 ,走全局时钟网络的时钟信号到各使用端的延时小, 时钟偏差很小 ,基本可以忽略不计。

2. 若设计中时钟信号数量很多 ,无法让所有的信号都走全局时钟网络.

若设计中时钟信号数量很多 ,无法让所有的信号都走全局时钟网络,那么可以通过在设计中加约束的方法,控制不能走全局时钟网络的时钟信号的时钟偏差.

一般而言 ,时钟偏差的控制值应按保持时间要求来计算 T < T1 T_hold 。

注意 Xilinx器件应用中 ,MAXSKEW约束必须直接加在触发器的时钟端上, MAXSKEW约束不能通过任何门电路, 尤其是对芯片PAD进行约束时, 应对IBUF之后的信号加约束 ,许多人在初学时经常忘记这一点。

3. 异步接口时序裕度要足够大。

局部同步电路之间接口都可以看成是异步接口 ,比较典型的是设计中的高低频电路接口I/O接口, 那么接口电路中后一级触发器的建立-保持时间要满足要求 ,时序裕度要足够大。

4. 在系统时钟大于30MHz时, 设计难度有所加大, 建议采用流水线等设计方法。

采用流水线处理方式可以达到提高时序电路的速度 ,但使用的器件资源也成倍增加。

5. 要保证电路设计的理论最高工作频率大于电路的实际工作频率。

最高频率是指设计软件经综合, 布局 ,布线后 ,软件计算出的可工作的最高频率。比如经过综合及布局布线后 ,最长的延时为20ns,则其理论最高工作频率为50MHz。需要指出的是 ,此频率更设计有很大关系, 良好的设计可使器件工作在更高的频率范围。

所谓电路的实际工作频率是指所设计的逻辑电路实际要达到的工作频率 。既实际电路中所使用的时钟频率。

要使时序电路可靠地工作就必须使理论最高工作频率大于电路的实际的工作频率 ,但理论要 ,高于实际的值是多少, 这需要根据实际情况而定 ,主要要考虑的是时钟的最大可能抖动是多少。

往期精彩

【华为】同步电路设计技术及规则(二)

【华为】同步电路设计技术及规则(一)

【华为】可编程ASIC设计方法简介(三)

【华为】可编程ASIC设计方法简介(二)

【华为】可编程ASIC设计方法简介(一) 【华为】verilog语言编写规范(三) 【华为】verilog语言编写规范(二) 【华为】verilog语言编写规范(一) 【华为】Verilog HDL入门教程(5-10章) 【华为】Verilog HDL入门教程(4章) 【华为】Verilog HDL入门教程(3章) 【华为】Verilog HDL入门教程(1-2章) 【华为】FPGA设计设计规范本文完!!! 欢迎关注微信公众号【数字积木】,更精彩的内容等着你!

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?