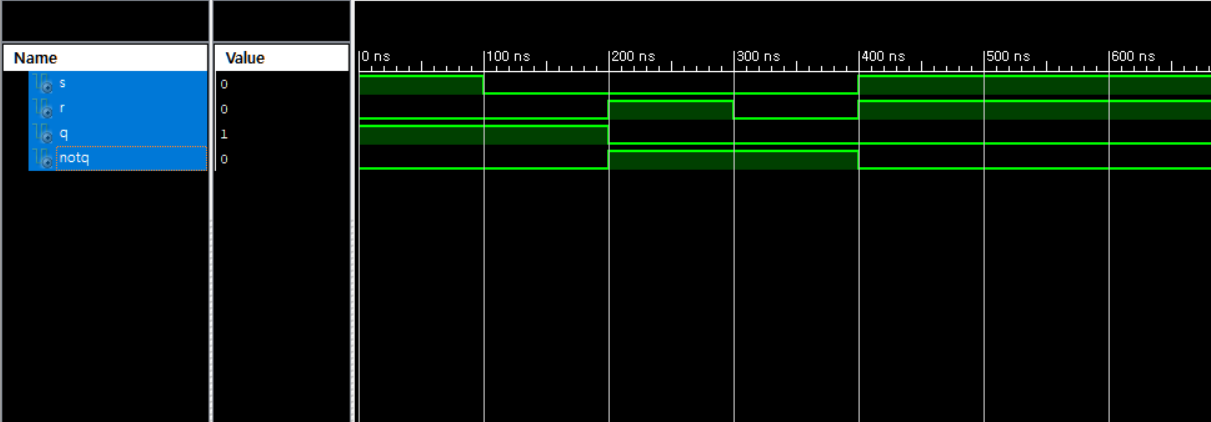

我已经了解到,当S和R在它们在下面的电路VHDL代码中仅为'1'时均为'0'时,SR锁存器会发生振荡。VHDL中的简单SR锁存器仿真(带Xilinx)不会振荡

这里是SRLATCH

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity SRLATCH_VHDL is

port(

S : in STD_LOGIC;

R : in STD_LOGIC;

Q : inout STD_LOGIC;

NOTQ: inout STD_LOGIC);

end SRLATCH_VHDL;

architecture Behavioral of SRLATCH_VHDL is

begin

process(S,R,Q,NOTQ)

begin

Q <= R NOR NOTQ;

NOTQ<= S NOR Q;

end process;

end Behavioral;

的VHDL和以下的测试平台代码的过程,其仿真结果

-- Stimulus process

stim_proc: process

begin

S <= '1'; R <= '0'; WAIT FOR 100NS;

S <= '0'; R <= '0'; WAIT FOR 100NS;

S <= '0'; R <= '1'; WAIT FOR 100NS;

S <= '0'; R <= '0'; WAIT FOR 100NS;

S <= '1'; R <= '1'; WAIT FOR 500NS;

end process;

,完全我没有任何想法,为什么模拟不反映。 ..

(点击放大)

+0

您尚未提供展示振荡的[最小,完整和可验证示例](https://stackoverflow.com/help/mcve),您提供的刺激也不会这样做。治愈的办法是平衡延误,以赢得胜利。这相当于提供了共识。在钟控触发器中,这是设置和保持时间的源泉,也是使用主从触发器的动力。我们正在处理丢失的数字设计艺术以及零门延迟的抽象。 –

+0

如果您要为Q和NOTQ的赋值添加统一的延迟:1ns后的Q <= R NOR NOTQ;在1 ns后NOTQ <= S NOR Q;'并且在同一个增量周期内(不插入WAIT)在S和R上提供'0'到'1'的转换,您可以证明[振荡](https:// i .stack.imgur.com/d23rt.png“srlatch_vhdl_with_delay.png”),而不需要可以显示增量循环或导致超过增量循环的最大数量的波形显示。 –

1189

1189

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?