点击蓝字关注我们

点击蓝字关注我们

大家好,我是奋斗者Y,欢迎来到数字IC自修室。

秋招如火如荼地进行着,今天为大家带来汇顶芯片岗的真题解析,如有错漏,欢迎指正哈。再次感谢亨师弟的鼎力支持。

验证类

1、下面是两种情况下的UVM代码:

第一种情况:

task my_case0::main_phase(uvm_phase phase);

for(int i = 0; i < 10; i++) begin

#10;

`uvm_info("case0", "phase is executed", UVM_LOW)

end

endtask

task my_case0::run_phase(uvm_phase phase);

phase.raise_objection(this);

#100;

phase.drop_objection(this);

endtask

第二种情况:

task my_case0::main_phase(uvm_phase phase);

phase.raise_objection(this);

#100;

phase.drop_objection(this);

endtask

task my_case0::run_phase(uvm_phase phase);

for(int i = 0; i < 10; i++) begin

#10;

`uvm_info("case0", "phase is executed", UVM_LOW)

end

endtask

请问上述两段代码"phase is executed"分别输出了几次?

第一种情况打印信息输出0次,第二种情况打印信息输出10次

解析:

UVM中通过objection机制来控制验证平台的关闭。在进入到某一phase的时候,UVM会收集此phase提起的所有的objection(raise_objection),并且实时监测所有的objection是否已经撤销了(drop_objection),当发现所有的objection都已经撤销后,那么就会关闭此phase,开始进入下一个phase。当所有的phase都执行完毕后,就会调用$finish来把整个的验证平台关掉。如果UVM发现此phase没有提出任何objection,那么将会直接跳转到下一个phase中。

在drop_objection语句之前必须先调用raise_objection语句,raise_objection和drop_objection总是成对出现。rasie_objection语句必须在phase中第一个消耗仿真时间的语句之前。

对于run_phase,与其他动态运行的phase是并行运行的,如果12个动态运行的phase有objection被提起,那么run_phase则不需要raise_objection就可以自动运行。

第一种情况中main_phase没有提起任何objection,不理会操作,直接跳到post_main_phase,时刻还是为0。因此"phase is executed"输出0次

第二种情况中main_phase提起延时100ns的objection,run_phase则开始并行运行其for循环操作,因此"phase is executed"输出10次

2、以下关于验证的描述,正确的是(B)

A.验证平台使用checker检测DUT的行为,只有知道DUT的输入输出信号变化之后,才能根据这些信号变化来判定DUT的行为是否正确

B.SystemVerilog区别于verilog的一个重要特征是其具有面向对象语言的特性:封装、继承和多态

C.UVM是Synopsys、Cadence、Mentor等EDA厂商联合发布的验证平台

D.Verilog,SystemVerilog,SystemC,,UVM都是验证常用的硬件语言

解析:

选项A:验证平台中实现监测DUT行为的组件是monitor。Checker是根据DUT的输出来判断DUT的行为是否与预期相符合,比对数据来源于RM(reference model)和o_agent的monitor。 选项C:VMM由Synopsys于2006年推出,OVM由Cadence和Mentor于2008年推出,UVM(Universal VerificationMethodology)由Accellera推出于2011年推出,得到Synopsys、Cadence、Mentor的支持。 选项D:UVM不是语言,是一个以SystemVerilog类库为主体的验证平台开发框架3、以下关于Venlog的描述,正确的是(无)

A.SystemVerilog是提供给验证使用的,因此其不能被综合

B.SystemVerilog中可以用logic代替Verilog中的wire和reg信号类型

C.Verilog语言中的function语言不可被综合

D.在Verilog中,定义成reg的信号会被综合成触发器

E.Verilog中,如果case的条件不写完整,将会导致综合时出现锁存器(Latch)

解析:

选项A:SystemVerilog可被综合 选项B:SystemVerilog对经典的reg数据类型进行了改进,使得它除了作为一个变量以外,还可以被连续赋值、门单元和模块所驱动。为了与寄存器类型相区别,这种改进的数据类型被称为logic,任何使用线网的地方均可以使用logic,但要求logic不能有多个结构性的驱动,例如在对双向总线建模的时候,需要用wire类型。 选项C:Verilog中的function可被综合 选项D:变量在always使用需要定义成reg,若always中为组合逻辑,则该reg不被综合成触发器 选项E:只有在组合逻辑中的case结构才有可能产生锁存器,而在时序逻辑电路中,即使case结构中的分支不完整,也不会产生锁存器。在时序逻辑中,由于触发器具有锁存数据的功能,所以不会生成锁存器,锁存器只会在组合逻辑电路中产生。 因此,在设计组合逻辑电路时,要注意将 if…else…结构中的else写完整,case结构中一定要加上default语句,这样可以减少综合出锁存器的可能性。设计类

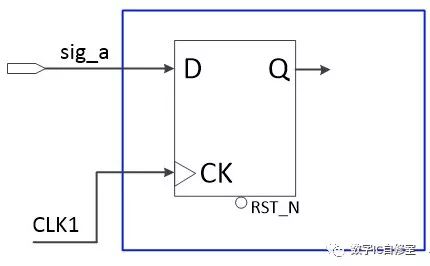

1、如下图所示,当CLK1为100MHz时,约束为set_input_delay -clocks CLK1-max 5 sig_a,如果CLK1变成50MHz,需要保证约束的效果不变,此时input delay应该设置为多少?(A,B,C?)

A. 5ns

B. 10ns

C. 15ns

D. 20ns

解析:

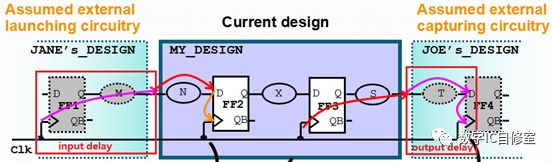

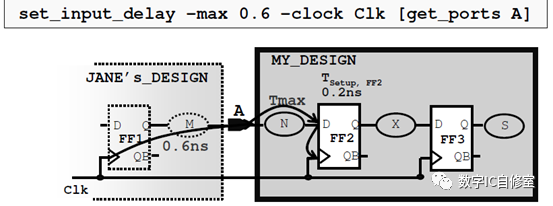

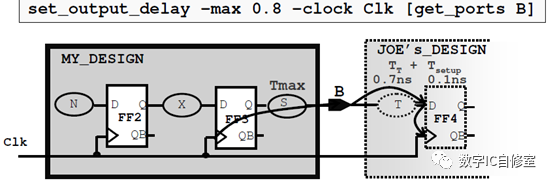

set_input_delay 和set_output_delay是对芯片间的信号延时信息的描述, DC根据这些描述对该芯片进行优化。如下图:

思路一:题目中当CLK1为100MHz,输入端口到D端的margin为10ns-5ns=5ns,

当CLK1为50MHz时,时钟周期增大为20ns,为保证约束效果一致,margin应该保持为5ns,因此input_delay应设置为15ns。

思路二:保持50%时钟的margin,设置为10ns。

思路三:input delay根据外围电路而定,应保持为5ns。所谓的一致应该是timing clean。不管时钟频率多少,input delay都是由外围电路决定。通常外设手册上会给出一个max和一个min的值,分别setup和hold。设max影响setup分析,设min影响hold分析。一个设计,在不同应用场景频率可能会运行在不同的频率上。

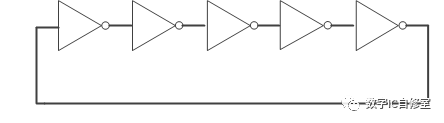

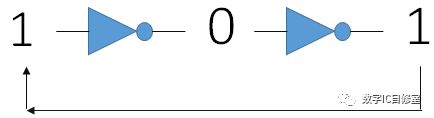

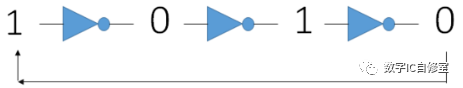

2、上图所示环形振荡器,单个反向器延时为3us,振荡后输出的信号周期为多少?(A)

A. 30us

B. 20us

C. 15us

D. 60us

解析:

简单的环形振荡器一般是由反相器构成的,单端环形振荡器每一级会贡献180°的相移,偶数级贡献360°的整数倍,这样会形成正反馈,会出现电路锁定问题,就无法形成振荡。所以需要奇数级形成负反馈。

3、以下哪些活动属于DFT的内容(A,B,C,D)

A. Boundary SCAN

B. MBIST

C. DC SCAN

D. AC SCAN

4、在数字电路设计中,要求模块设计中保持寄存器输入输出的好处是(A)

A. 利于时序收敛

B. 降低亚稳态概率

C. 没有好处

D. 提高仿真速度

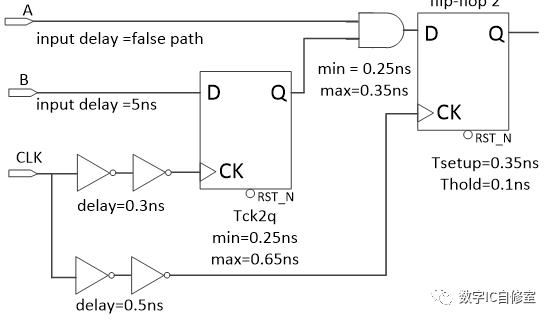

5、下面的电路中,flip-flop 2的hold time margin= 0.2ns

解析:

reg2reg的STA hold时序分析:Tlaunch+Tck2q+Tcomb>Tcapture+Thold所以flip-flop 2的 hold time margin=Tlaunch+Tck2q(min)+Tcomb(min)-Tcapture-Thold

=0.3+0.25+0.25-0.5-0.1

=0.2ns

6、下面verilog程序中,事件A分别在15ns,25ns处发生,而B一直为X态,请问在35ns时count的值为(2)(结果用十进制数字表示,例如3)

reg[7:0] count;

initial

count=0;

always

begin

@(A)count=count+2;

@(B)count=count+2;

end

解析:

always为进程,@(A)执行1次后,轮到@(B),不触发,一直等待。7、下面verilog程序执行完后,B的值为(8)(结果用十进制数字表示,例如3)

reg[2:0] A;

reg[3:0] B;

initial

begin

A=0;

A=A-1;

B=A;

B=B+1;

end

解析:

A=A-1时,由于没有给1设置位宽,转换成32bit做减法了,结果为0xffffffff,因此A=3’b111,所以B+1=4’b10008、用触发器设计一个最大计数为72的计数器,至少需要(7)个触发器。

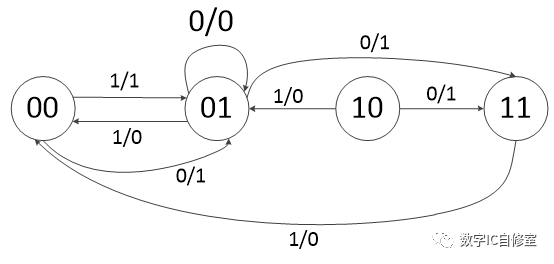

9、如图为某时序电路的状态图,设电路的初始状态为10,当序列A=011001(自左至右输入)时,该电路输出Z的序列为(101000)

解析:

该状态机为mealy状态机,状态的输出不仅和当前状态有关,而且跟各输入信号有关;Moore型状态机的状态输出只和当前状态有关。 如上图10状态的”0/1”表示在10状态下,输入信号为0则输出信号为1,并跳转到状态11。推导可得输出序列为101000。10、假设一个AHB总线频率是100M,数据位宽是64bit,一个APB总线频率为50M,数据位宽是32bit,请问理论上这个AHB总线的最大宽带是这个APB总线带宽的(8)倍。

解析:

AHB(AdvancedHigh performance Bus),高级高性能总线,AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字节和字的传输。AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummyMaster)所组成。

APB(AdvancedPeripheral Bus),高级外围总线。该总线协议是ARM公司提出的AMBA总线结构之一。APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。

理论上AHB传输为单周期,APB传输到双周期,所以带宽比为(100/50)*(64/32)*2=8

11、以下关于综合(synthesis)的描述正确的有(A,B)

A. RTL先被替代成通用的逻辑单元,再mapping到工艺库中的逻辑单元

B. RTL文件,设计约束,library和UPF文件是综合的输入

C. 综合的约束越紧越好,以便给后端实现留出足够的余量

D. 为模拟芯片实际使用的环境,综合一般使用typical的library

解析:

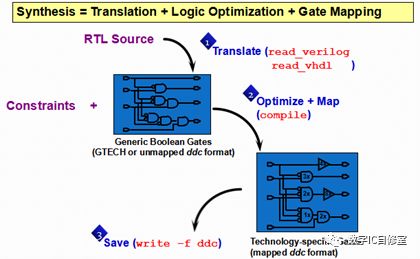

选项A:DC过程包括三个步骤,Synthesis= Translate + Mapping + Optimization,如下图:(1)Translate是将 HDL转化为GTECH库元件组成的电路(GTECH库是Synopsys公司提供的通用的、独立于工艺的元件库)

(2)Mapping是将GTECH映射到设计指定的工艺库(target library + link library)。

(3)Optimization是将网表按设计约束进行优化。

12、请问在下面Verilog代码实现中,初始值a=5,b=5,c=5,d=5时,下一个时钟b,c,d分别是多少?(A)

begin

b=a+1;

c=b+1;

d=c+1;

end

A. 6,7,8

B. 6,5,5

C. 6,6,6

D. 5,5,5

解析:

阻塞赋值;在赋值时先计算等号右手部分的值,这时赋值语句不允许任何别的Verilog语句的干扰,直到现行的赋值完成时刻,才允许别的赋值语句的执行。13、以下verilog代码中,clk,rst_n分别为时钟信号和复位信号。

wire clk,rst_n;

reg [3:0] counter;

wire out _data;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)counter <=4’b0;

else counter <=counter +1;

end

assign out_data=counter[0]&counter[2];

下列counter的状态变化中,哪种或哪些情况容易在out_data信号上产生glitch。(B)

A. 4’d1→4’d2

B. 4’d3→4’d4

C. 4’d2→4’d3

D. 4’d0→4’d1

E. 4’d4→4’d5

解析:

选项B:4’b0011—>4’b0100 counter[0]和counter[2]都需要翻转,因此容易出现glitch14、以下关于RAM表述正确的是(C、D)

A. Cache一般由DRAM组成

B. DRAM的每个存储单元需要更多的晶体管

C. RAM中存储的数据断电后丢失

D. SRAM不需要定时刷新

解析:

RAM(Random Access Memory),随机读写存储器。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,即一旦断电所存储的数据将随之丢失。

从名字上看,SRAM与DRAM的区别只在于一个是静态一个是动态。由于SRAM不需要刷新电路就能够保存数据,所以具有静止存取数据的作用。而DRAM则需要不停地刷新电路,否则内部的数据将会消失。而且不停刷新电路的功耗是很高的,在我们的PC待机时消耗的电量有很大一部分都来自于对内存的刷新。

SRAM存储一位需要花6个晶体管,而DRAM只需要花一个电容和一个晶体管。cache追求的是速度所以选择SRAM,而内存则追求容量所以选择能够在相同空间中存放更多内容并且造价相对低廉的DRAM。

15、以下有关FIFO的描述,正确的是(B)

A. 异步FIFO读写时钟的频率相同时,读写地址不必采用格雷码

B. 异步FIFO进行地址比较时,仅由地址相同是无法判断当前FIFO是空还是满的

C. 异步FIFO设计时,即使读写地址采用格雷码,仍然会出现快时钟域的地址信号在慢时钟域漏踩,从而导致空满判断错误造成功能问题,需要在设计时避免这种情况发生

D. 同步FIFO因为读写周期频率相同,所以不会出现溢出的情形

E. 异步FIFO设计时,读写地址采用格雷码可以避免亚稳态的发生

解析:

选项A:频率相同,若相位不同是异步时钟,需要采用格雷码 选项C:使用格雷码的情况下,地址信号漏踩会造成空满误判,但不会造成功能问题。第一种情况我们假定写时钟特别快,读时钟都采不齐写指针。

那么此时空逻辑会不会出错呢?假设写指针已经跑了1 2 3 4 5 6 7 8 9,而读时钟采到了1 2 6 8;那么如果此时读指针就在8,两边一对比发现一样(当然了这只是假设的一种情况)则会报“空”!那么实际空没空呢,没有。因为我写到9了写进去了一个数,不过没关系之后必然会采到9(或者采到10一类的),状态会很快恢复正常,或者说没有空而报了空的话我们还可以接受,因为这样对于一个将要空的FIFO会停止读,数旋即恢复正常,不会使其数据发生紊乱。那会不会有空了而报不空使得读出数据出现问题的情况呢?不会的,你想想看写指针跑的比你采样的快,是趋向与“不空”(越写数据越多嘛)的,因此不会出现这样的错误。读指针被同步到写时钟域本身不会出现漏采的情况,因此“满”逻辑的判断不会出现问题。

第二种情况我们假定读时钟域特别快,写时钟都采不齐读指针。

此时的满逻辑会出错么?我们来看下。我们同样假设读指针从1跑到了9,而只被采样到了7。如果此时写指针也写到了7,那么二者一比较发现写“满”了,实际呢没有满,不过此时也会停止外部写入(传出了满的信号),这是不会对FIFO中的数据产生影响的,并且很快会恢复到“不满”。如果此时写指针到了5,那么二者对比会得出“不满”的逻辑传出,真实情况呢同样是不满,因为读到7就已经不满了,真实情况读到了9自然更加“不满”。这样就解释清楚了。写指针被同步到读时钟域本身不会出现漏采的情况,因此“空”逻辑的判断不会出现问题。 选项D:同步FIFO写满,若不禁止写入也会出现溢出 选项E:亚稳态无法避免16、选择下列做法中对降低动态功耗效果最显著的两项(A,D)

A. RTL级电路设计优化

B. 电源门控

C. 多电压阈值

D. 门控时钟

解析:

选项B,C为降低静态功耗。RTL完成时至少80%的功耗已经确定,所以RTL级电路设计优化对动态功耗有很大的影响。17、以下关于AMBA总线表述不正确的是(B)

A. AXI有独立的读写控制,应答和数据通道

B. AHB的读写数据线是分开的,可以进行读写并行操作

C. AHB的读写操作可以pipeline

D. APB常用于寄存器配置之类的低带宽组合

解析:

选项B:AHB算是三通道协议,分别是读写数据和地址通道,读写共用一个地址通道,不支持读写并行。AXI支持读写并行。18、降低动态IR-DROP的方法包括(A,D)

A. 降低工作频率

B. 减少电源地直接的DECAP

C. 增加LVT Cell的比例

D. 增加接入的电源地IO数量

解析:

选项B:DECAP是一种特殊的Filler cell。当电路中大量单元同时翻转时会导致冲放电瞬间电流增大,使得电路动态供电电压下降或地线电压升高,引起动态电压降,俗称IR-DROP。为了避免IR-DROP对电路性能的影响,通常在电源和地线之间放置由MOS管构成的电容,这种电容被称为去耦电容或者去耦单元,它的作用是在瞬态电流增大,电压下降时向电路补充电流以保持电源和地线之间的电压稳定,防止电源线的电压降和地线电压的升高。 选项C:应减少LVT Cell,降低漏电流。19、以下关于复位表述正确的是(B,C)

A. 同步电路中不能使用异步复位

B. 不是所有的电路都需要复位信号

C. 所有的复位信号在测试中都要可控

D. 异步复位跟时钟异步,不需要时序检查

解析:

选项B:设计中可以有不需要复位的寄存器 选项D:异步复位若进行同步释放处理,需要检查recovery time20、以下关于时钟表述不正确的是(A,B,E)

A. 芯片中同频的时钟可以认为是同步时钟

B. Clock setup uncertainty等于PLL的jitter值

C. Clock skew可以用来改善时序

D. Clock transition太大会增加功耗

E. 同步电路只使用时钟的上升沿

解析:

选项A:同频,不同相是异步时钟 选项B:综合前uncertainty=jitter+skew+margin 选项D: transition太大会导致较大的cell delay,造成timing问题,并且会增加短路功耗。 选择E:上下边沿都可21、以下关于跨时钟域同步的描述,正确的是(D,E)

A. 当多比特数据需要跨时钟域进行同步时,必须要使用异步FIFO

B. 当多比特数据进行跨时钟域同步时,每一比特都进行两级同步,可以确保数据不会出错

C. 当单比特脉冲信号需要跨时钟域进行同步时,只要在目标时钟将此信号同步两拍即可

D.在CLKA时钟域下产生的信号到CLKB时钟域下使用时,亚稳态的出现是因为CLKB中的寄存器建立时间和保持时间的要求无法满足

E.当CLKA时钟域下的两个信号需要在CLKB进行逻辑与时,应先在CLKA下进行逻辑与后再同步到CLKB,而不是分别同步到CLKB,至CLKB下进行逻辑与操作。

解析:

选项A:若多比特数据是格雷码,可以进行打拍处理。若是快时钟域踩慢时钟域的缓变信号,可用DMUX 选项B:错,会出现重汇聚风险 选项C:脉冲信号在快时钟域到慢时钟域还需要展宽处理参考链接: https://blog.csdn.net/moon9999/article/details/77943407欢迎大家继续关注我们后续文章。 本文作者 | 奋斗者Y

● 欢迎转发,转载请注明出处,原创文章可后台联系我们开白。 彩 蛋

▼ 扫码备注入群,数字IC自修室欢迎你!

2931

2931

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?