1.简述

我在去年推出一系列的文章,分享一步一步搭建自己IC EDA环境,受到大家的认可。通过大家的反馈,强烈需要仅有数字前端工具的EDA虚拟机,降低虚拟机大小;因此去除一些不常用的工具,将虚拟机压缩至不到50G的大小;

近期出现不少倒卖我分享的虚拟机,甚至有培训机构拿去作为教学使用,特此严正声明:

声明:该EDA虚拟机仅供个人学习使用,且为免费使用,切勿商用;出现一切问题本人概不负责。

声明:该EDA虚拟机仅供个人学习使用,且为免费使用,切勿商用;出现一切问题本人概不负责。

声明:该EDA虚拟机仅供个人学习使用,且为免费使用,切勿商用;出现一切问题本人概不负责。

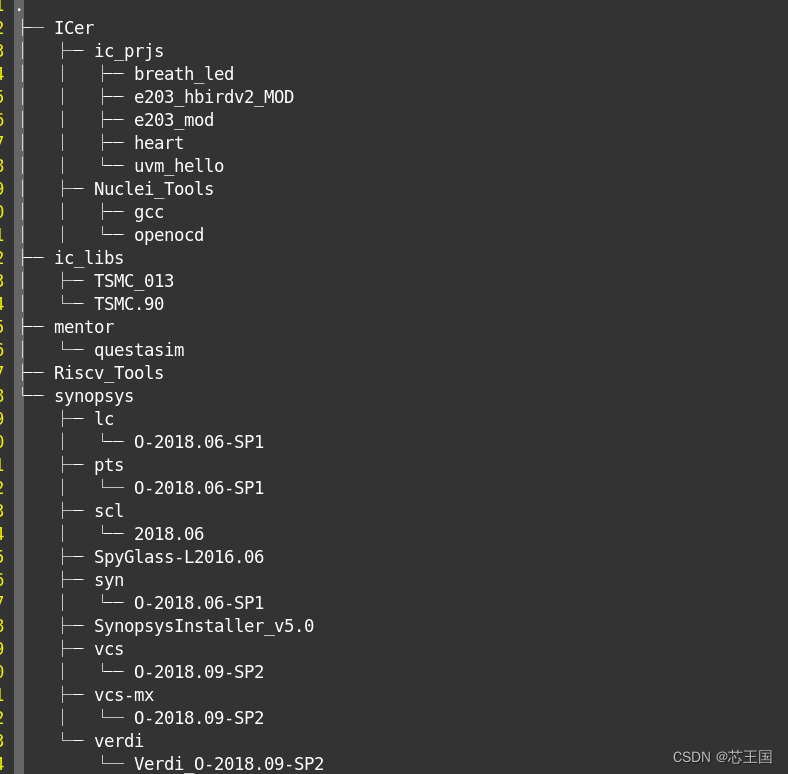

2.EDA虚拟机总览

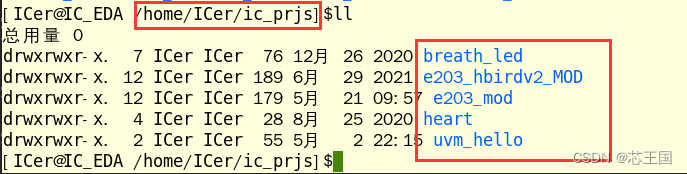

- ic_prjs下自带很多demo,供学习参考;还有蜂鸟E203开源RISCV环境以及工程,可直接使用;

- ic_libs下带有工艺库,可直接使用

- questasim 带UVM库

- 32位 RISCV工具链

- 各个Synopsys的工具

3.详细说明

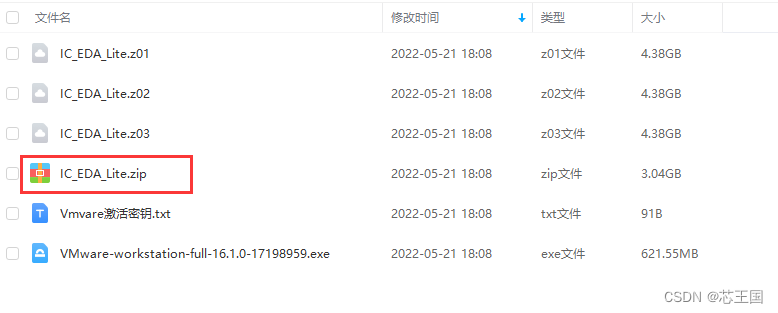

1)下载

- 分享链接中也提供vmware安装包;

- 由于文件比较大,采用分卷压缩的方式,所以需要下载所有文件,解压 压缩包图标的文件;

- 下载后,需要确认下载文件是否完整,没下载完的文件名会很长,明显带有网盘的扩展名;如果解压中有任何错误都需要重新下载;

- 该虚拟机仅有46G,但是最好磁盘空间有60G以上,在使用过程中会越用越大;

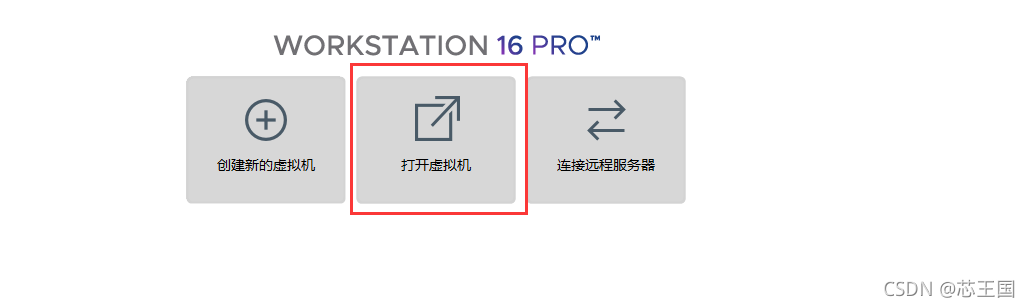

2)VMware添加虚拟机

我是使用VMware16_pro,创建的虚拟机,所以也需要这个版本VMware才能打开虚拟机。启动VMware后点击“打开虚拟机”;

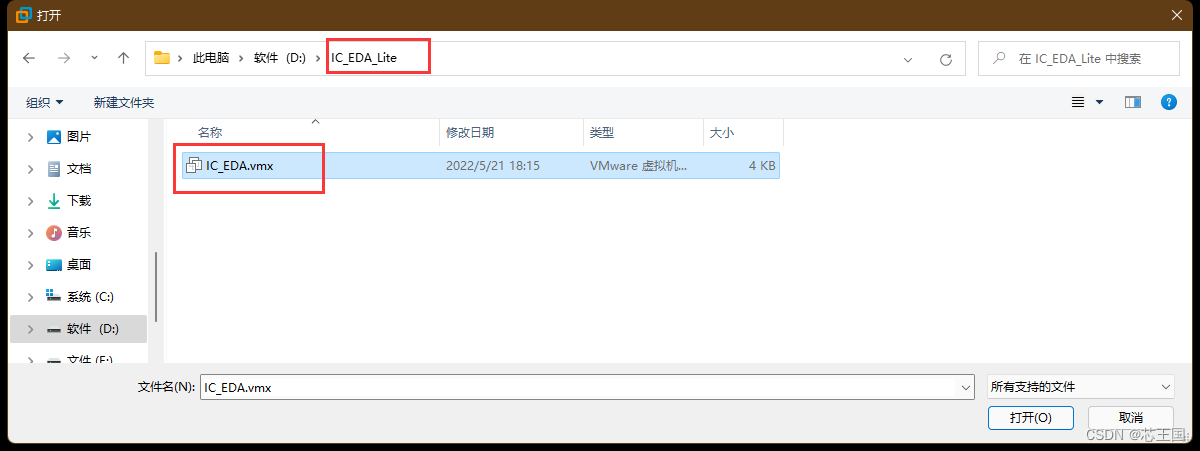

进入到自己IC_EDA解压的路径下,只有一个.vmx图标,选中就行;

3)修改设置

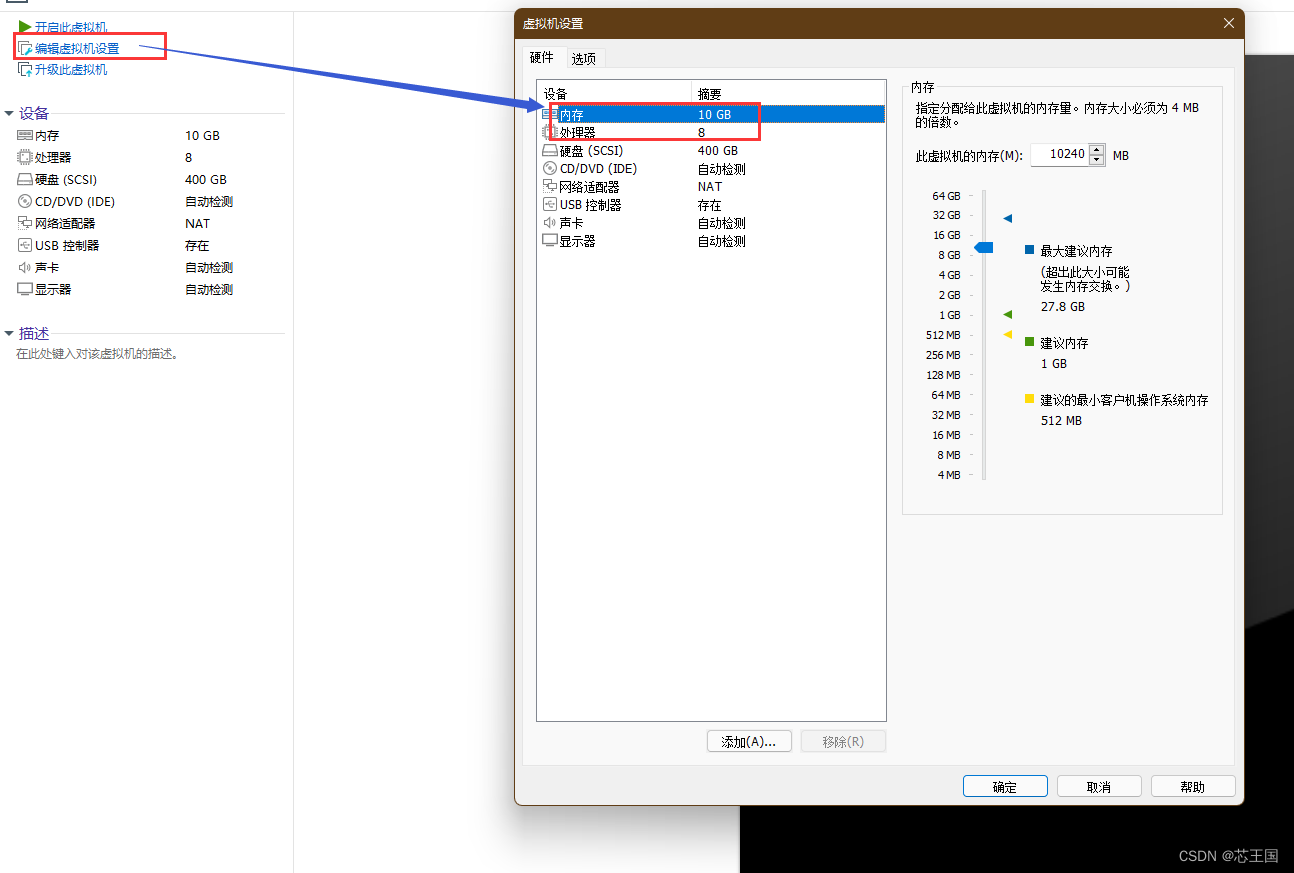

我默认分配虚拟机10G内存,8核,这里根据自己电脑情况分配,修改方法如图所示;

4)第一次启动

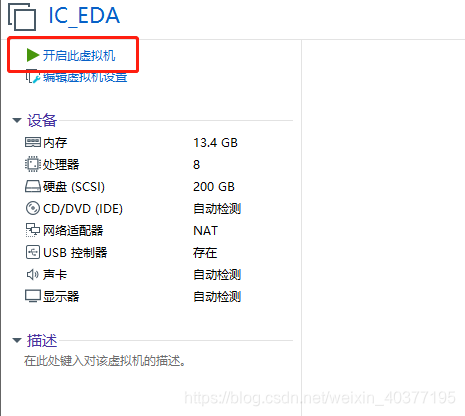

点击“开启此虚拟机”就可以启动了;

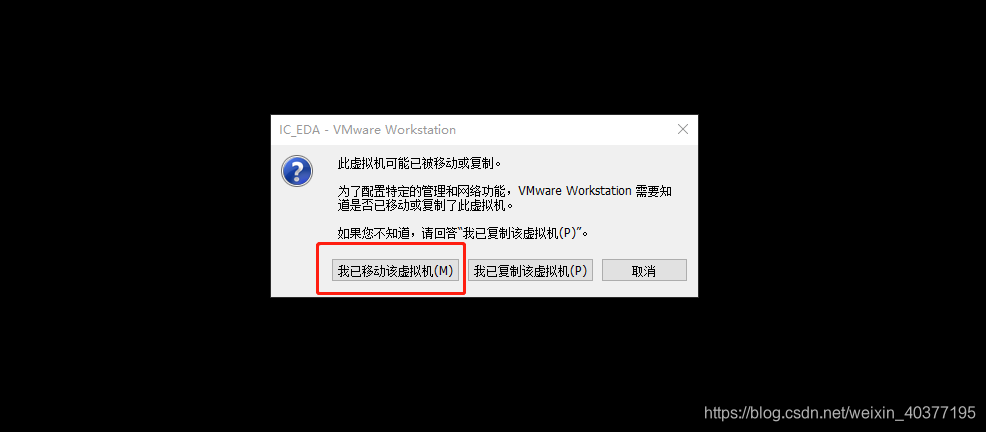

弹出的页面一定要选择“我已移动”;

5)虚拟机密码

- 登录密码:2022

- root密码:2022

6)已安装IC工具及命令

Synopsys:

- vcs(-SP2)

- vcs_mx(-SP2,带uvm)

- verdi

- dve

- pt

- dc

- dv(dc的gui)

- lc

- spyglass

Mentor: - questasim10.7c(带UVM)

工艺库: - TSMC_090

- TSMC_013

其他: - git

- gvim8.2

7)工具所在目录

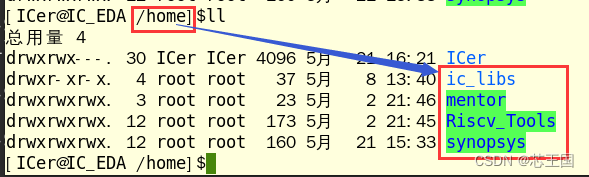

工具均在home下

8)DEMO工程所在目录

这里说明一下e203_hbirdv2_MOD是移植的工程,具体可以参看专栏第4部分内容;而e203_mod是蜂鸟老版本的工程,具体的移植情况请参看专栏里的前3篇内容;

专栏:蜂鸟E203学习

9)联网

默认是断开网络的,需要联网时,保证电脑联网,然后在虚拟机中点击“链接”;

注意: 不必要请少联网,话不多说懂得都懂;另外联网也会影响VCS仿真速度;

10)EDA获取

关注芯王国公众号,后台回复:IC_EDA_LITE,可以免费获取;

4.操作演示(重点必看)

IC_EDA_Lite版本虚拟机演示

或者点击直接跳转:B站传送门

5.总结

感谢广大粉丝的支持,反馈很多宝贵的建议,让我得以一点点完善虚拟机,欢迎大家交流,不限与虚拟机,FPGA、IC领域均可!!!

由于CSDN开始限制放置二维码,所以只有搜索 芯王国 关注我的公众号,公众号中有更多资源和干货,同时加入IC/FPGA,RISCV的交流群;

QQ群号:897532154

我的gitee:传送门

你可能需要的

centos7 升级安装 vim8.2(gvim)

Vmware 虚拟机 释放文件删除后的磁盘,缩小虚拟机大小

搭建属于自己的数字IC EDA环境(番外):S家EDA工具 license失效,TCP端口占用问题

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?