阻塞赋值“=”对应组合逻辑电路赋值(无存储功能,立即赋值),并且会阻塞后面的赋值操作,

非阻塞赋值“<=”对应时序逻辑电路赋值(有存储功能),所有非阻塞赋值操作在同一时刻进行赋值。

下面分别通过vivado综合不同情况赋值的代码。

第一种:在时序逻辑电路中使用阻塞赋值,通过综合后的电路可以看出非阻塞赋值综合出来的电路时立即执行赋值操作,和组合逻辑电路特性一致,无缓存功能,out_o直接被优化掉了。

always@(posedge clk or negedge rst_n)

if(~rst_n)begin

out_o <= 'h0;

out_o_1 <= 'h0;

end

else if(a_i)begin

out_o = b_i;

out_o_1 = out_o;

end

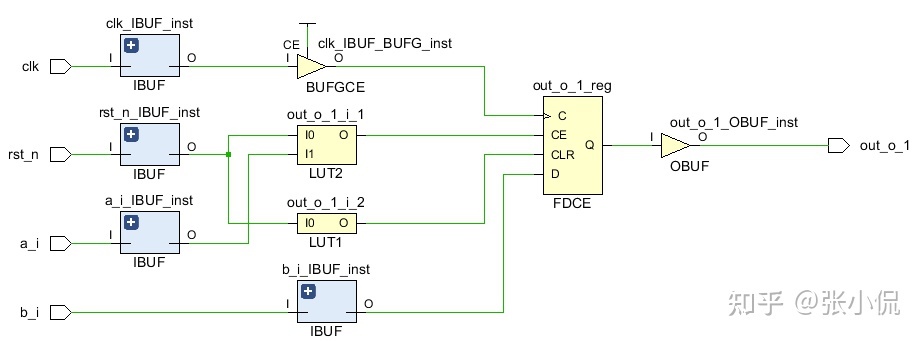

第二种:在时序逻辑电路中使用非阻塞赋值,通过综合后的电路可以看出非阻塞赋值综合出来的电路对应时序逻辑电路的特性,有缓存功能,out_o_1相较于out_o延迟一拍。

always@(posedge clk or negedge rst_n)

if(~rst_n)begin

out_o <= 'h0;

out_o_1 <= 'h0;

e

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?