差分阻抗90Ω±10%或者其他分别走什么阻抗

普通走线阻抗

必须选择 PCB 走线阻抗来匹配使用中的所有逻辑系别的特性阻抗(对于 CMOS 和 TTL,特性阻抗的范围是 80~110)。为了最好地将信号从源传送到负载,走线阻抗必须匹配发送设备的输出阻抗和接收设备的输入阻抗。

阻抗控制技术包括两个含义:

(1)阻抗控制的 PCB信号线是指沿高速 PCB 信号线各处阻抗连续,也就是说同一个网络上阻抗是一个常数。

(2)阻抗控制的 PCB 板是指 PCB 板上所有网络的阻抗都控制在一定的范围内,如20~75Ω。

线路板成为“可控阻抗板”的关键是使所有线路的特性阻抗满足一个规定值,通常在25~70Ω,一般取 50Ω。在多层线路板中,传输线性能良好的关键是使它的特性阻抗在整条线路中保持恒定。

HDMI接口布线要求

尽可能使 HDML连接器和器件之问的电气长度保持最短,从而使衰减最小化。为了使差分信号正常传输,一个差分对的两走线间距必须在整个走线轨迹上保持一致。否则,间距变化就会引起磁场耦合不平衡,从而降低磁场消除的效果,造成 EMI增加。推荐线宽间距比为1:1<W:S<1:2(W表示线宽,S 表示间距),差分线的线宽线距比如下图所示。HDMI差分走线控制阻抗要求是 100Ω,在计算阻抗的时候尽量按照此线宽间距比来进行。

差分等长、四对差分对之间的误差控制在 10mil 以内,每一对差分对对内之间的误差制在5mil之内,需要对单根走线进行绕线处理。PCB 设计的目的在于尽量将非连续性阳最小化。从而消除反射并保持信号完整。

可能发生非连续性的位置为:

(1)HDMI连接器焊盘同信号线迹相遇处;

(2)信号线迹碰到过孔、电阻器组件盘或IC引脚处;

(3)信号对被分离以围绕一个物体布线的地方,信号线的匹配电阻起防 ESD 作用和微调阻抗用途,通常靠近插座放置,但是两个电阻必须并排放置。

USB接口布线要求

(1)USB 差分走线越短越好,综合布局及结构进行调整。

(2)DP/DM 90Q差分走线,严格遵循差分走线规则,对内误差满足5mil。

(3)为抑制电磁辐射,USB 建议在内层走线,并保证走线参考面是一个连续完整的多考面,不被分割,否则会造成差分线阻抗的不连续性,并增加外部噪声对差分线的影响。穷间充足的情况下进行包地处理。同时尽量减少换层过孔,过孔会造成线路阻抗的不连续,实在需要的时候,建议在打孔换层处放置 GND 过孔。

(4)ESD保护器件、共模电感和大电容在布局时应尽可能地靠近 USB 接口摆放,线先通过静电器件及共模电感之后再进去接口。

(5)USB2.0规范定义的电流为500mA,但是VBUS走线最好能承受1A 的电流,以防过流。在使用 USB 充电的情况下,VBUS 走线需能承受 2.5A 的电流。

网口接口布线要求

MCU到网口芯片的走线,需进行等长控制,误差为 50mil。需进行阻抗控制,阻抗为50Ω。也应使其有完整的电源作为参考平面。

网口芯片到变压器及变压器到RJ45的信号为差分,一对 TX、一对 RX。阻抗控制为100Ω。需做对内等长,误差为5mil。

变压器在 PCB的投影区域内禁布器件和走线,电源层和地层需挖空。

LCD 接口布线要求

信号线需要做50Ω的阻抗控制。

应避免跨分割,注意不要从产生干扰的下方区域穿线。

总线有时序要求,需要进行等长控制,误差为50mil。

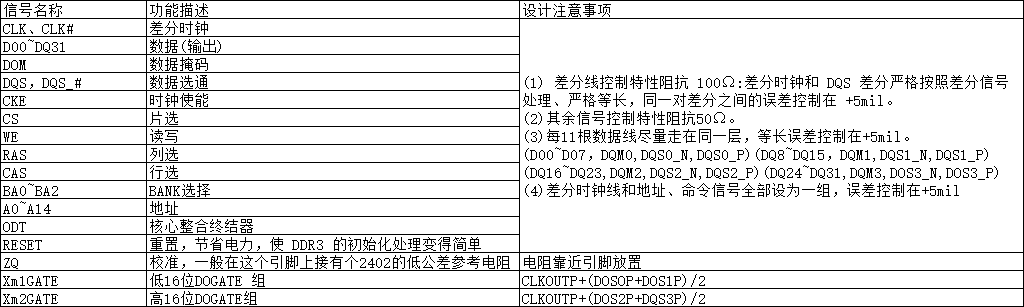

DDR3关键信号处理要点

1600

1600

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?