五、实验步骤与实验结果

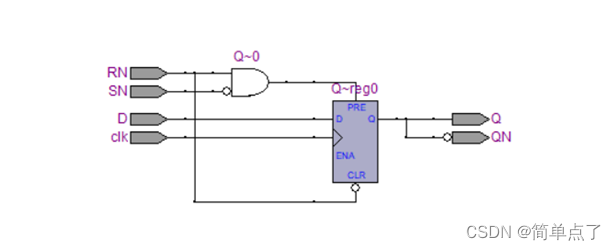

1、用Verilog VHDL设计D触发器。打开QuarterII新建一个基于ALTERA的Cyclone系列FPGA芯片EP1C3T144C8N的项目保存在D:\dianlu\ecp1文件夹中,新建一个Verilog HDL文件,将附件一代码写入,运行无错误,查看myD触发器的逻辑图(图1-1),重新运行,无误后,进行“Creat symbol files for current file”操作,将myD.bsf和myD.v文件复制到ecp2文件夹中。

图1-1 myD触发器的逻辑图

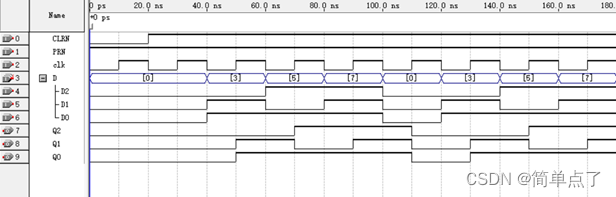

对myD触发器进行仿真。仿真图如图1-2myD触发器的仿真图。可知功能表与仿真图一致。

图1-2 myD触发器的仿真图

表1-3 myD触发器的功能表

| 输 入 | 输 出 | |||||

| Rd | Sd | CP | D | Qn+1 | Qn+1 | |

| 1 | 0 | × | × | 1 | 0 | |

| 0 | 1 | × | × | 0 | 1 | |

| 1 | 1 | ↑ | 1 | 1 | 0 | |

| 1 | 1 | ↑ | 0 | 0 | 1 | |

| 1 | 1 | ↓ | × | Qn | Qn | |

2、用myD触发器组成三位缓冲寄存器。再创建一个一个基于ALTERA的Cyclone系列FPGA芯片EP1C3T144C8N的项目保存在D:\dianlu\ecp2文件夹中,通过自己设计的D触发器进行基于3-1原理图的三位寄存器的设计,设计图如图2-1,连接完毕后进行引脚锁定,如图2-2。2-1图中的clk输入端口进行了硬件消抖,硬件消抖的原理,基本rs触发器是基于稳态电路的,输入端的抖动不会影响Q的输出,rs触发器的创建Verilog代码,见附件二。

图2-1 三位寄存器

图2-2 三位寄存器的引脚锁定

3、将三位缓冲寄存器进行仿真。仿真图如图3-2,仿真图解读:当CLEN(低有效)置0时,Q全输出0,当CLEN置1且PRN置1时,D在clk的上升沿赋值000,011,101,111,Q逐步输出000,011,101,111,实现了存储数据的功能。

图3-2 仿真图

4、将三位缓冲寄存器下载到FPGA开发板上进行测试,开发板验证结果可以对比仿真图的测试结果,判断逻辑功能是否正确。结果如图4-1,注意:LED灯是是输出为0时才亮

表4-1

| D2 D1D0 | Q2 Q1Q0 | 十进制的意义 |

| 000 011 101 111 | 000 011 101 111 | 存储数据的功能,对于本题目而言十进制的意义是:0,3,5,7 |

5、用myD触发器组成四位左移寄存器。再创建一个一个基于ALTERA的Cyclone系列FPGA芯片EP1C3T144C8N的项目保存在D:\dianlu\ecp3文件夹中,通过自己设计的D触发器进行基于3-2原理图的四位左移寄存器的设计,设计图如图5-1,连接完毕后进行引脚锁定,如图5-2。5-1图中的clk输入端口通过连接48端口进行了硬件消抖。

图5-1 四位左移移位寄存器

图5-2 四位左移移位寄存器的引脚锁定

6、将三位缓冲寄存器进行仿真。仿真图如图6-1,仿真图解读:当CLR(低有效)置0时,Q全输出0,当CLR置1且SN置1时,DIN在CLD的第一次脉冲(第一次上升沿)时,将1存到寄存器中,依次保持其余量不变,给予第2,3,4次脉冲,Q逐步输出0000,0010,0100,1000,实现了数据左移的功能。

图6-1 仿真图

7、将三位缓冲寄存器下载到FPGA开发板上进行测试,开发板验证结果可以对比仿真图的测试结果,判断逻辑功能是否正确。结果如图7-1,注意:LED灯是是输出为0时才亮

表7-1

| 脉冲个数 | Q3Q2Q1Q0 | 功能 |

| 0 1 2 3 4 | 0 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 1 1 1 1 | 随着cp脉冲数的增加,储存数据的位置逐个左移 实现逻辑左移 |

8、如何构建一个四位右移寄存器?如图8-1

图8-1 四位右移移位寄存器

图8-2 四位右移移位寄存器仿真图

表8-3

| 脉冲个数 | Q3Q2Q1Q0 | 功能 |

| 0 1 2 3 4 | 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 1 1 1 1 | 实现逻辑右移 |

六、实验讨论与总结

1.准备工作,Quattus创建一个D触发器和一个基本RS触发器,前者为了设计三位缓冲寄存器和四位左移移位寄存器,写verilog代码的时候一定要注意是上升沿触发还是下降沿触发。

2. 触发器最重要的功能,存储、计数和分频

3. CP时钟信号控制的只是器件的工作状况。而真正的输入是由D决定的

4.消抖分为硬件消抖和软件消抖,硬件消抖可以通过RS触发器来实现,软件消抖要通过分析一个短时间内的主脉冲。抖动的原因:机械开关在闭合和断开的时候电路存在一定的延时性和接触性等问题,会出现一些“毛刺”使得电路不稳定,影响稳定性。

6.移位寄存器的作用:存储和移位;移位的实现,受到移位脉冲的作用

7.本次实验和38译码器实现逻辑函数的电路实验的最大的区别在于前面是组合逻辑电路,现在是时序电路,前面输入和输出是“一触即发”的关系,而现在是与脉冲有关,与一段时间有关

附件一:myD触发器代码

module myD(D,clk,SN,RN,Q,QN);

input D,clk,SN,RN;

output Q,QN;

reg Q,QN;//寄存器定义

always @ (posedge clk or negedge RN or negedge SN)

begin

if(!RN)

Q<=0;

else if(!SN)

Q<=1;

else

Q<=D;

end

always @(Q)

begin

QN<=~Q;

end

endmodule

附件二:myrs触发器的代码

module myrs ( Rn, Sn, Q );//低有效的rs触发器

input Rn, Sn;

output Q;

reg Q;//寄存器定义

always @( Rn,Sn )

if(!(Rn&&Sn))

begin

case ({ Sn ,Rn })

2'b01:Q <= 1;

2'b10:Q <= 0;

endcase

end

endmodule

427

427

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?