关于FPGA同步电路中的一点小问题

对于上图所示的电路图,在数电中,我们知道,来了以此CLK之后,B模块是根据A模块flag的上一次变化而确定led的输出的,也就是说,假如clk到来之前,flag是0,clk到来之后,flag是1,那么clk到来之后,led的状态是根据flag为0而确定的。当时在下是认为数电基础中的分离元器件速度较慢,clk传播速度远大于模块的运行速度,因此才会这样。在FPGA这种高集成度的芯片会不会也是这样?有无可能A模块的转化速度大于clk的传播速度,由此与学数电基础时候的结论相反?网上搜了半天都搜不到答案,因此在下自己遍了一段代码,用signaltap观察结果。

这个是顶层模块

module dsdsds(input clk,

output led,

output led1 );

wire lianxian;

assign led1=1'b1;

mod_a moda(

. clk(clk),

. flag(lianxian)

);

mod_b(. clk(clk),

. flag(lianxian),

. led(led)

);

endmodule

``

这个是A模块

module mod_a(

input clk,

output reg flag

);

reg [1:0] counter;

always @(posedge clk)

begin

if(counter<2'b11)

begin

counter<=counter+1;

flag<=0;

end

else

begin

counter<=0;

flag<=1;

end

end

endmodule

这个是B模块

module mod_b(input clk,

input flag,

output reg led

);

always @(posedge clk)

begin

if(flag==0)

led<=0;

else led<=1;

end

endmodule

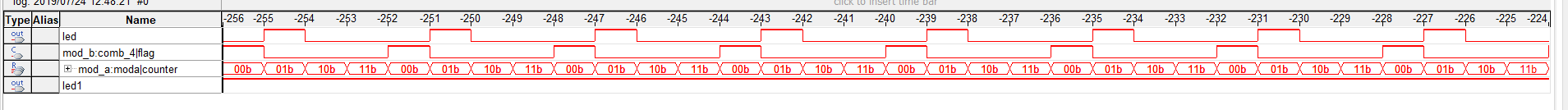

下图是signaltap的截图

也即

代码写得是,来了CLK的上升沿之后,如果flag=0,则led=0,flag=1,则led=1.由上图可知,led是根据flag变化之前的值改变的,也就是说,数电基础学的东西,在fpga中依然使用。

不过在下听说这个东西好像和一个叫时序约束的东西有关,在下新手,今天第一次玩板子,等过几天看了时序约束相关内容之后,再看看有没有什么新的发现吧。

3206

3206

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?