数字IC笔记

锁存器的结构

使用两个或非门或者是与非门构成。

[SR锁存器](https://blog.csdn.net/weixin_44988101/article/details/106020435)

DFF(D触发器)的结构

在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。相当于jk触发器,将k端用反相器与j端连接。

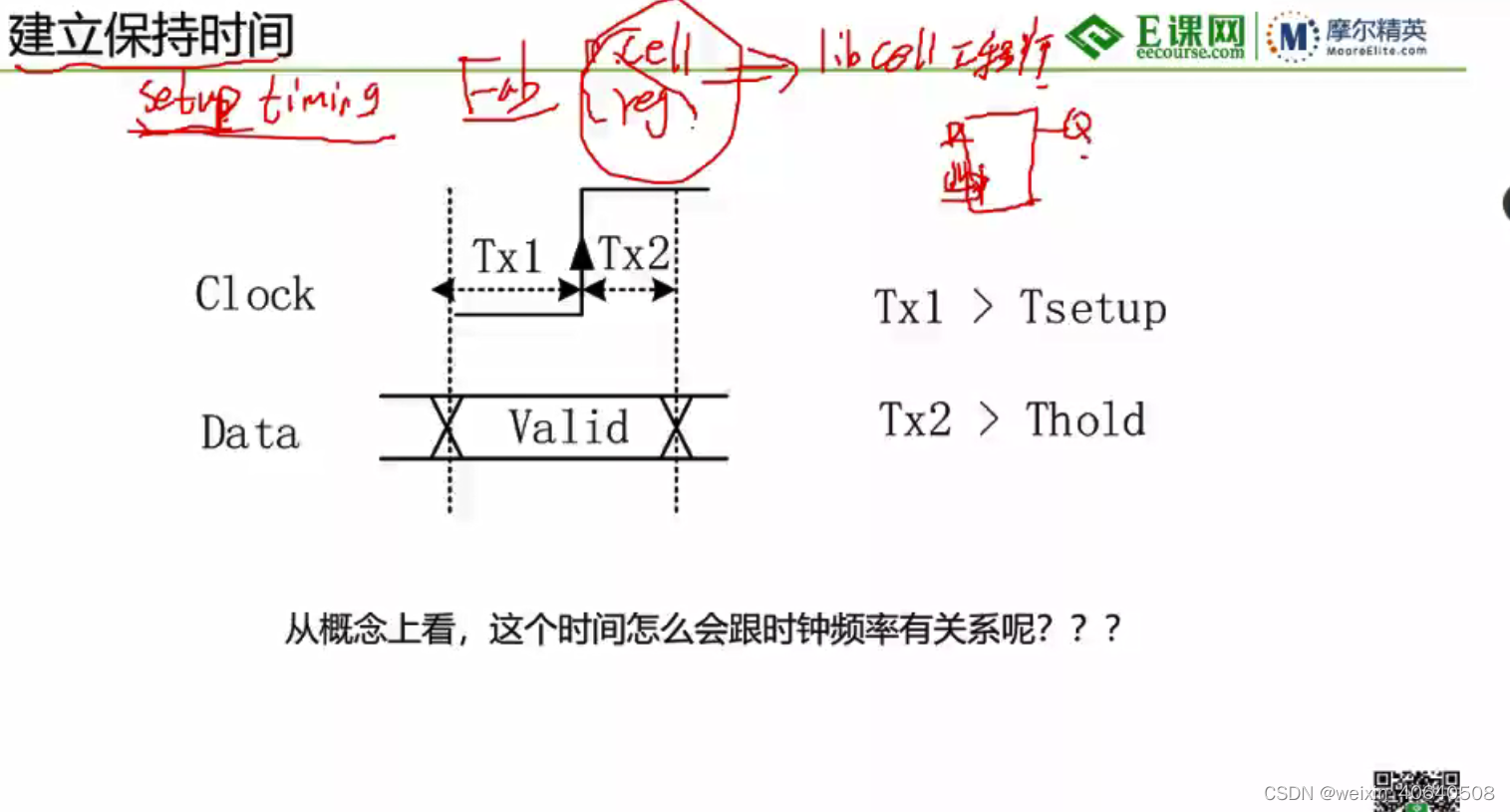

建立时间、保持时间、传输延迟时间和传输无效延迟

建立时间(tsu):输入信号应当先于时钟信号CLK动作沿到达的时间。

保持时间(th):时钟信号CLK动作沿到达后,输入信号仍然需要保持不变的时间。

传输延迟时间(tpd):从CLK动作沿到达开始,直到触发器输出的新状态稳定建立所需要的时间。

传输无效延迟(tcd):输入信号开始变化到输出信号开始变化

在这里插入图片描述

FIFO

-

同步FIFO

同步FIFO-读写时钟clock是同一个clock。

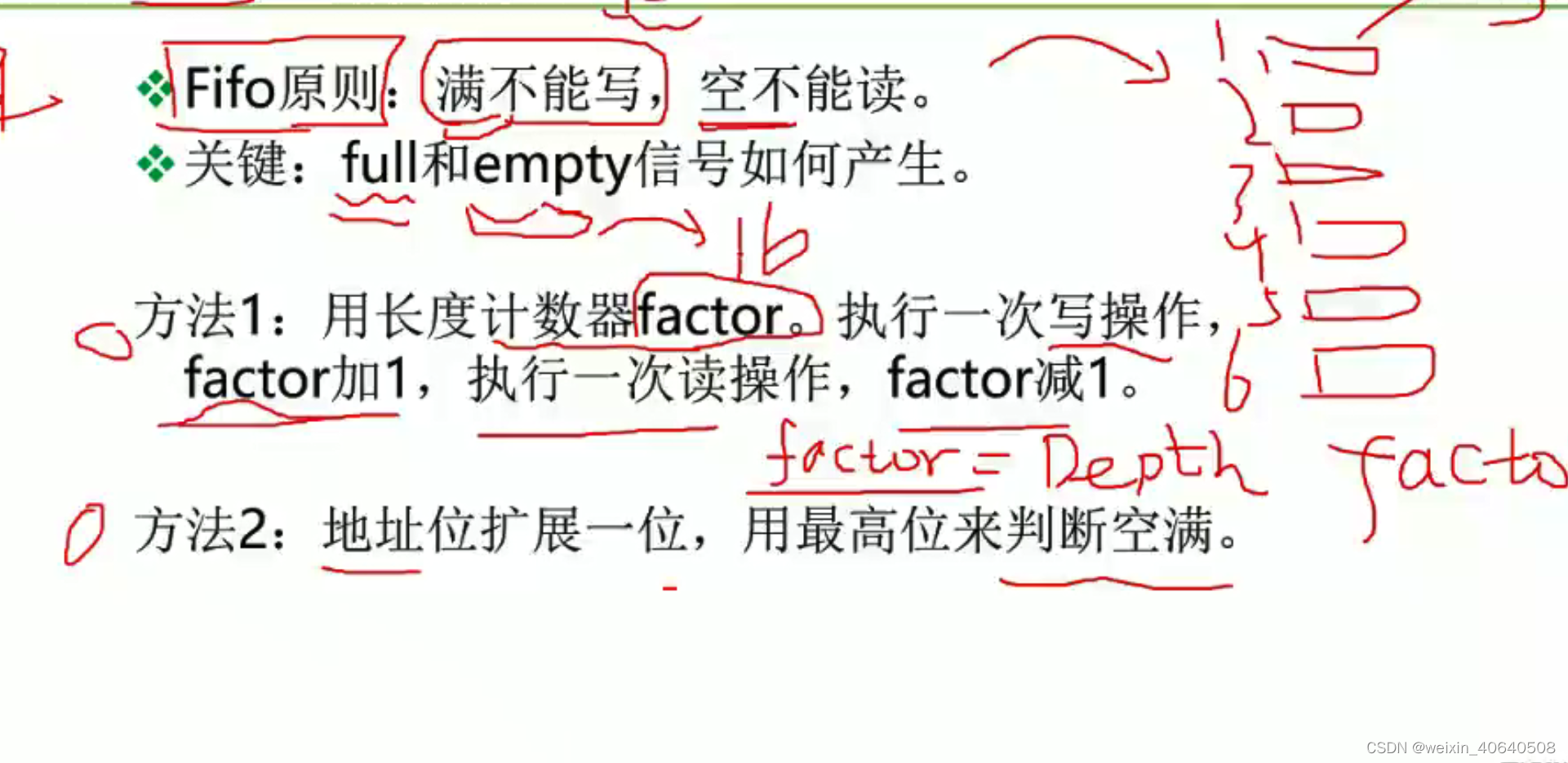

(1)FIFO原则:满不能写,空不能读。

(2)关键:full和empty信号如何产生。两种方法:

方法1:用长度计数器factor。执行一次写操作,factor加1,执行一次读操作,factor减1。

方法2:地址位扩展一位,用最高位来判断空满。 -

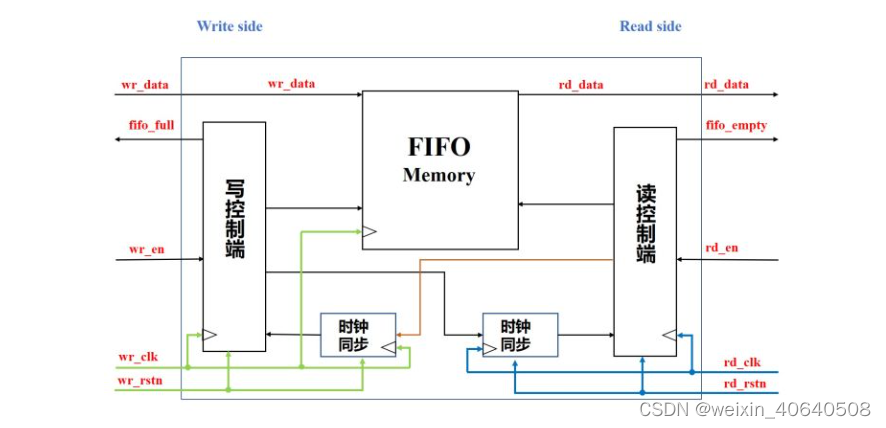

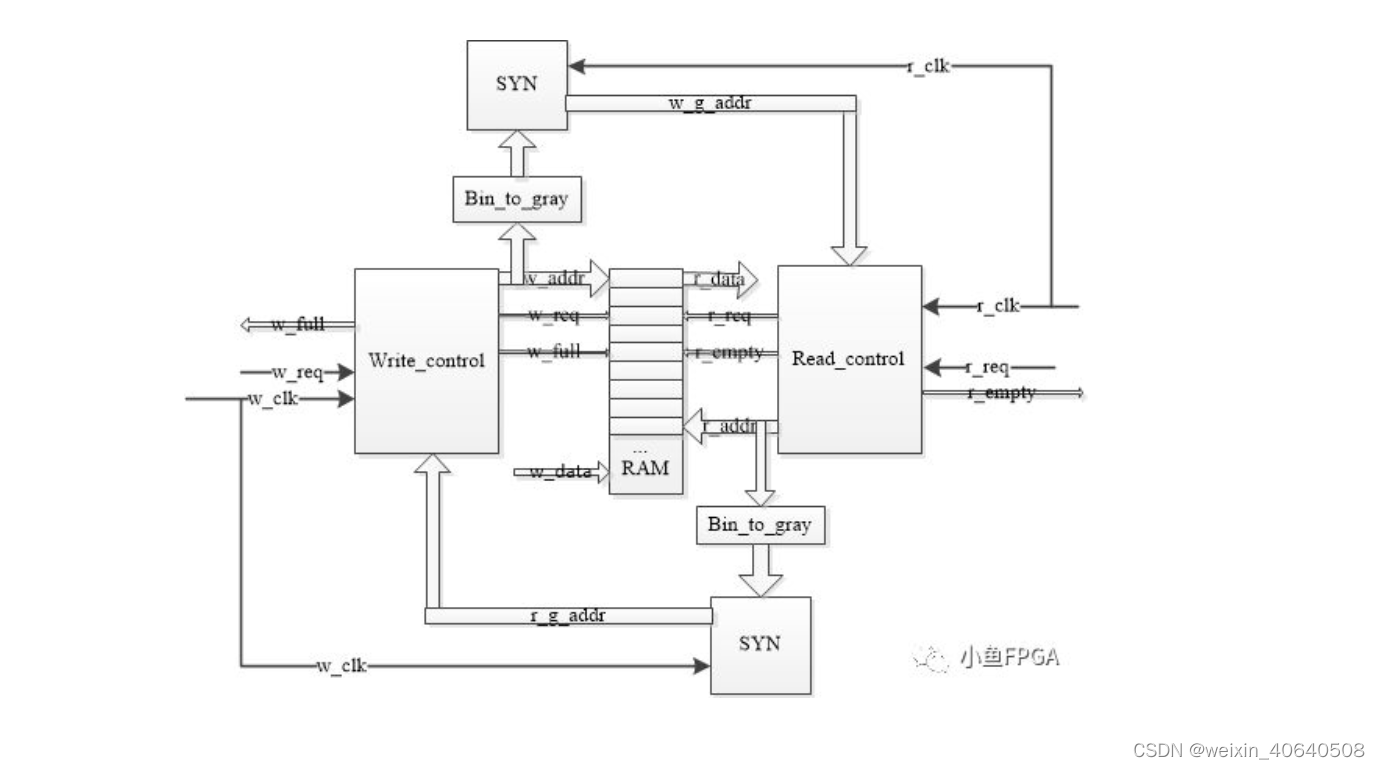

异步FIFO

使用扩展地址位的方式来判断空满。

读写信号时钟不同。

关键:格雷码的使用。

https://mp.weixin.qq.com/s/_PrMnCkto0i_HWvld3g5Xg

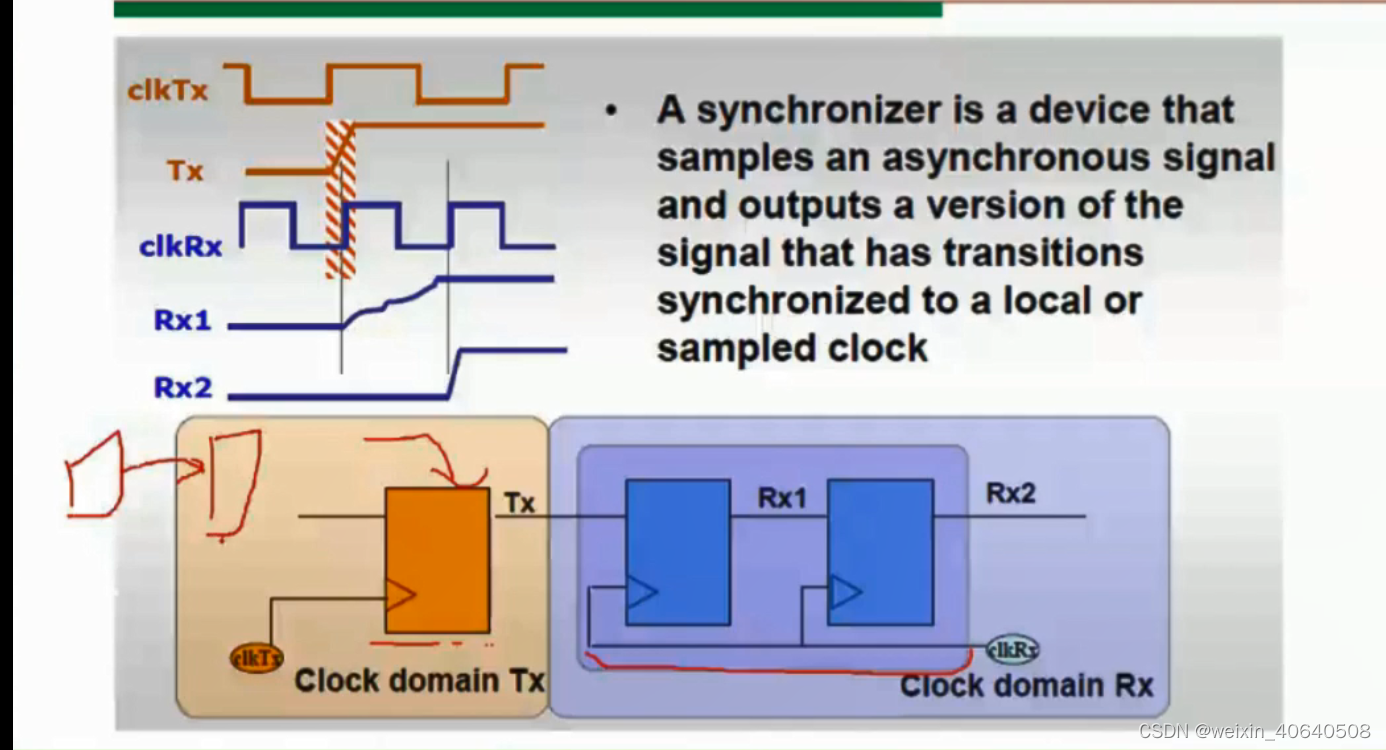

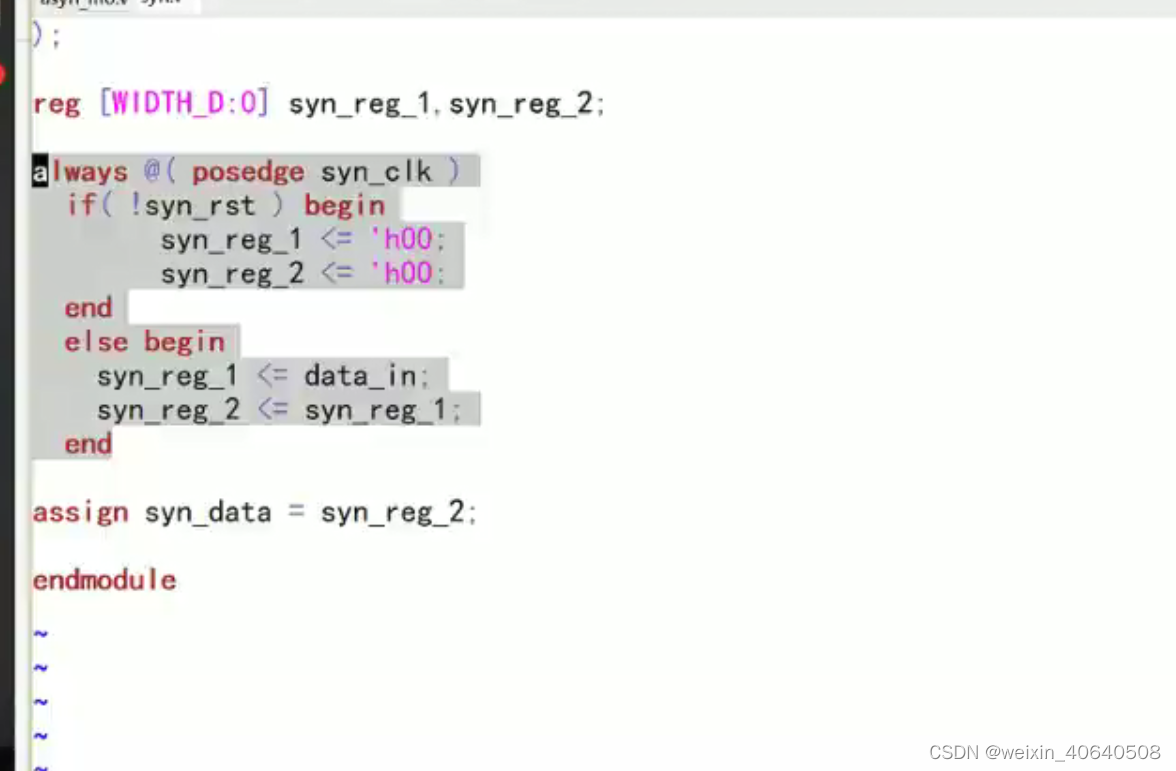

syn 模块原理就是打两拍

关键点解释

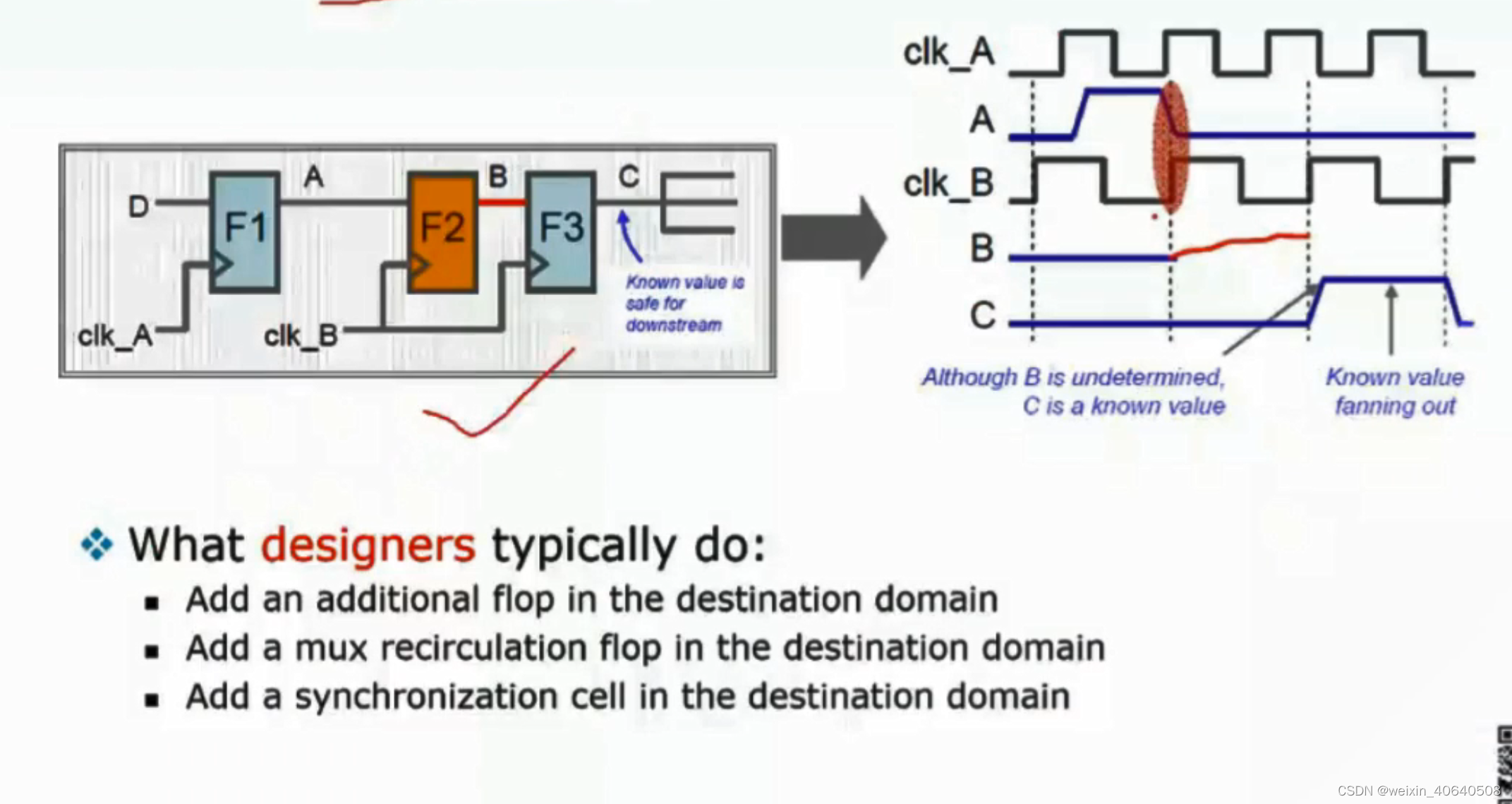

1.跨时钟域传递信号做时钟同步一般通过打两拍。

2.采用格雷码编码,因为格雷码每次跳转只会有一位发生变化,所以如果出现不确定状态也只会有两种状

况,即正确变化了和不变。因此在读写时钟不一样的情况下,纵使读写时钟同步过程中出现亚稳态(毛刺是组合逻辑的异常情况),也不会使得FIFO在实际空或者满之后,FIFO却没有正确的产生出空满信号。只有可能是实际没有空或者满,但产生了空满信号,但这对于FIFO的功能不会有影响,只会使得FIFO的读或者写操作暂停。

格雷码不能消除亚稳态,但是降低出错的概率,就算出错也不会对功能产生影响。

3.读比写时钟更快,只会只出现实际没满,但误判为满;不会对功能(数据流)造成错误。

4.写比读时钟更快,只会出现实际没空,但误判为空;不会对功能(数据流)造成错误。

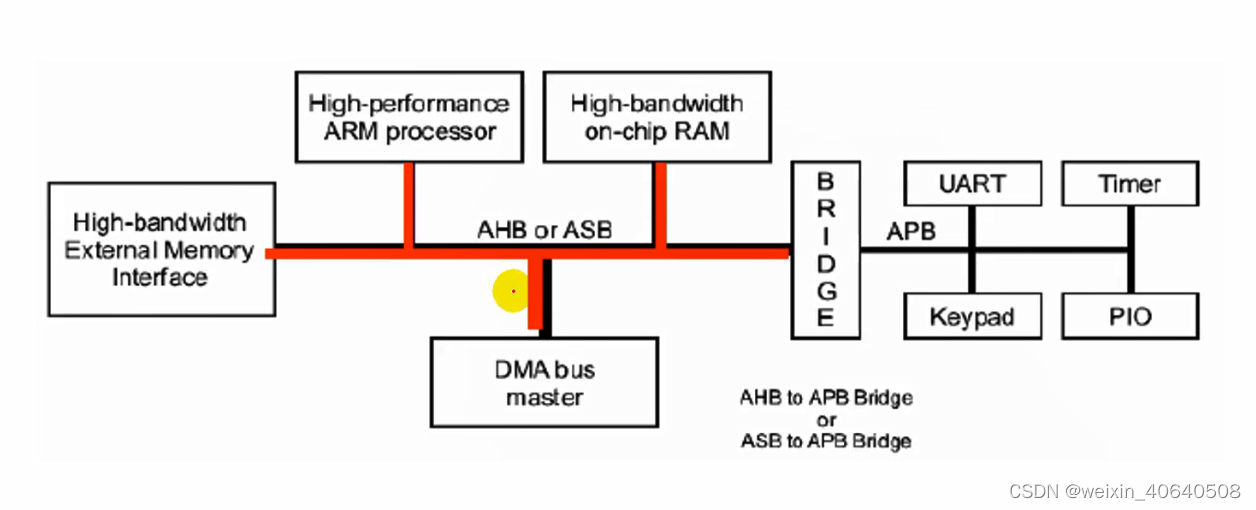

AMBA、AHB、APB、AXI总线介绍及对比

https://blog.csdn.net/weixin_44425619/article/details/115207331

AMBA 总线

知识点:

-

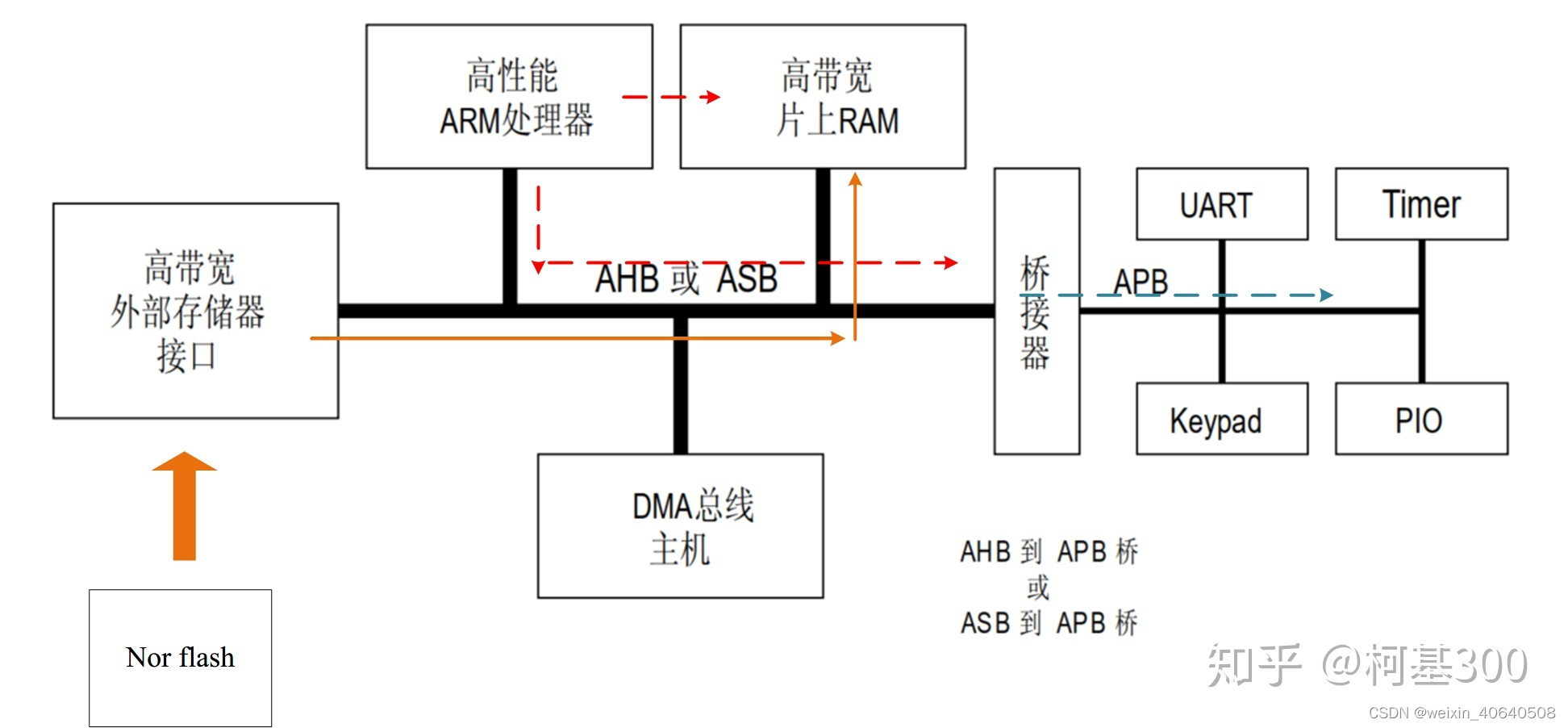

AMBA简介

AMBA2.0:AHB、ASB(现在不常用)、APB -

AHB的组成部分

AHB master、AHB slave、AHB arbiter、 AHB decoder -

APB的组成部分

AHB2APB bridge(在AHB中是slave,在APB中是master) -

AHB信号(H开头代表的是AHB信号)

HCLK、HRESETn、HADDR、HTRANS、HWRITE、HSIZE、HBURST、HWDATA、HSELx、HRDATA、HREADY、HREST. -

AHB传输的两个阶段

地址周期、数据周期(写:先发地址再发数据,读: 先发地址,返回数据) -

当前传输的状态HTRANS

IDLE、BUSY、NOSEQ、SEQ -

猝发传输类型HBURST

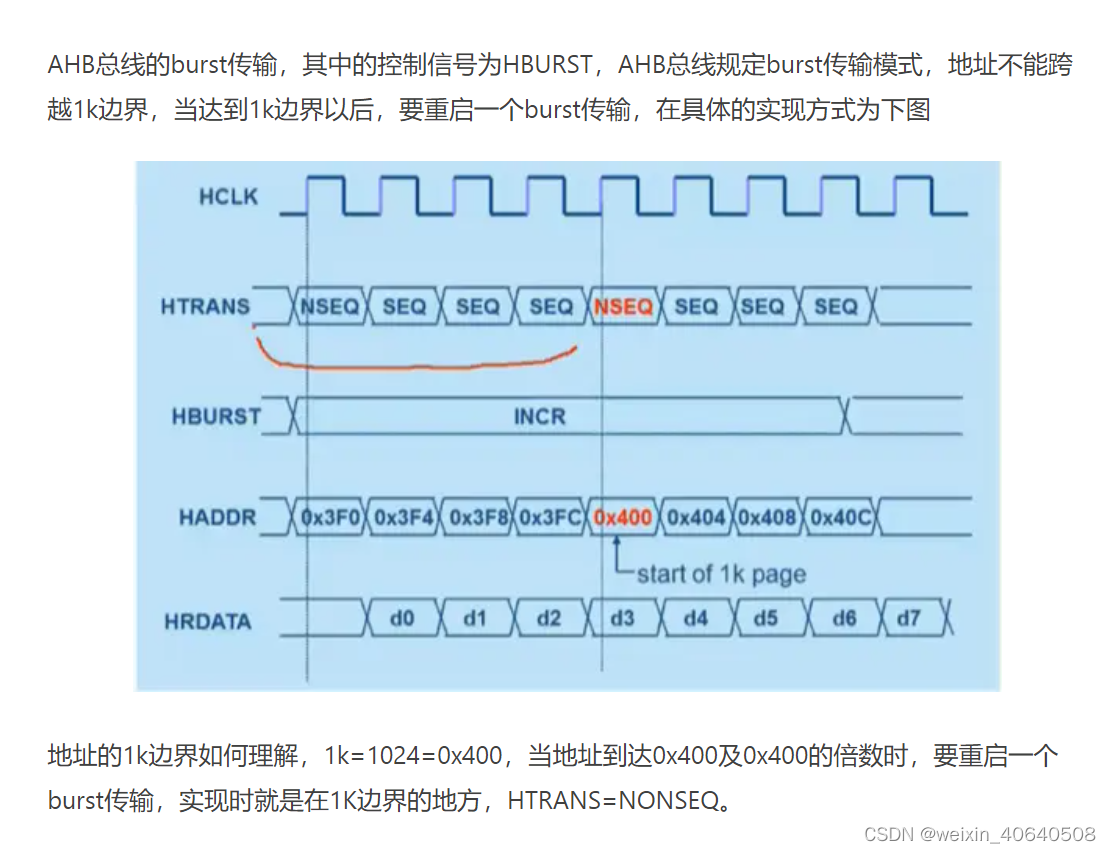

SINGLE、INCR(如何开始一次新的INCR传输?)

Burst传输不可跨越1K边界 -

HSEL:由AHB decoder 通过地址映射给出

-

AHB slave响应信号

-

HREADY传输完成、HRESP传输响应(OK、ERROR、RETRY)

-

AHB slave短时间无法响应?长时间无法响应?使用RETRY。

-

AHB

AMBA 总线概述

AHB组成部分

- AHB主设备(master)

- 初始化一次读/写操作

- 某一时刻只允许一个主设备使用总线

- CPU、DMA(Direct Memory Access)、DSP、LCDC…

- AHB从设备(slave)

- 响应一次读/写操作

- 通过地址映射来选择使用哪一个从设备

- 外部存储器控制器EMI、APBBridge

- AHB仲裁器(arbiter)

- 允许某一个主设备控制总线

- 在AMBA协议中没有定义仲裁算法(即可能是随机分配总线给主设备)

- AHB译码器(decoder)

- 通过地址译码来决定选择哪一个从设备

APB组成部分

- AHB2APB Bridge(在AHB中是slave,在APB中是master)

- 可以锁存所有地址、数据和控制信号

- 进行二级译码来产生APB从设备选择信号

- APB总线上的所有其他模块都是APB从设备

AMBA协议其他有关问题

- 与工艺无关

- 没有定义电气特性

- 仅在时钟周期级定义时序

- 提取时序参数依赖于所采用的工艺和工作频率

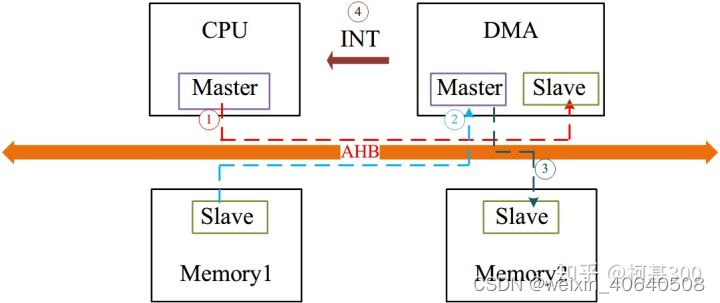

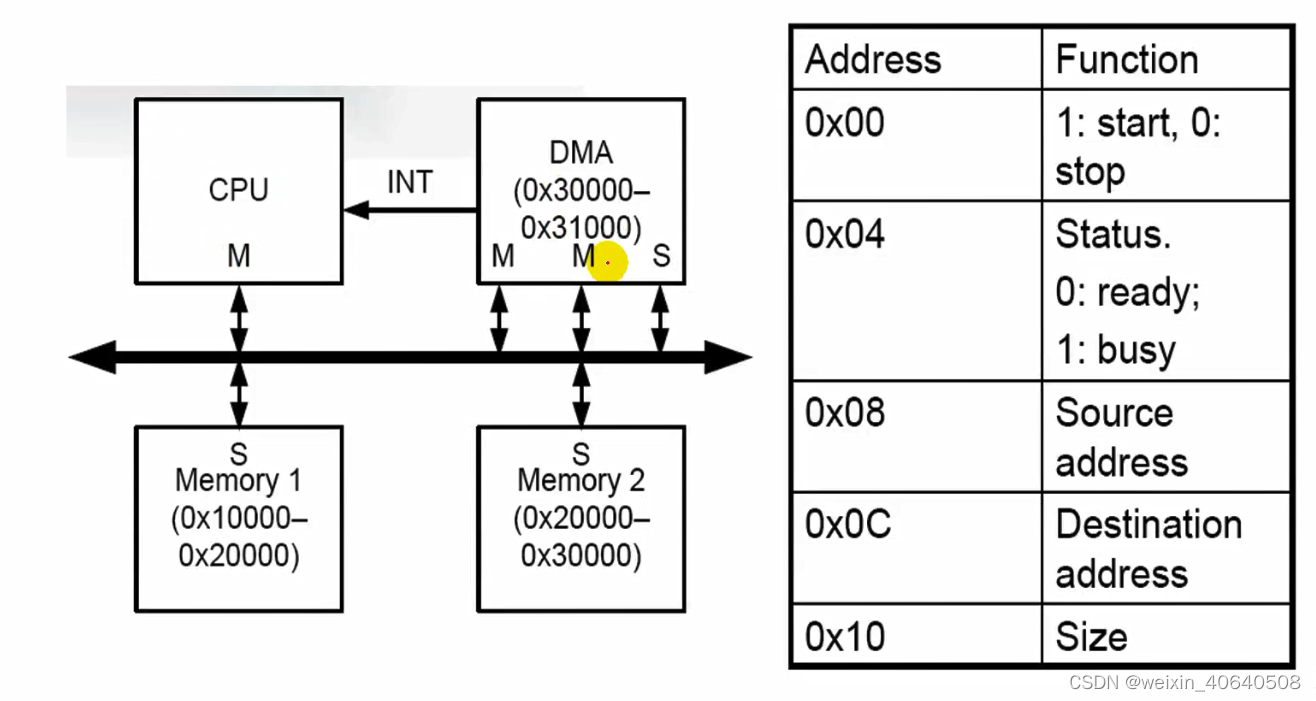

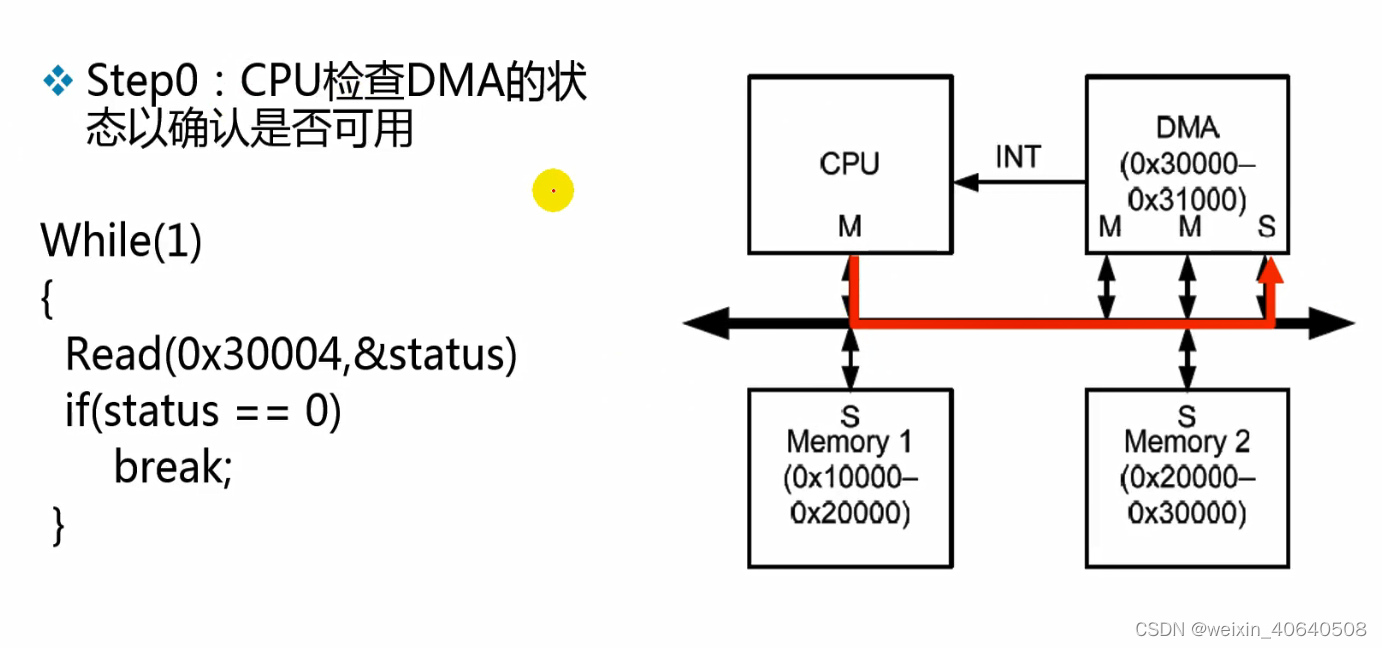

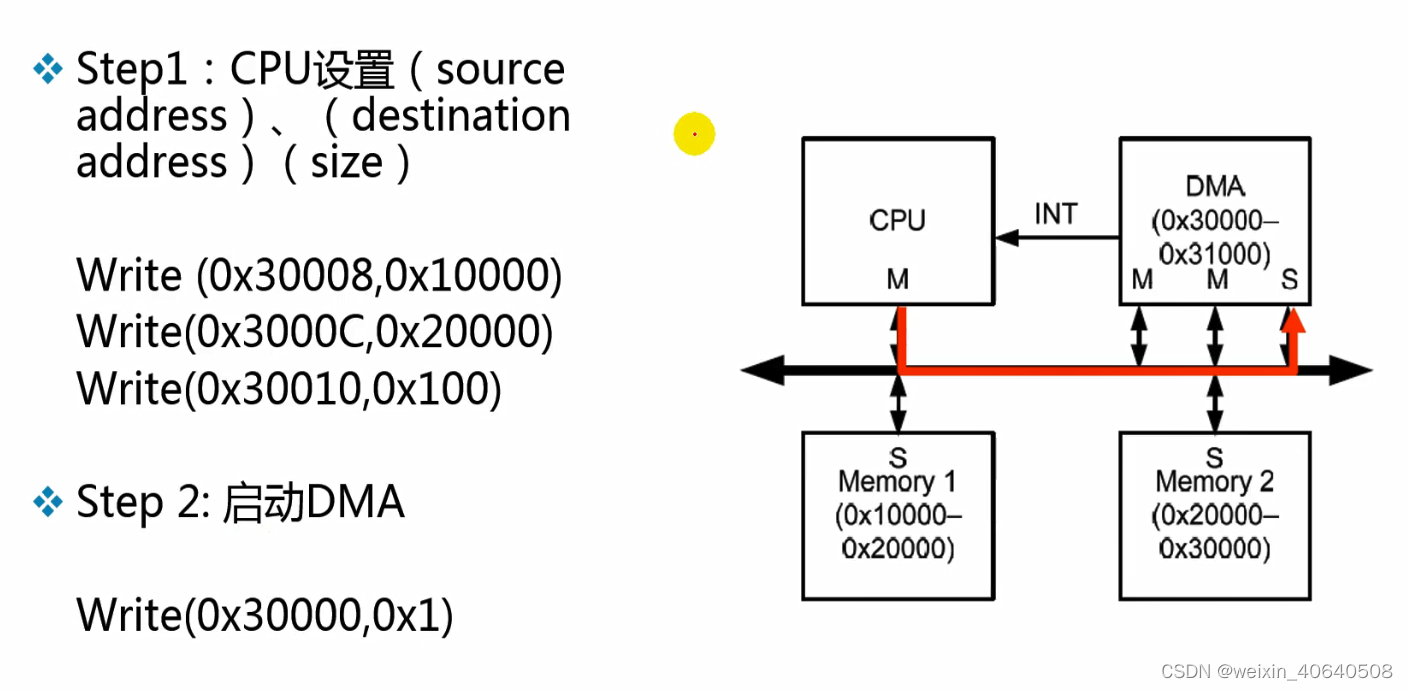

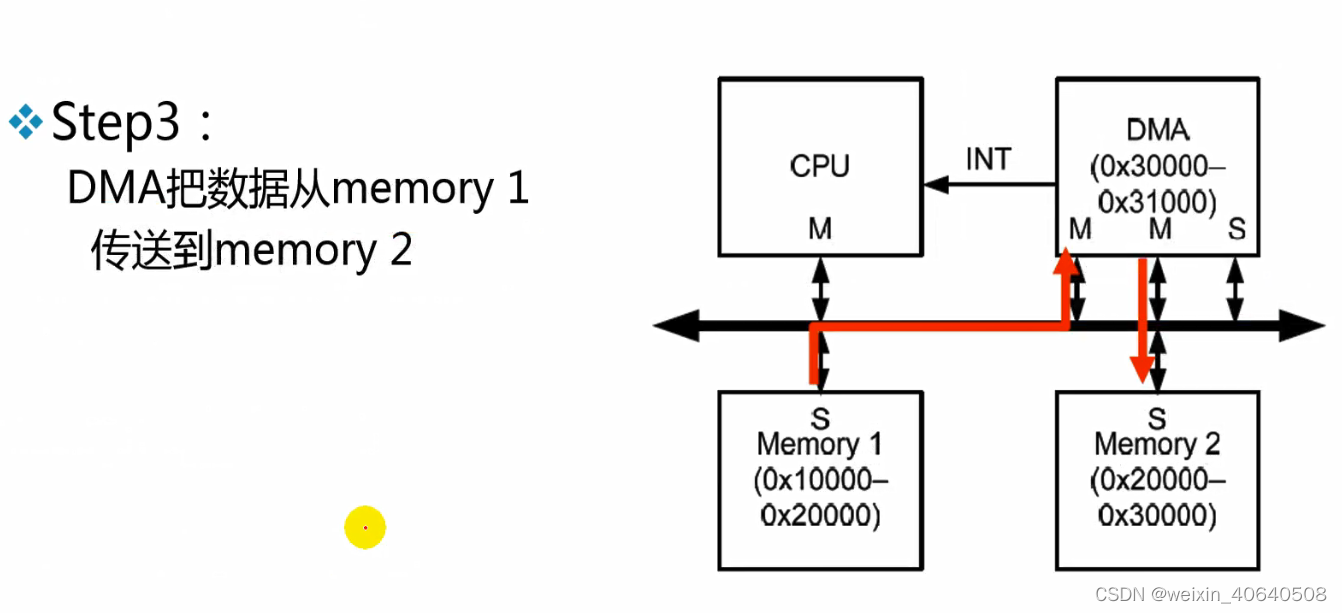

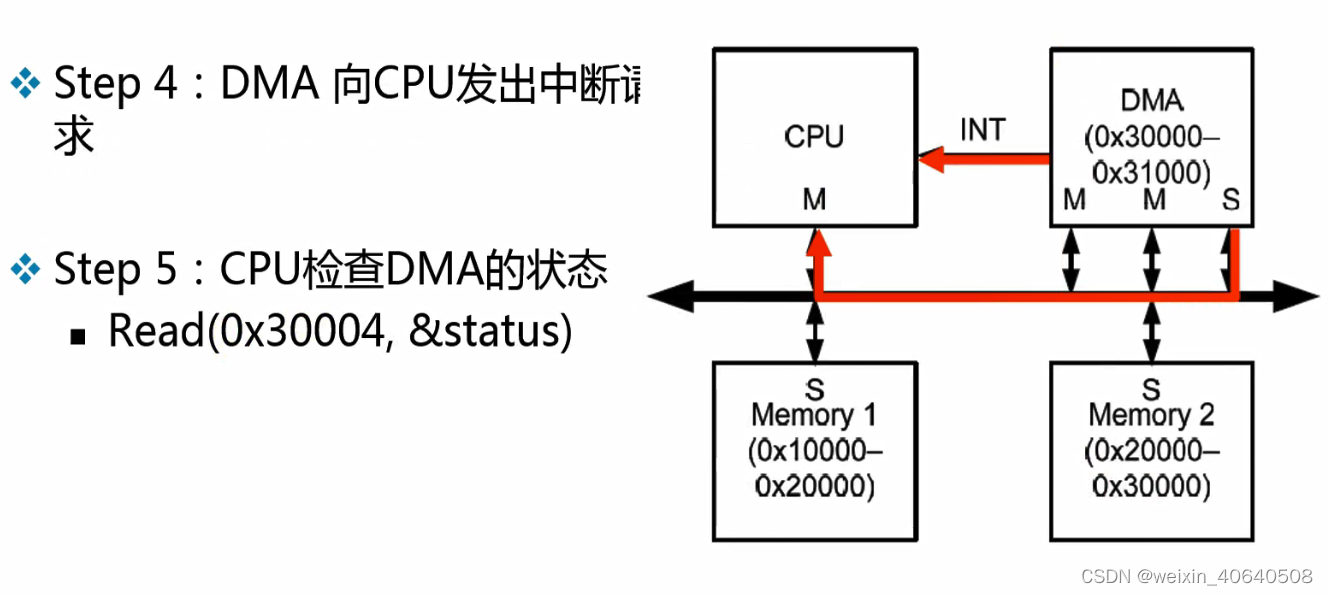

DMA

框架:

例子:

AHB总线互联

AHB传输

https://zhuanlan.zhihu.com/p/490952995

基本的AHB传输

-

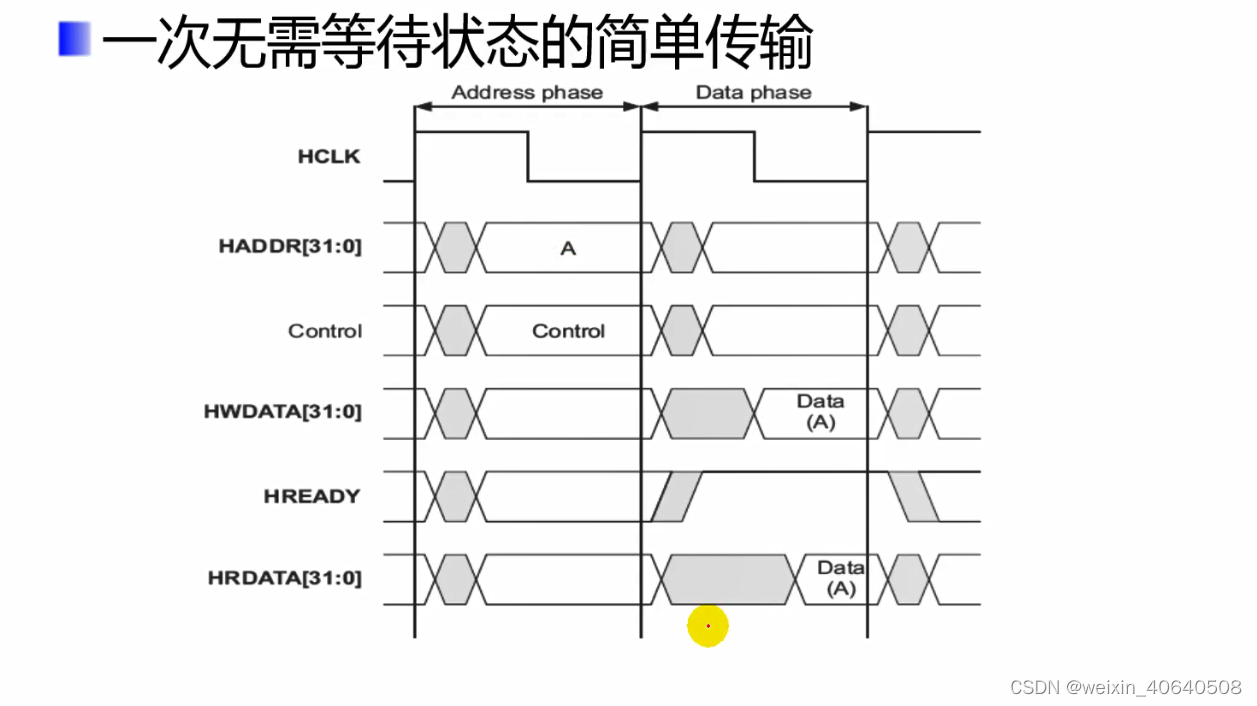

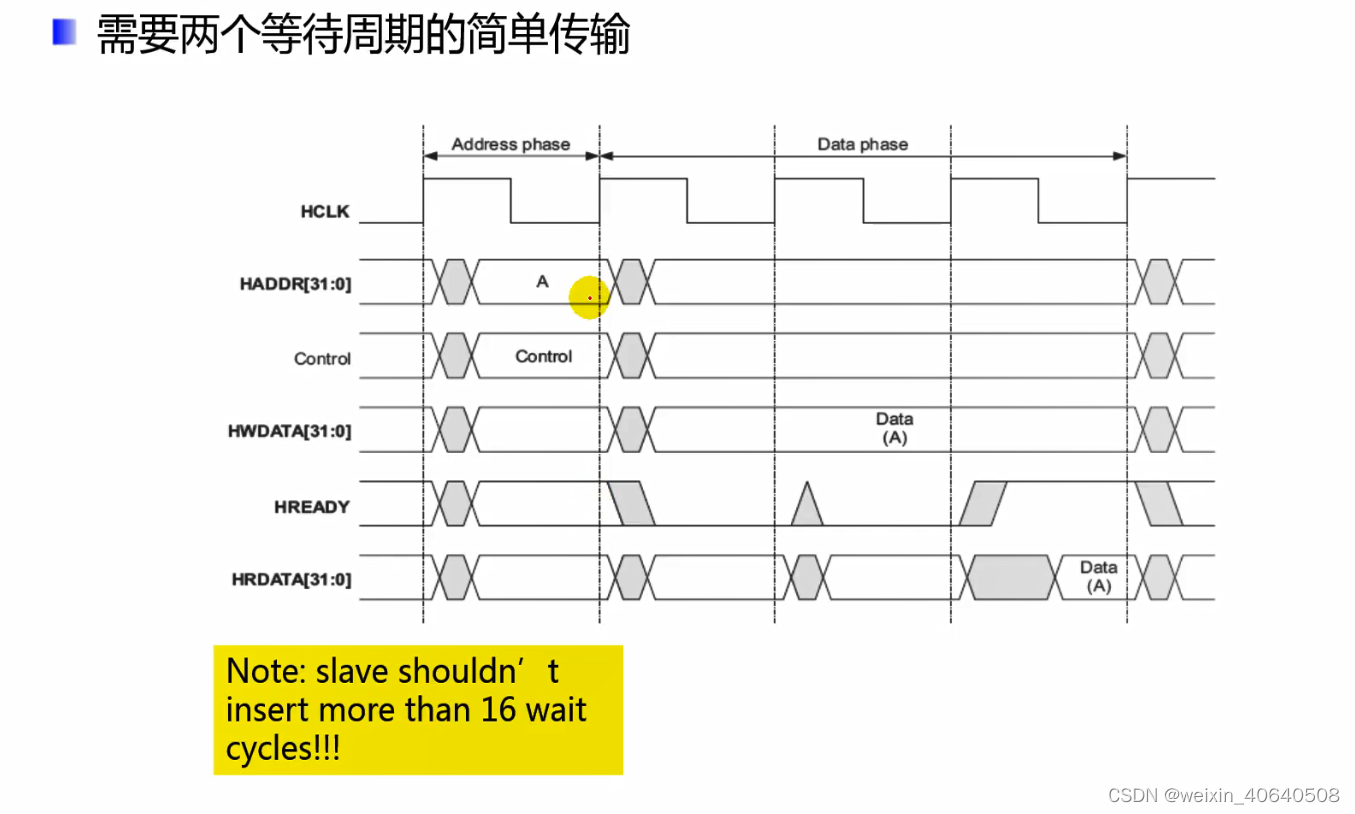

两个阶段

- 地址周期,由HREADY信号决定需要几个cycle

- 数据周期,由HREADY信号决定需要几个cycle

-

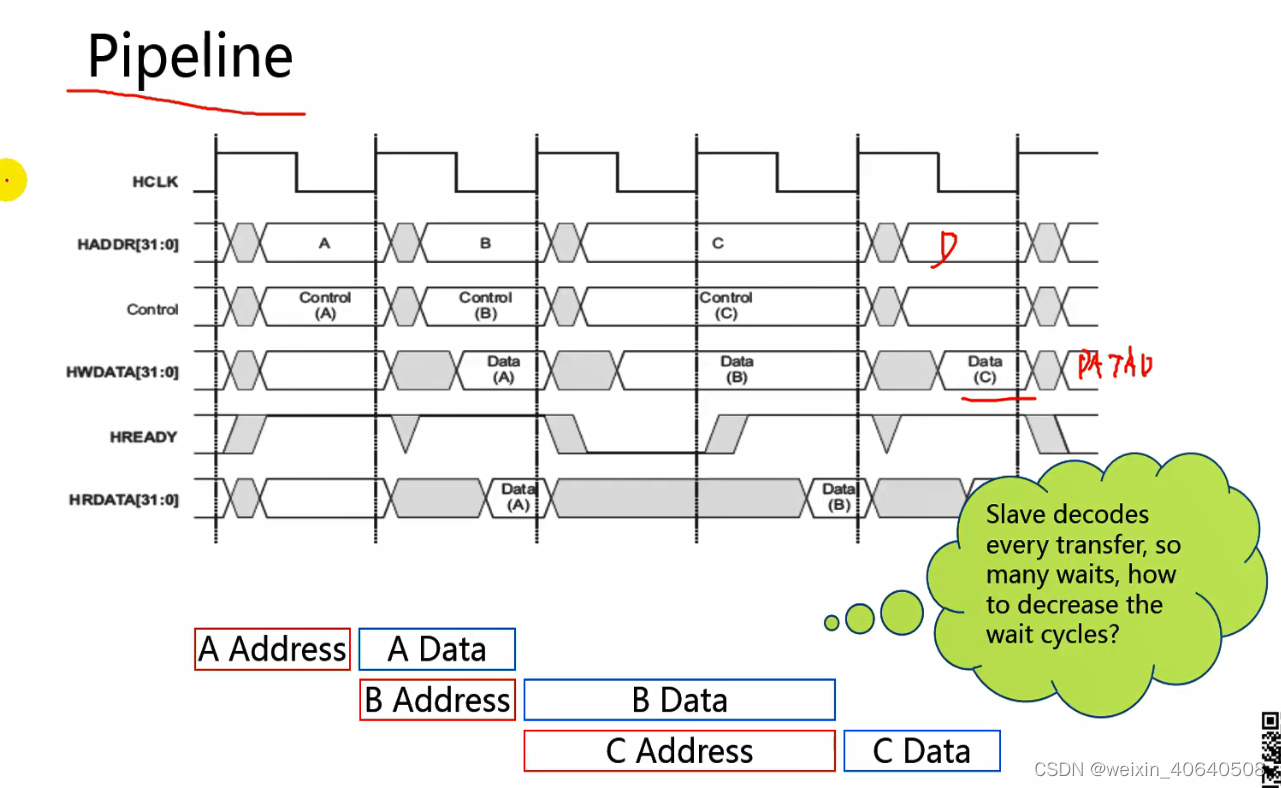

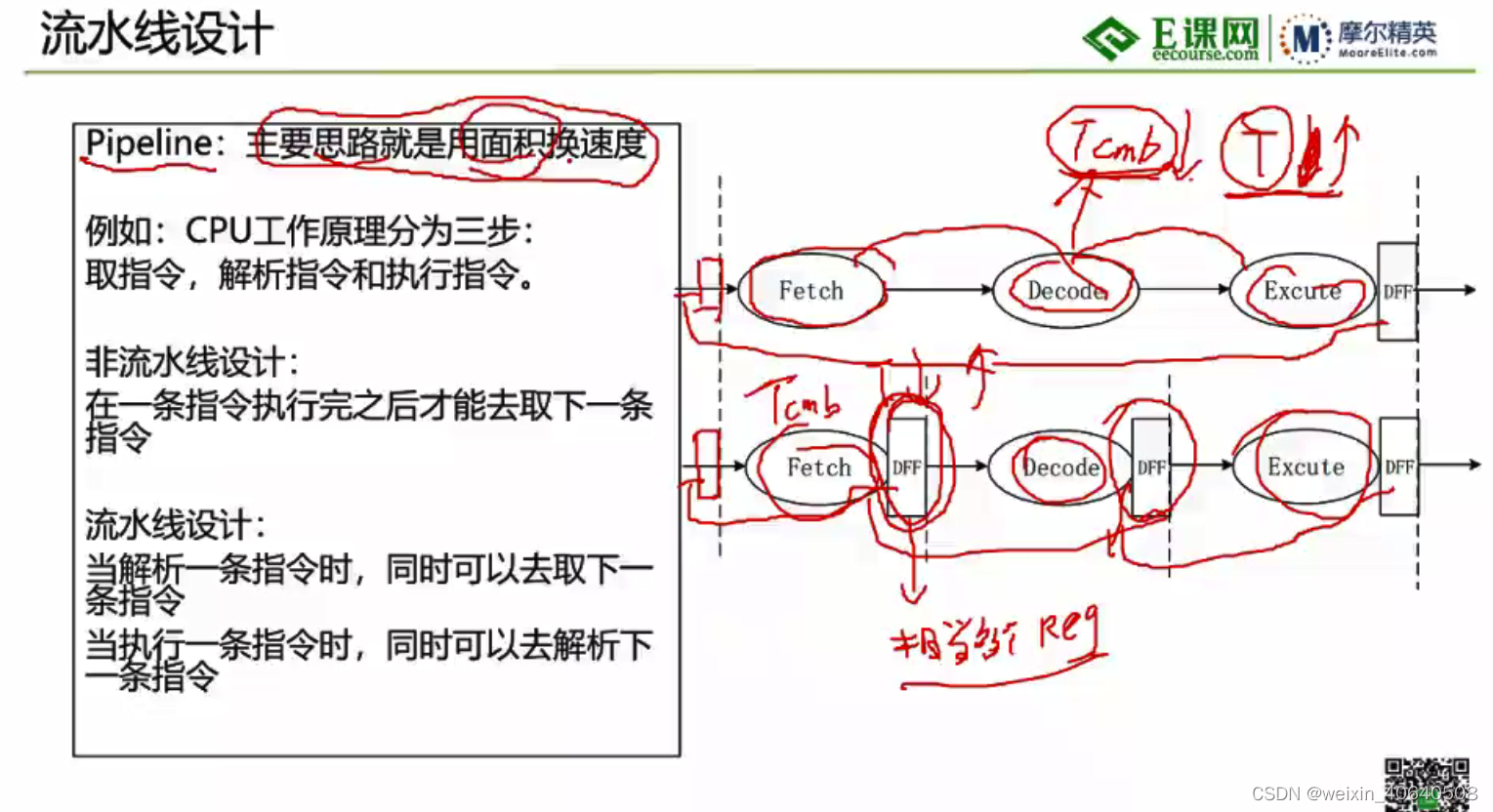

流水线传送(pipeline)

- 先是地址周期,然后是数据周期。

减少每次从decoder时间,使用burst 传输

- 先是地址周期,然后是数据周期。

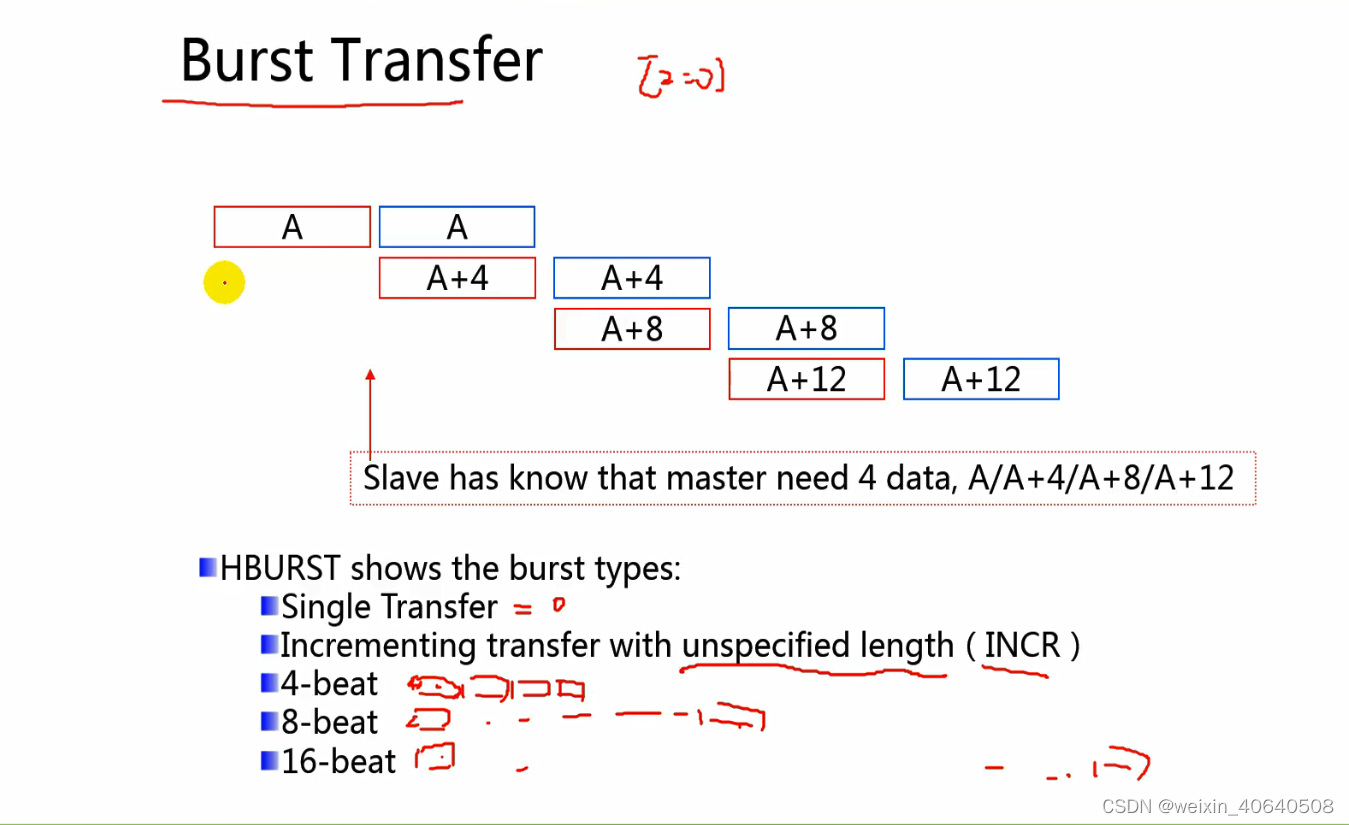

BURST传输

- AHB Burst传输

4beat、8beat、16beat、单个字节传输、未定义长度的传输

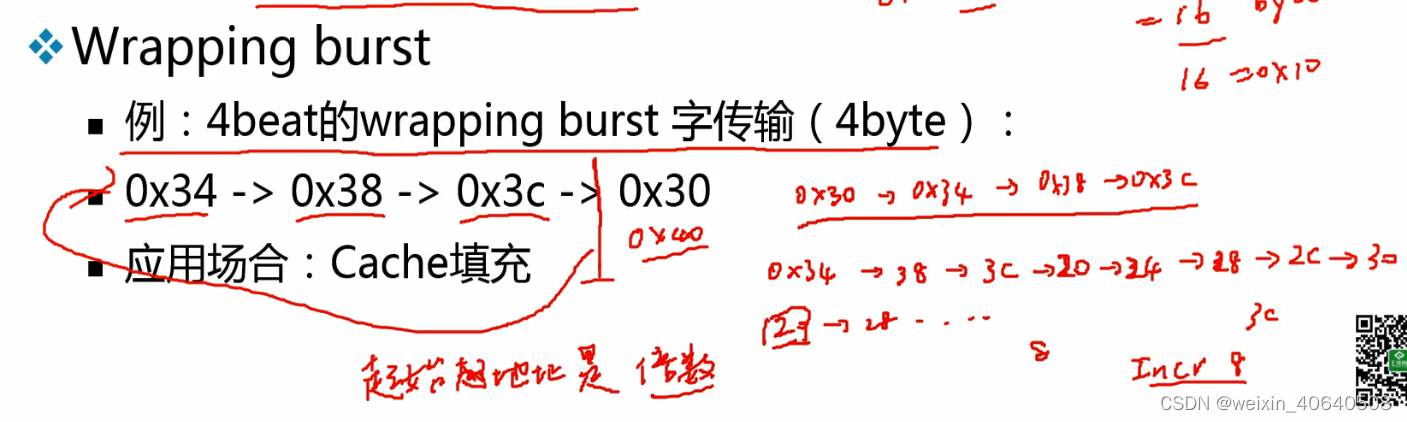

支持incrementing和wrapping两种burst传输- incrementing burst :地址是上一次的传输地址加1

- wrapping burst

- AHB总线burst不能跨越1k边界的实现

https://www.jianshu.com/p/a1be13dd82cd

地址译码

AXI总线

https://blog.csdn.net/ivy_reny/article/details/56274238

AMBA 协议支持用于主从模块间通信的高性能,高频率系统设计。

其特征是:

- 适用于高宽带、低时延设计

- 不需要复杂的桥便可实现高频时钟要求

- 满足大多数模块的接口需求

- 适用于初始延迟较高的存储器控制

- 在总线互联架构上提供更大的灵活性

- 向下兼容AHB和APB

它的几个关键特征:

- 将address/control 和 data传输通道分开

- 利用byte strobes(字节选通)支持非对齐数据传输

- 使用burst(突发)传输时只需要发送首地址,便可发送一段数据

- 读数据和写数据通道独立,从而支持low-cost(低功耗)DMA(direct memory access)

- 支持outstanding(未完成的)功能,可以发送多个地址进行读写。

- 支持out-of-order传输(乱序传输)

- 可以比较容易地添加寄存器级,以此来实现时序收敛。

注:1、outstanding传输是指不需要等待前一笔传输完成就可以发送下一笔操作,这样可以有效提升通路利用率,提升系统性能 (outstanding 未完成,发送多个地址,然后发送数据,不需要等待每次发送完下一次发送握手)

2、burst 传输可以减少地址通道的交互,提升单笔传输的效率

3、outstanding 可以减少多笔传输之间的等待,提升多笔传输的效率

SRAM

静态随机存取存储器,CPU的缓存和寄存器堆。

功耗

https://blog.csdn.net/ygyglg/article/details/105735982

低功耗设计

寄存器传输级

- 状态机编码和解码

- 二进制数表示法

- 门控时钟

- 独热码多路器

- 除掉多余的转换

- 资源共享

- 使用行波计数器来降低功耗

- 总线反转

- 高活跃度网路

- 启动和禁用逻辑云

器件

扇出:FPGA里面,是一个输出端连接/驱动的后级资源的个数,比如驱动10个LUT查找表

LUT查找表:

https://blog.csdn.net/weixin_44356019/article/details/123710924

验证分析

STA 静态时序分析

适用场景:

用于同步时钟域的分析。不能用于异步时钟。

组合逻辑:

- 竞争和冒险问题;

时序逻辑:

- (1)对于时钟和数据信号,分析setup建立时间和hold保持时间

setup建立时间:在有效的时钟沿来临前,数据需要保持稳定的最短时间,简写为Tsu,

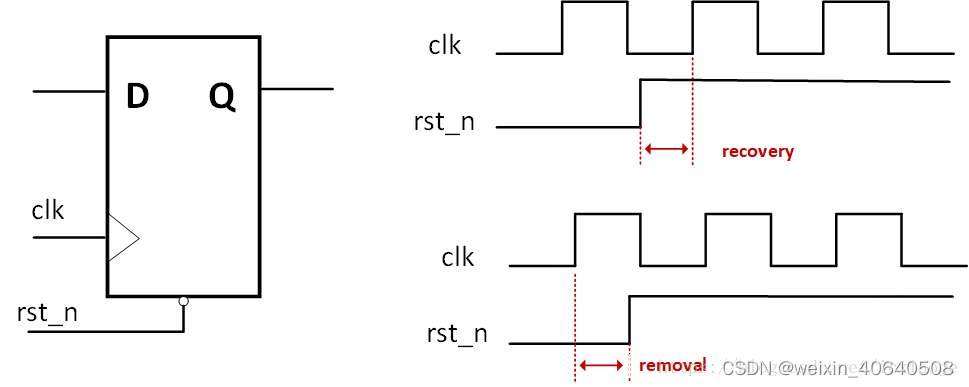

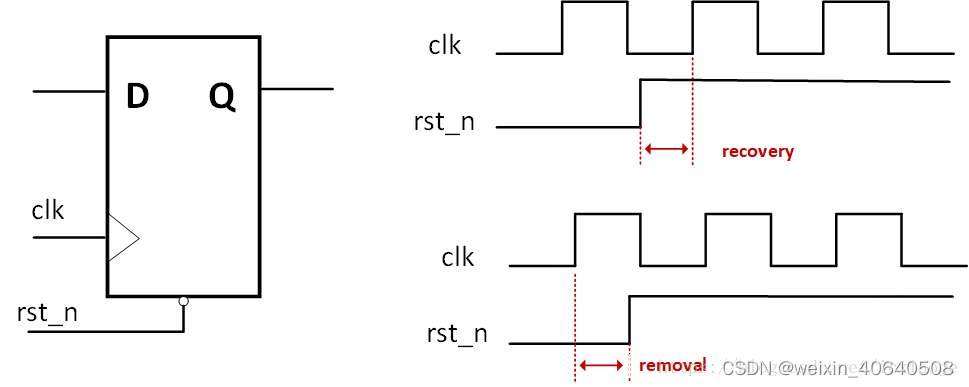

hold保持时间:在有效的时钟沿来临后,数据需要保持稳定的最短时间,简写为Th, - (2)对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recover time(恢复时间):

撤销复位时,恢复到非复位状态的电平(或者复位信号保持非复位状态的最短时间) 必须在时钟有效沿来临之前的一段时间到来,才能保证时钟能有效恢复到非复位状态,此段时间为recovery time。类似同步时钟的setup time。

removal time(去除时间):

复位时,在时钟有效沿来临之后复位信号还需要保持复位状态 的时间为取出removal time(去除时间)、类似同步时钟Hold time。

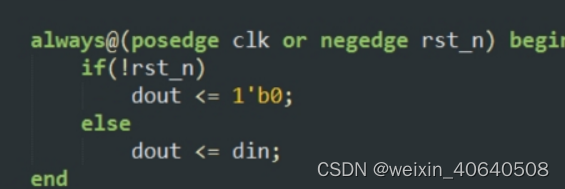

根据代码判断条件可知异步复位电路同时收到时钟信号和复位信号影响,所以要考虑这两个信号的影响。

https://www.cnblogs.com/east1203/p/11594398.html

(3)亚稳态振荡时间Tmet

亚稳态:触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态。

在这段时间里Q端在0和1之间处于震荡状态,而不是等于数据输入的D值,这段时间称为决断时间(resolution time)。

功能性验证

FIFO

FIFO(First In First Out,即先入先出),是一种数据缓冲器,用来实现数据先入先出的读写方式。

FIFO 存储器主要作为缓存,应用在同步时钟系统和异步时钟系统中,在很多的设计中都会使用;如:多比特数据做跨时钟域处理、前后带宽不同步等都用到了FIFO.

同步FIFO设计

FIFO原则:满不能些,空不能读。

关键:full和empty信号如何产生。

方法 一

异步FIFO设计

设计简介

> https://zhuanlan.zhihu.com/p/464417028

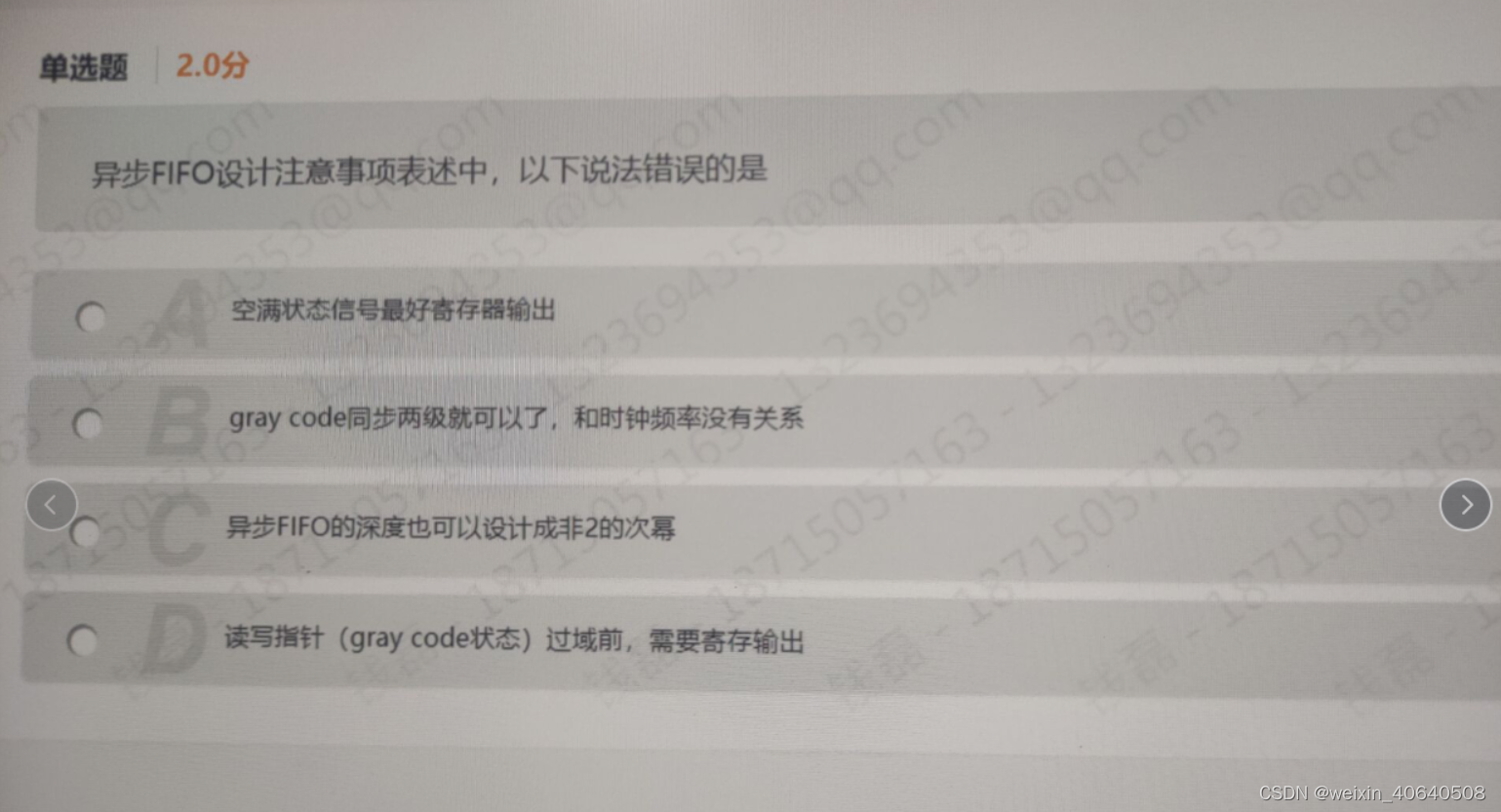

例题:

异步FIFO设计深度

异步FIFO最小深度计算

https://blog.csdn.net/qq_40483920/article/details/108233399

https://blog.csdn.net/Reborn_Lee/article/details/100127937

异步FIFO的深度也可以设计成非2的次幂

https://blog.csdn.net/re_call/article/details/114869609

-

读写指针(gray code状态)过域前,需要寄存输出

例如现在将读指针(gray code状态)跨时钟域送到写控制器需要 进行时钟同步(为了避免亚稳态出现),因为格雷码生成的是通过组合逻辑输出的,没有时钟信号,所以读指针(gray code状态)跨时钟域需要再用经过以及寄存器用来寄存输出(这样就会有一个时钟,没有时钟的话都无法出现使用跨时钟解决亚稳态方法,个人以为如果不单独拉一条时钟线过来,跨时钟解决亚稳态的时钟信号就是使用读地址(非格雷码)使用clk,中间就会忽略二进制转格雷码这段组合逻辑电路的消耗时间,造成的后果就是读指针(gray code状态)输出时间和源时钟信号的关系是不一致的,读指针(gray code状态)变化的时间电要落后源时钟信号的上升沿,这对于分析跨时钟域亚稳态是非常不利的 )如下图,跨时钟采集的写时钟(目标时钟域)clkRx上升沿不能出现在Tx的 建立时间(Tset)和保持时间段(Thold)内,如果没有寄存输出,clkTx也就不存在(你能参考的时钟就只是读指针(gray code状态)的时钟),更不清楚分析工具能不能准确分析出Tx的wave图。

竞争和冒险

出现在组合逻辑场景中

- 竞争:不同路径输入信号变化传输到同一点门级电路,时间上有先后,时间差称为竞争;

冒险:由于竞争的存在,输入信号要经过一段时间才达到期望状态,过渡时间内可能产生瞬间的错误输出,这种现象称为冒险。

冒险是在竞争的基础上产生的。 - 消除方法:

(1)增加滤波电容,滤除窄脉冲;

(2)修改逻辑增加冗余项;

(3)使用时钟同步电路,利用触发器进行拍打延迟;

(4)用格雷码计数器。(格雷码计数器的优势在于两个数值之间只有一位发生变化,提高了系统的抗干扰能力,而且在计数时,各个输出的门电路反转次数要远远小于二进制计数器,从而可以大幅度降低系统的功耗)

跨时钟域处理(CDC clock domain crossing)

https://blog.csdn.net/haojie_duan/article/details/110304907

亚稳态问题(Metastability)

出现在时序逻辑中

解决方法:

解决方法

1.降低系统时钟

2.用反应更快的FF(Flip-Flop,触发器)

2.引入同步机制,防止亚稳态传播

3.改善时钟质量,用边沿变化快速的时钟信号

关键是器件使用比较好的工艺和时钟周期的裕量要大。

https://blog.csdn.net/qq_42587251/article/details/88875409

【注】1. STA只能分析同步时序逻辑,不能分析跨时钟域

5. 时钟树综合不能修复跨时钟域问题。

解决方法就是以下几个:

单比特

两级寄存器打拍

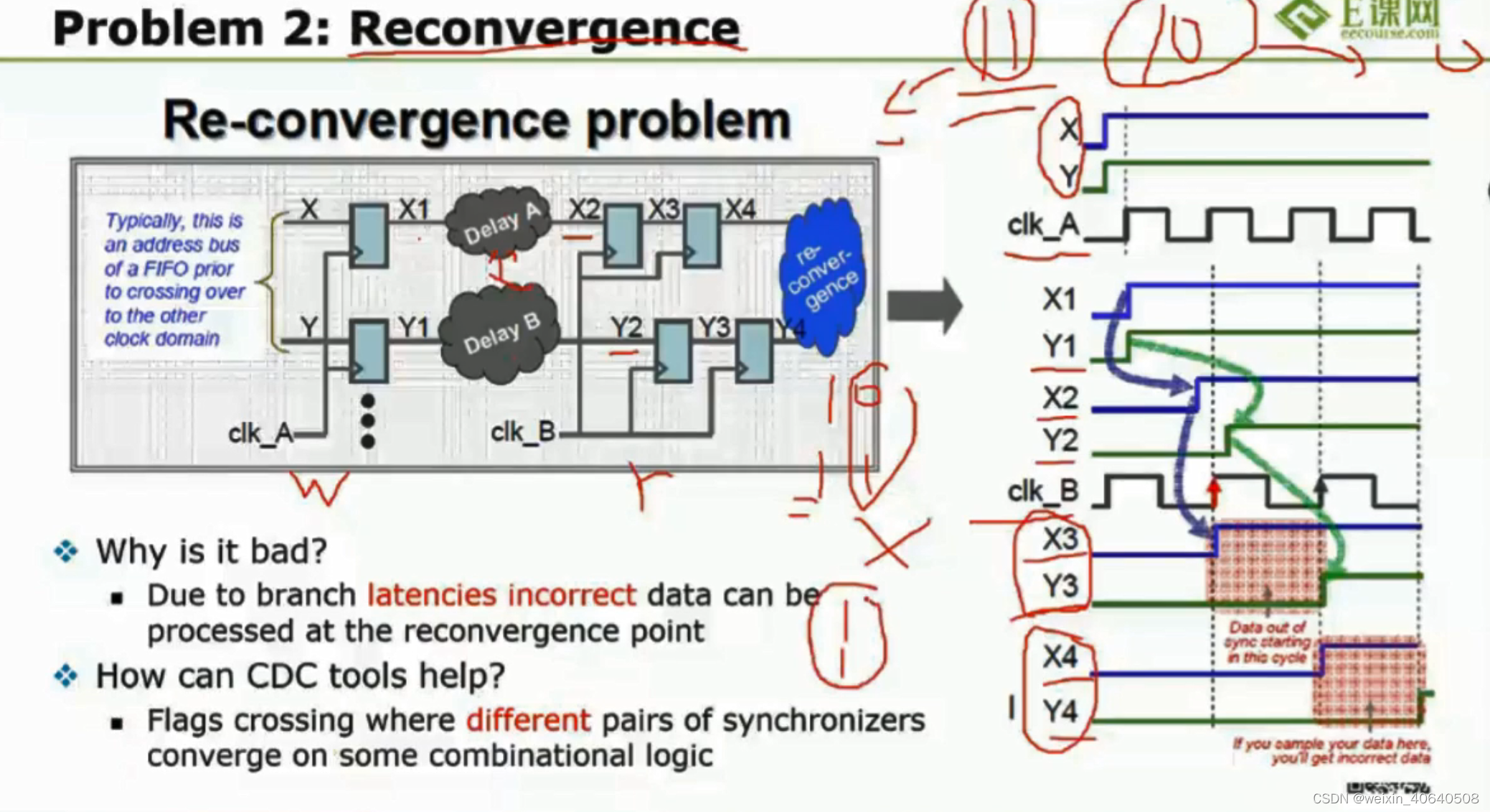

多比特(reconvergence)

多比特使用多个打拍同步会出现的问题如下:本来会出现输出市 1,1 使用多重打拍就变成了 1,0

解决办法就是用使用格雷码X和Y转成格雷码每次只有1bit发生翻转。通过源时钟打一拍,再到目的时钟打两拍同步。例如异步电路读控制

module read_part #(

parameter WIDTH_A = 8

)(

input r_clk,

input r_rst,

input r_req,

input [WIDTH_A:0] w_gaddr,

output r_empty ,

output reg[WIDTH_A:0] r_addr ,

output reg [WIDTH_A:0] r_gaddr

);

always @( posedge r_clk )

if( !r_rst )

r_addr <= 'h00;

else if( r_req&&(!r_empty) )

r_addr <= r_addr + 1'b1;

wire [WIDTH_A:0] r_gaddr_w;

bin_to_gray #(

.WIDTH_D(WIDTH_A+1)

)

bin_to_gray_inst

(

.bin_c ( r_addr ),

.gray_c( r_gaddr_w )

);

// 格雷码不直接输出,打一拍之后在送到目的时钟域做同步

always @( posedge r_clk )

if( !rst_n )

r_gaddr <= 'h0;

else

r_gaddr <= r_gaddr_w;

assign r_empty = (w_gaddr==r_gaddr_w)?1'b1:1'b0;

endmodule

data hold(快时钟域到慢时钟域)

高时钟域到低时钟域A的高电平信号(脉冲信号)叫短,到了慢时钟域就需要扩大脉冲有效时间。

使用两个触发器加一个异或门输出:(高电平有效)

Design Intent(handshake,FIFO)

handshake:

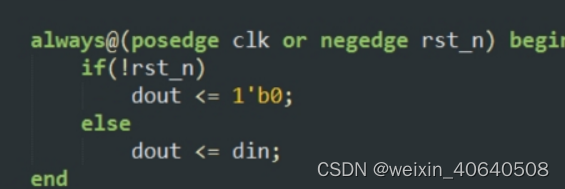

异步复位(reset Synchronization)

时序逻辑:

- (1)对于时钟和数据信号,分析setup建立时间和hold保持时间

setup建立时间:在有效的时钟沿来临前,数据需要保持稳定的最短时间,简写为Tsu,

hold保持时间:在有效的时钟沿来临后,数据需要保持稳定的最短时间,简写为Th, - (2)对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recover time(恢复时间):

撤销复位时,恢复到非复位状态的电平(或者复位信号保持非复位状态的最短时间) 必须在时钟有效沿来临之前的一段时间到来,才能保证时钟能有效恢复到非复位状态,此段时间为recovery time。类似同步时钟的setup time。

removal time(去除时间):

复位时,在时钟有效沿来临之后复位信号还需要保持复位状态 的时间为取出removal time(去除时间)、类似同步时钟Hold time。

根据代码判断条件可知异步复位电路同时收到时钟信号和复位信号影响,所以要考虑这两个信号的影响。

https://www.cnblogs.com/east1203/p/11594398.html

错误实例

SDC

设计约束文件 SDC(Synopsys design constraints)

SDC是一个设计中至关重要的一个文件。它对电路的时序,面积,功耗进行约束,它是 设计的命脉。

RAM的存储容量,以及地址线,数据线

https://blog.csdn.net/zhaominpro/article/details/82813284

https://blog.csdn.net/Dingjiawang6/article/details/72860759

低功耗设计和统一功耗格式(UPF)

https://blog.csdn.net/gsjthxy/article/details/106502908

CRC码以及校验原理

https://blog.csdn.net/lycb_gz/article/details/8201987?spm=1001.2101.3001.6650.3&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7ERate-3-8201987-blog-73330526.pc_relevant_default&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7ECTRLIST%7ERate-3-8201987-blog-73330526.pc_relevant_default&utm_relevant_index=6

综合策略与数字电路时序分析

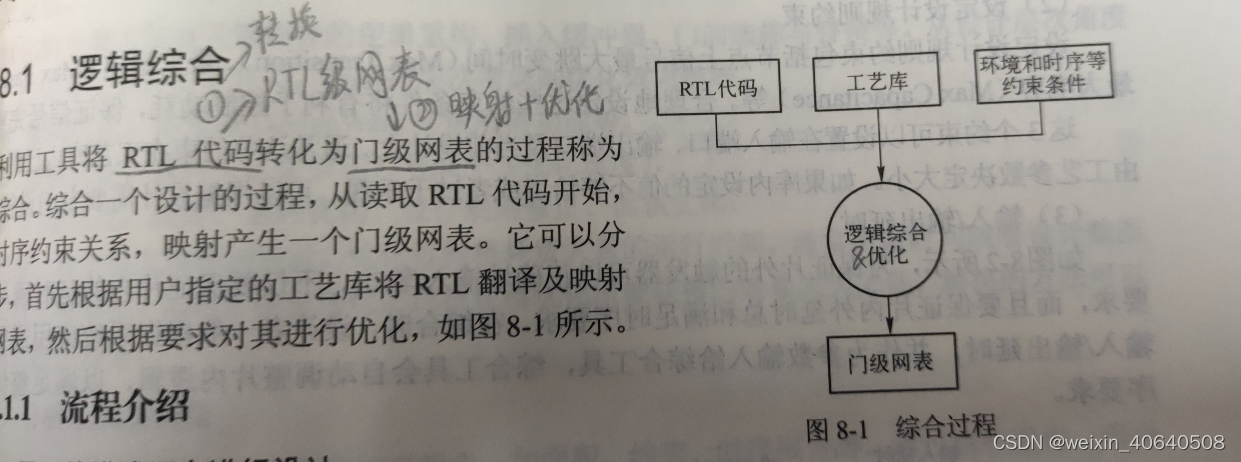

逻辑综合

逻辑综合就是将前端设计工程师编写的RTL代码,映射到特定的工艺库上,通过添加约束信息,对RTL代码进行逻辑优化,形成门级网表。

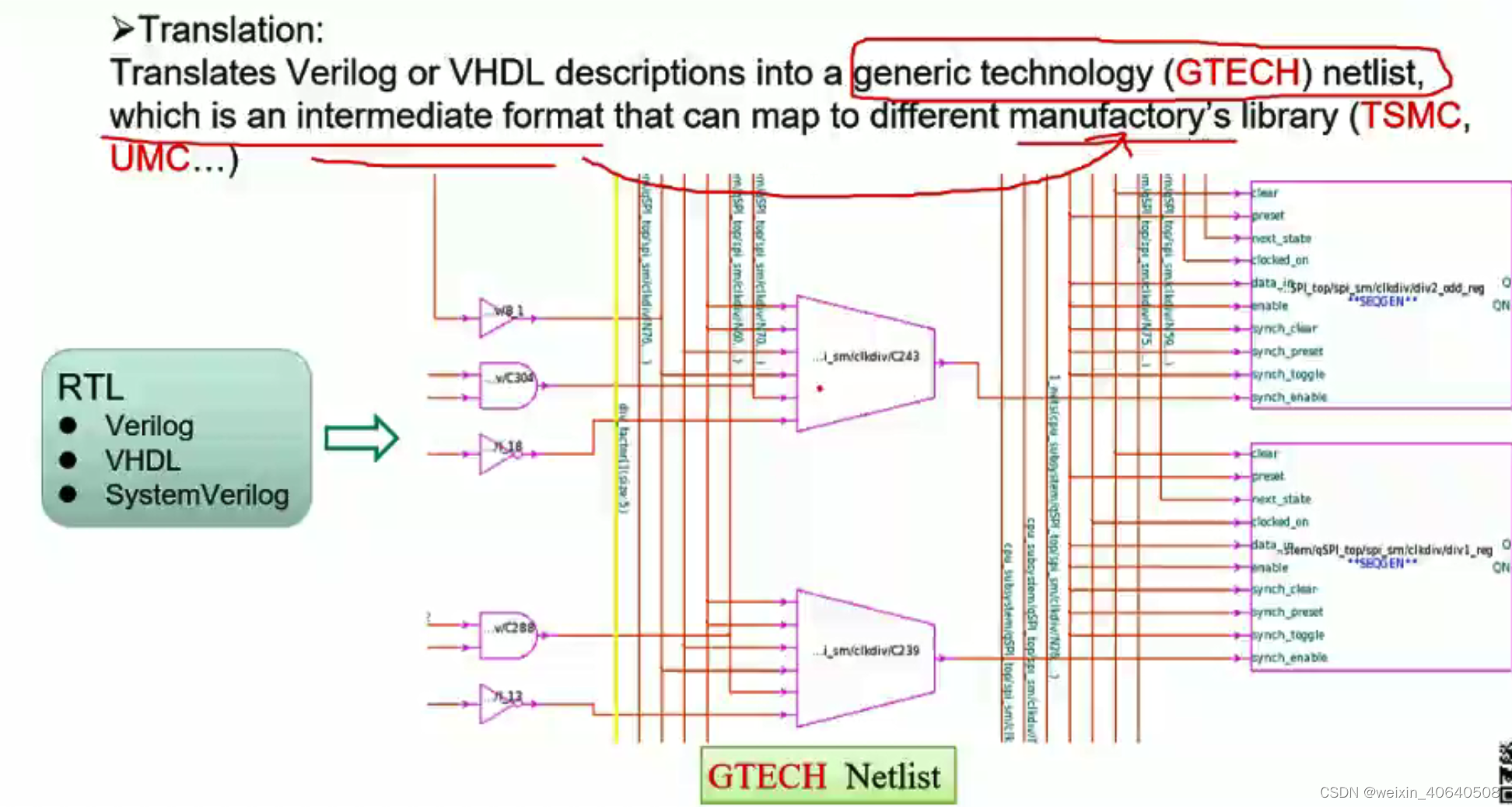

逻辑综合转换过程(translation)

先转化成generci technology netlist(GTECH),再结合工艺库(manufactory library)转化成真正的网表

Synthesis(compile) = Translation + Gate Mapping + Logic Optimization

Logic Optimization 根据给的约束信息做逻辑优化

基础

ASIC流程

组合和时序电路

锁存器Latch

什么情况下产生latch:

同步复位与异步复位

建立保持时间

建立时间分析

保持时间分析

静态时序分析

流水线设计

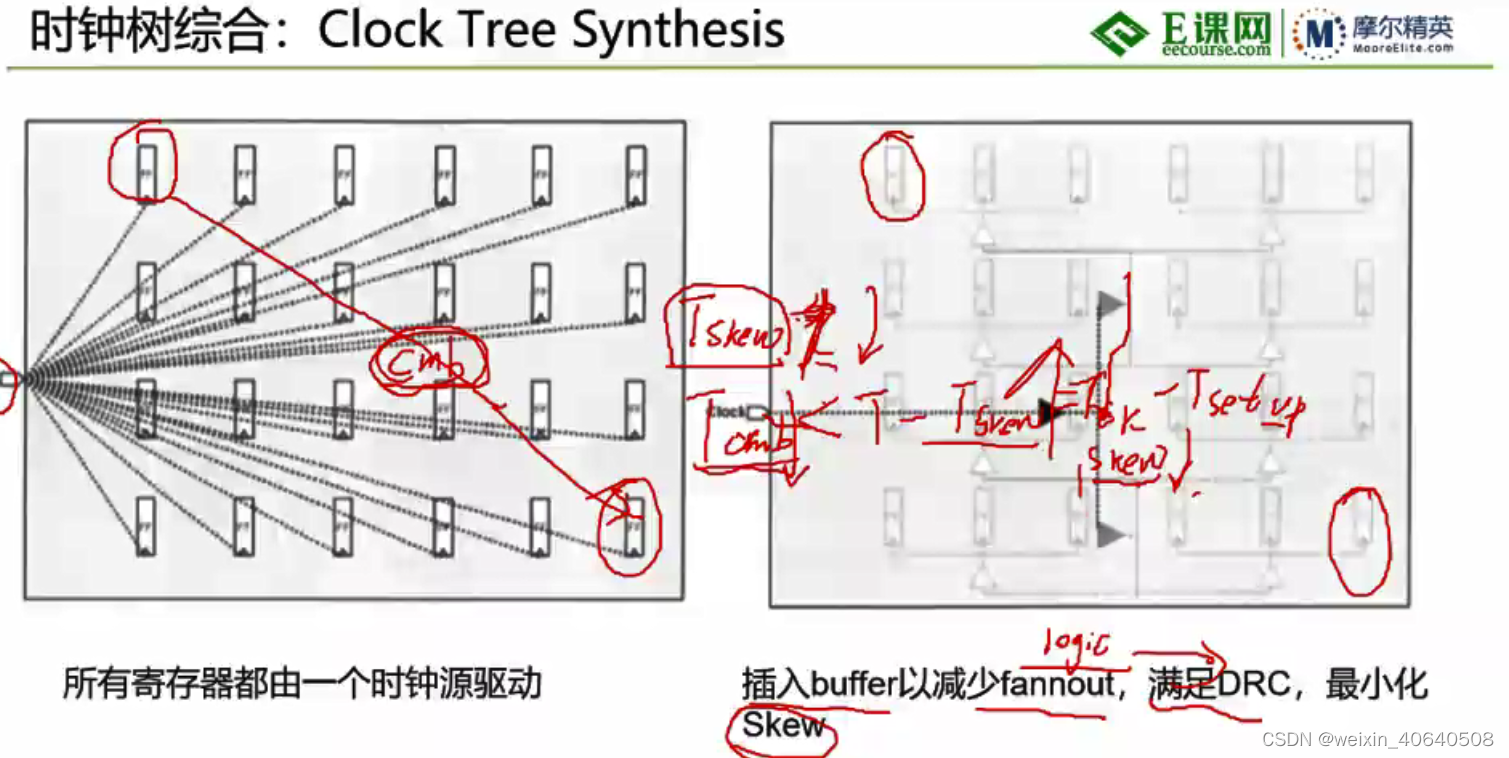

时钟树综合:Clock Tree Synthesis

目的:尽量降低Tskew。

Cell延时

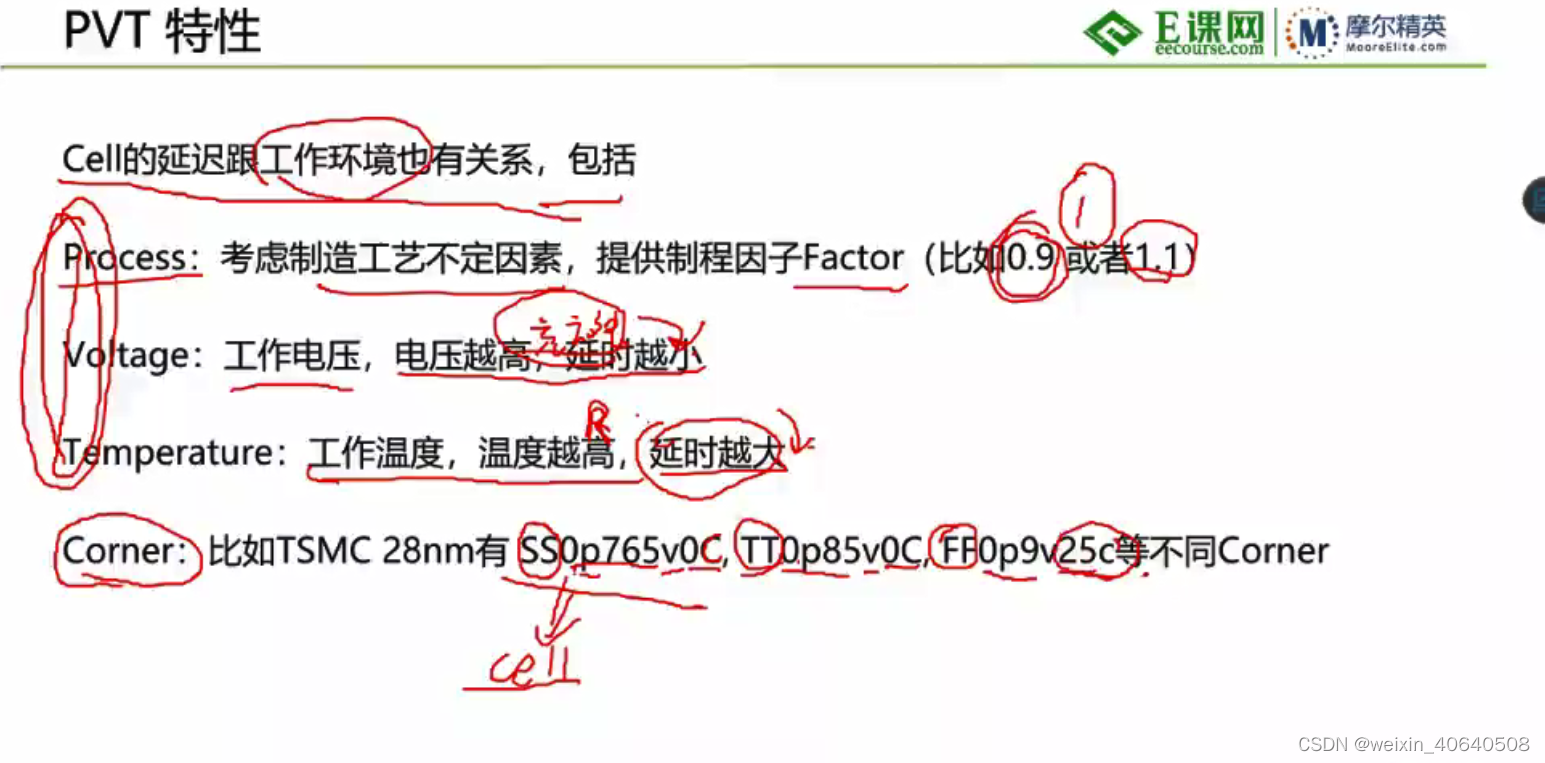

PVT特性

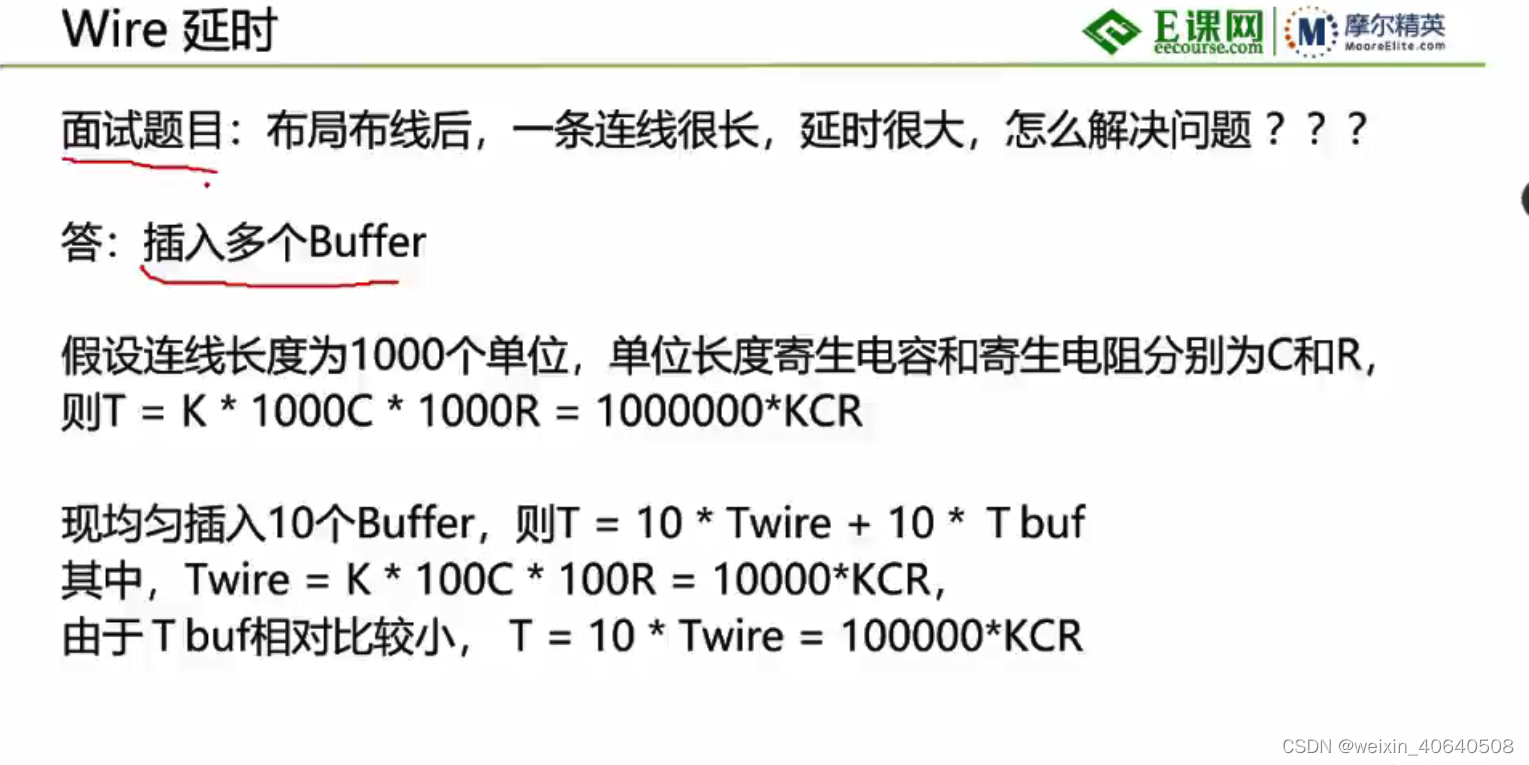

Wire延时

布局布线,加buffer打断,

课后题目

1748

1748

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?