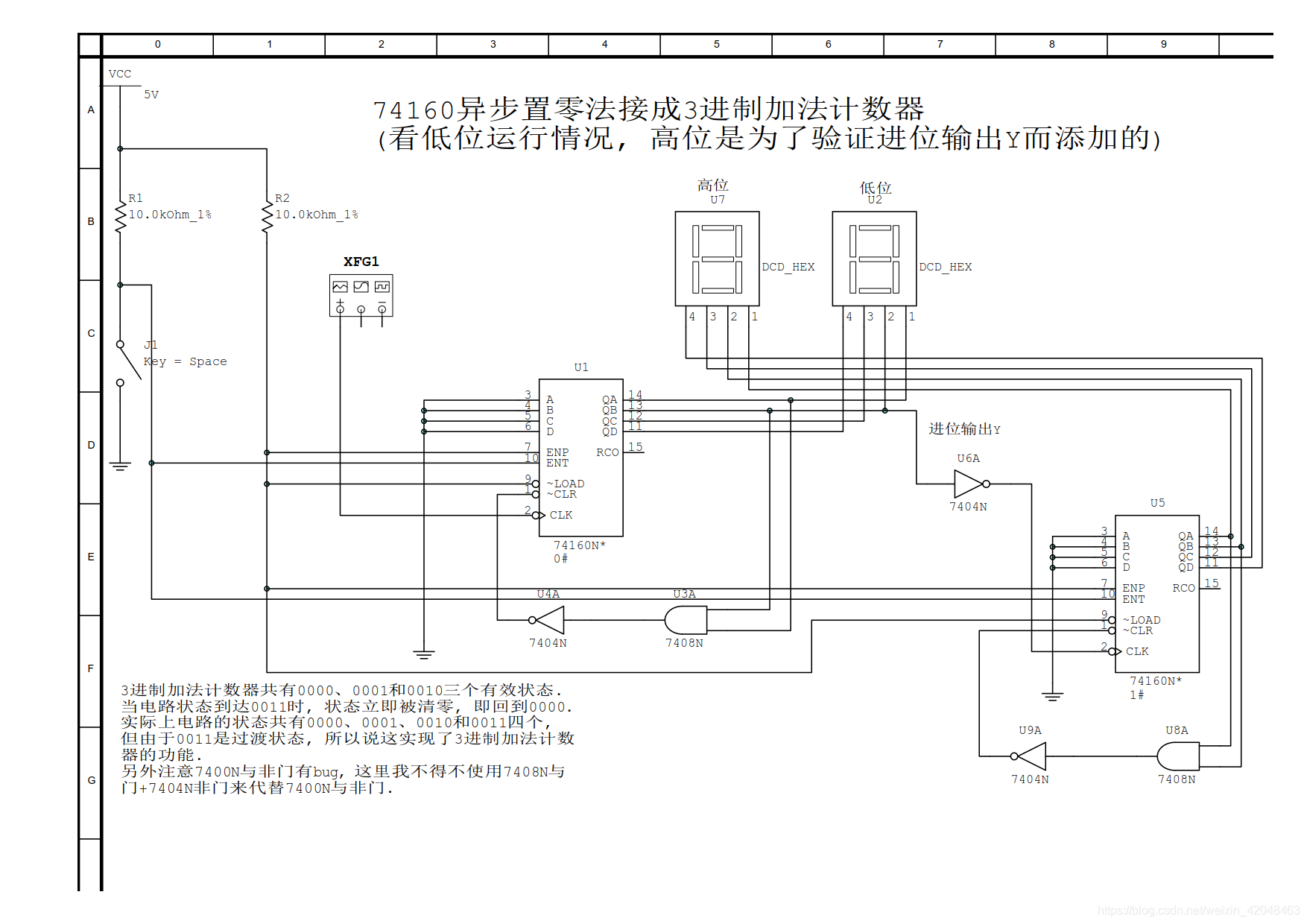

我们先来看一下电路图, 从中提取核心信息:

①QB、QA通过一级与门后再通过一级非门接到CLR引脚.

3进制加法计数器共有3个有效状态0000、0001和0010, 而电路状态到达0011时, CLR引脚立即变为低电平, 电路状态清零, 即变为0000, 而后CLR引脚又恢复高电平, 计数器继续计数. 0011其实是一个过渡状态, 不算在有效状态之类. 故接成的电路实现了3进制加法计数器的功能.

②电路的状态是如何变化的.

0000 —> 0001 —> 0010 ---> 0011(一闪而过) ---> 0000.

③进位输出Y为何这样设计.

(对比⑧来学习)

直接将QB作为进位输出Y即可. 如此一来, 电路状态和进位输出Y的关系为 0000(Y=0) —> 0001(Y=0) —> 0010(Y=1) ---> 0011(Y=1) ---> 0000(Y=0): 通过一级非门接到高位74160的CLK引脚后, 在0011->0000时实现了一次上升沿的过程.

值得说明一下的是, multisim7中74160芯片的触发方式为上升沿触发: 虽然CLK引脚处有小圆圈, 理论上应该为下降沿触发, 但经过大量实验后验证, 其触发方式的确为上升沿触发. multisim7中有一些芯片的触发方式确实和直观表达(是否带小圆圈)的不同, 这一点不必过多纠结.

④低位对高位的进位是如何实现的.

我们先来看一下电路的状态和进位输出Y的关系: 0000(Y=0) —> 0001(Y=0) —> 0010(Y=0) ---> 0011(Y=1) ---> 0000(

本文通过电路图解析74160如何实现异步清零,以三进制加法计数器为例,阐述了电路状态变化、进位输出设计、低位对高位进位的实现以及74160的LOAD引脚在设计中的作用。同时探讨了在multisim7软件中74160芯片的触发方式和与非门替代方案。

本文通过电路图解析74160如何实现异步清零,以三进制加法计数器为例,阐述了电路状态变化、进位输出设计、低位对高位进位的实现以及74160的LOAD引脚在设计中的作用。同时探讨了在multisim7软件中74160芯片的触发方式和与非门替代方案。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?