计数器清零就是将计数值清零

计数器的异步清零就是不顾时钟信号,只要清零信号来到就进行清零操作

计数器的同步清零就是即使清零信号有效也要等时钟信号有效沿到来才能清零

module counter(

clk, //时钟信号

rst_n, //复位信号

clr, //

cnt_value //计数输出

);

input clk;

input en; //使能

input rst_n;

input clr;//清零信号

output [3:0]cnt_value;

reg [3:0]cnt;

always @(posedge clk)//同步清零

//always @(posedge clk or posedge clr) //异步清零

if(!rst_n)

cnt<=4'b0;

else if(en) begin

cnt <=cnt +1'b1;

end

assign cnt_value =cnt;

endmodule

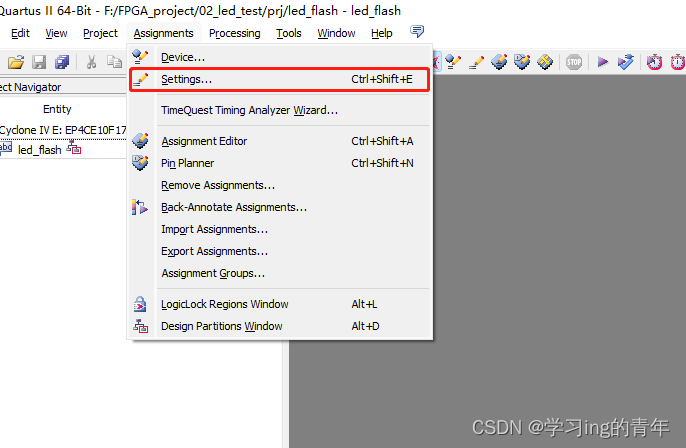

设置顶层文件:

2164

2164

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?