前言:

经常在面试中,面试官会问你谈谈uvm整个的认识,整个的构建。其实面试官应该是想问uvm整个层次的构建。

1、uvm的组件

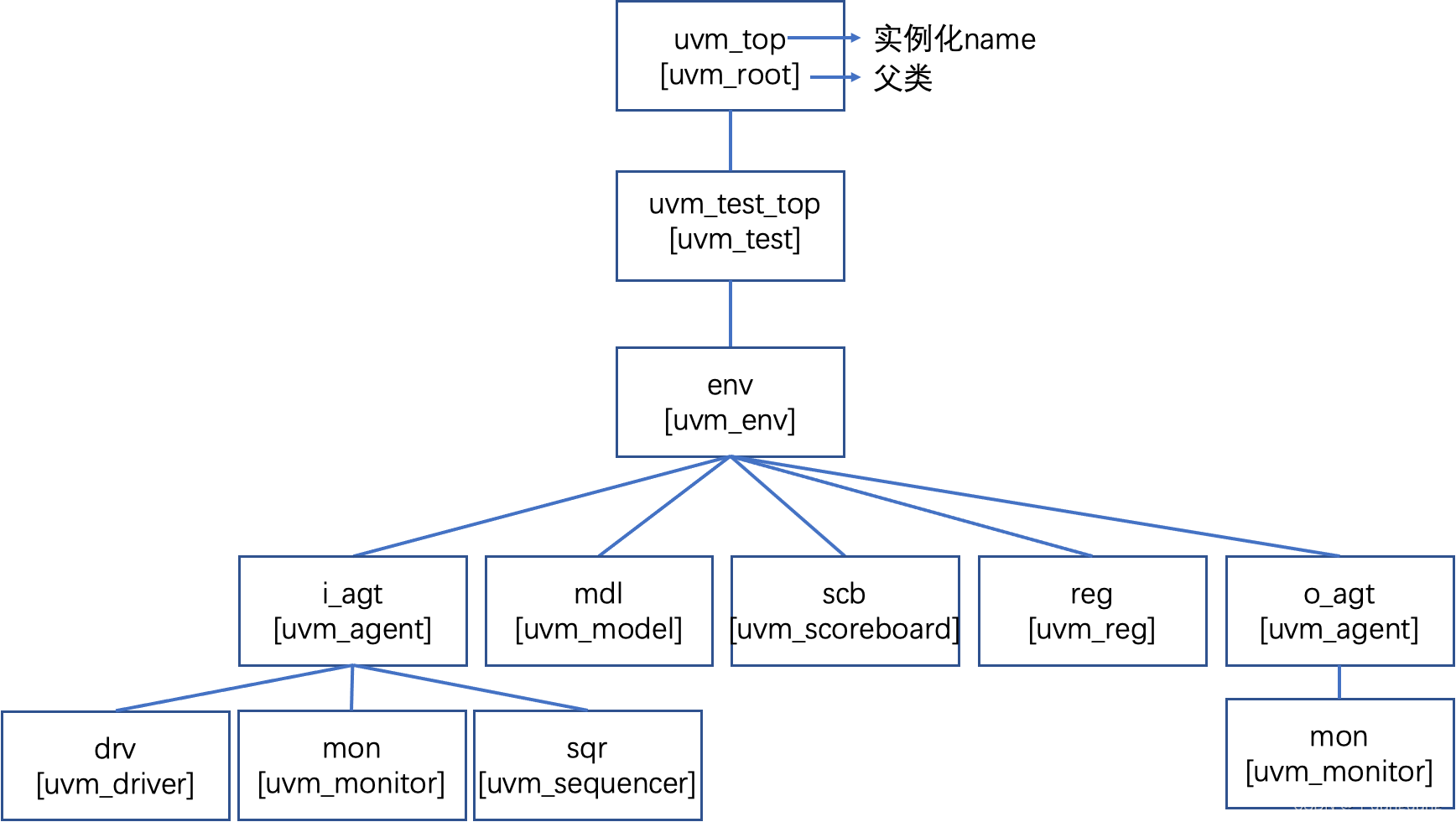

整个uvm构成主要包含uvm_component与uvm_object。

uvm_component因为在创建时有两个参数:name与parent,因此uvm_component具有一个层次关系,它构成验证环境。uvm_root唯一实例为uvm_top,为整个uvm的根。要求在build_phase阶段完成创建(自顶向下:建立了根才能逐渐向底层创建)。

uvm_object创建时的参数只有一个:name。没有层次关系。它作为环境的事务或配置。它可以在整个环境的任何阶段创建。

通过选择运行相应name的case,例化相应case中的环境env,逐渐向底层建立。

i_agt:仅仅作为将driver、monitor与sequencer封装。

mdl:参考模型为模拟硬件的行为,将模拟出的数据与o_agt中监测到的DUT发出的数据发送到scb,进行对比,若出现错误,说明DUT运行不正常。

reg:寄存器模型,是硬件与硬件、硬件与软件的一个交互模式。通过读寄存器可以得知硬件目前的状态,通过写寄存器,对硬件的行为进行配置。

2、运行过程

事务transcation以item的形式在sequence中产生, sequence将item发送给sequencer,等待driver向sequencer索取item(get_next_item信号发出后sequencer开始仲裁(按照一定的仲裁机制进行仲裁,决定将哪个item发送给driver)),driver将数据按照与DUT物理协议时序关系驱动到接口上(接口通过config_db 传递virtual interface)。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?