小数分频原理

在没有数字锁相环的情况下,要实现小数分频的方法是:

先设计两个不同分频比的整数分频器,然后通过控制两种分频比出现的不同次数来获得所需的小数分频值,从而实现平均意义上的小数分频。

假设我们需要进行5.3分频,那么5.3可以写为53/10,因为:

53/10=5…3

商为5,余数为3

那么我们就可以通过5(商)分频和8(商+余数)来实现5.3分频。

现在我们来确定5分频和8分频的次数,设5分频的次数为a,8分频的次数为b;

那么应该有:

a+b=10(除数)

5a+8b = 53(被除数)

解得a=9,b=1,也就是说通过9次5分频和1次8分频可得到5.3分频。

下面我们直接来看Verilog程序。

Verilog源代码

module fdiv5_3(clk_in,rst,clk_out);

input clk_in,rst;

output reg clk_out;

reg [3:0] cnt1,cnt2;

always @(posedge clk_in or posedge rst)

begin

if(rst)

begin

cnt1<=0;

cnt2<=0;

clk_out<=0;

end

else if(cnt1<9) //9次5分频,9=a;

begin

if(cnt2<4) //5

begin

cnt2<=cnt2+1;

clk_out<=0;

end

else

begin

cnt2<=0;

cnt1<=cnt1+1;

clk_out<=1;

end

end

else

begin

if(cnt2<7) //1次8分频

begin

cnt2<=cnt2+1;

clk_out<=0;

end

else

begin

cnt2<=0;

cnt1<=0;

clk_out<=1;

end

end

end

endmodule相对应的testbench如下:

testbench

initial

begin

clk_in=0;

rst=0;

#5000 $stop;

$display("Running testbench");

end

always

begin

#5 clk_in=~clk_in;

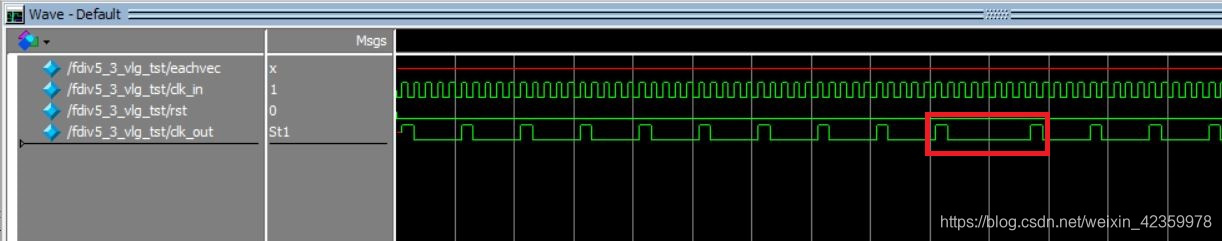

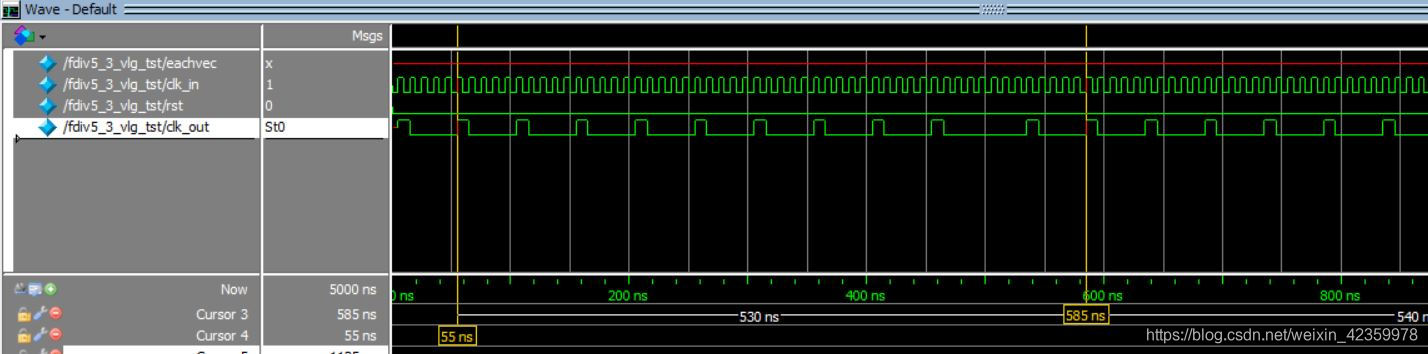

end modelsim仿真波形

从最后的仿真波形可以看到前面9次分频与第10次分频的周期不同,在testbench中设定输入的时钟信号clk_in的周期是10ns,经过5.3分频后,输出信号clk_out的10个周期所占的时间应为53ns。

若文档有任何错误或不足,欢迎在博客下方留言指正;

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?