多异步时钟设计(2)

4.0 传送多个信号

在时钟域之间传递多个信号时,简单的同步器不能保证数据的安全传送。

工程师在处理多时钟设计时经常犯的错误是将同一事件中所需的多个CDC位从一个时钟域传递到另一个时钟域,并忽略了CDC位同步采样的重要性。

问题在于,与一个时钟同步的多个信号将经历小数据改变偏斜,这些偏斜偶尔可以在第二时钟域中的不同上升时钟边沿上采样。 即使我们能够完美地控制和匹配多个信号的走线长度,上升和下降时间的差异以及芯片上的工艺变化也可能引入足够的歪斜,也会导致在其他精心匹配的走线上出现采样失败。

必须采用多位CDC策略以避免多位值的偏斜采样。

4.1 多个CDC信号分类

为避免多位CDC偏斜采样情况,将多个CDC信号分为三大类:

(1)多位信号合并。 在可能的情况下,将多个CDC位合并为1位CDC信号。

(2)多循环路径配方。 使用同步加载信号安全地传递多个CDC位。

(3)使用格雷码传递多个CDC位。

4.2 多位信号合并

在可能的情况下,将多个CDC信号合并为1位CDC信号。

简单地在所有CDC位上使用同步器并不总是足够好,如以下示例所示。

如果控制信号的顺序或对齐很重要,则必须注意将信号正确地传递到新的时钟域。

本节中显示的所有示例都过于简单,但它们非常类似于真实设计中经常出现的情况

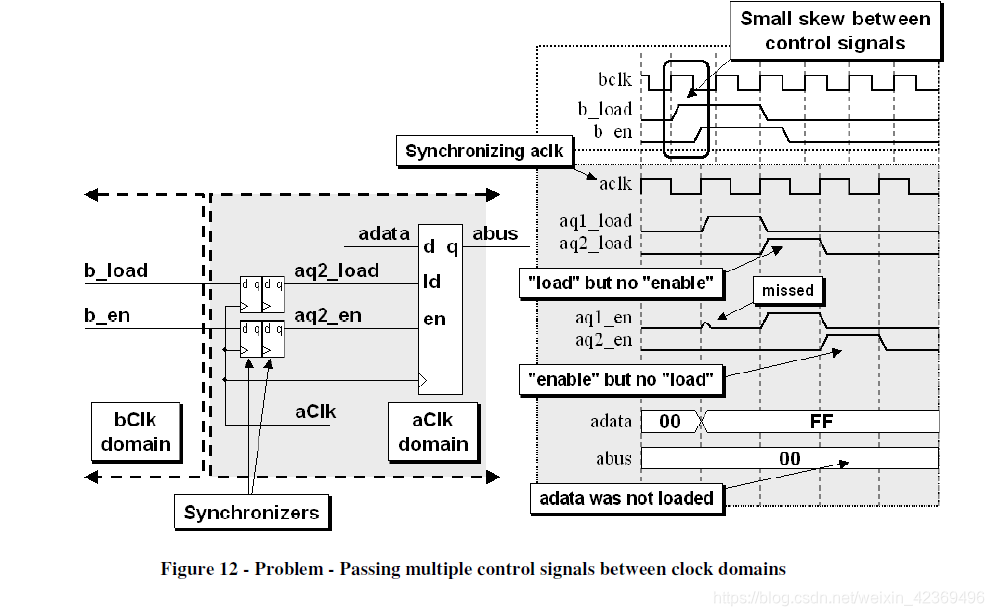

4.2.1 problem - 两个需要同时控制的信号

在图12所示的简单示例中,接收时钟域中的寄存器需要加载信号和使能信号,以便将数据值加载到寄存器中。 如果在相同的发送时钟边沿上驱动加载和使能信号,则控制信号之间的小偏斜可能导致两个信号在接收时钟域内被同步到不同的时钟周期。 在这些条件下,数据不会加载到寄存器中。

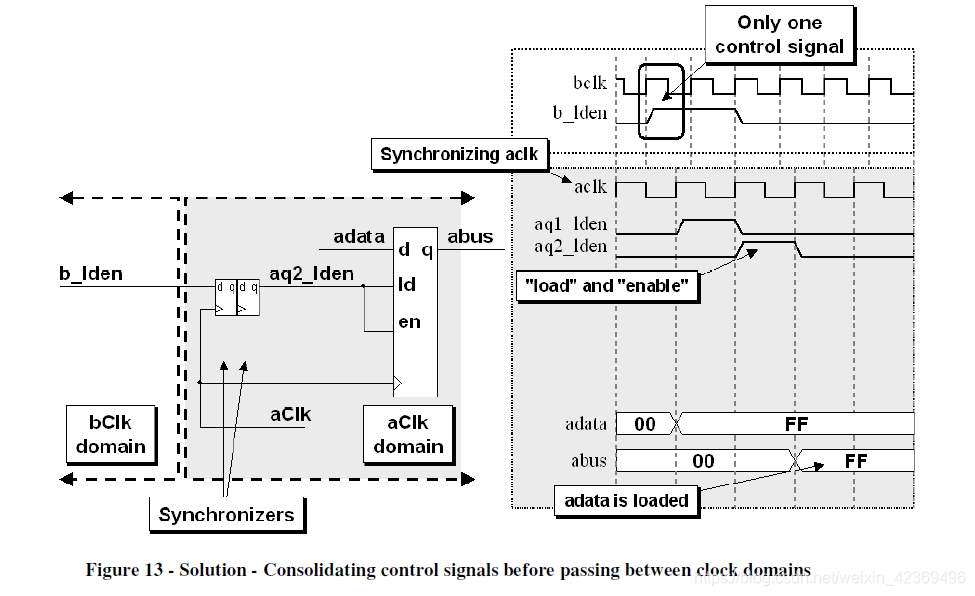

4.2.1.2 Solution - Consolidation(合并)

第4.3节中的问题解决方案很简单,巩固了控制信号。 如图13所示,仅从一个负载使能信号驱动接收时钟域中的负载和使能寄存器输入信号。 合并将消除两个控制信号在时间上移位的可能性。

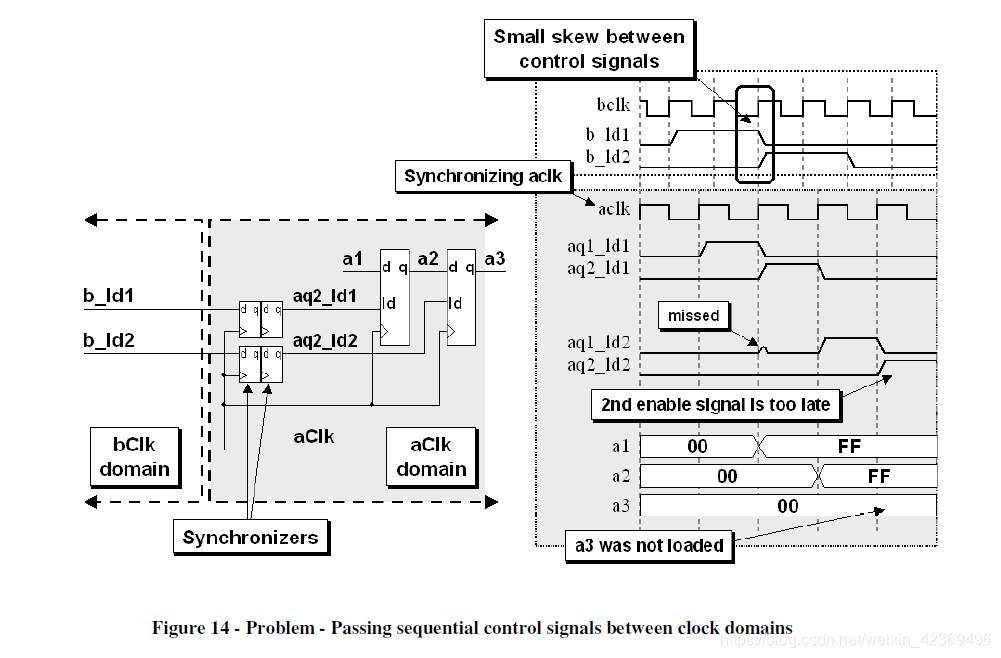

4.2.2 Problem - 两个相移序列控制信号

图14中的图表显示了两个使能信号aen1和aen2,它们从发送时钟域顺序驱动到接收时钟域,以控制流水线数据寄存器的使能输入。 问题是在第一个时钟域中,aen1控制信号可能在产生aen2控制信号之前稍微终止,并且接收时钟的上升沿可能发生在aen1和aen2控制信号脉冲之间的微小间隙中,从而导致 在接收时钟域的使能控制信号链中形成一个周期间隙。 这将导致第二个寄存器错过a2数据值。

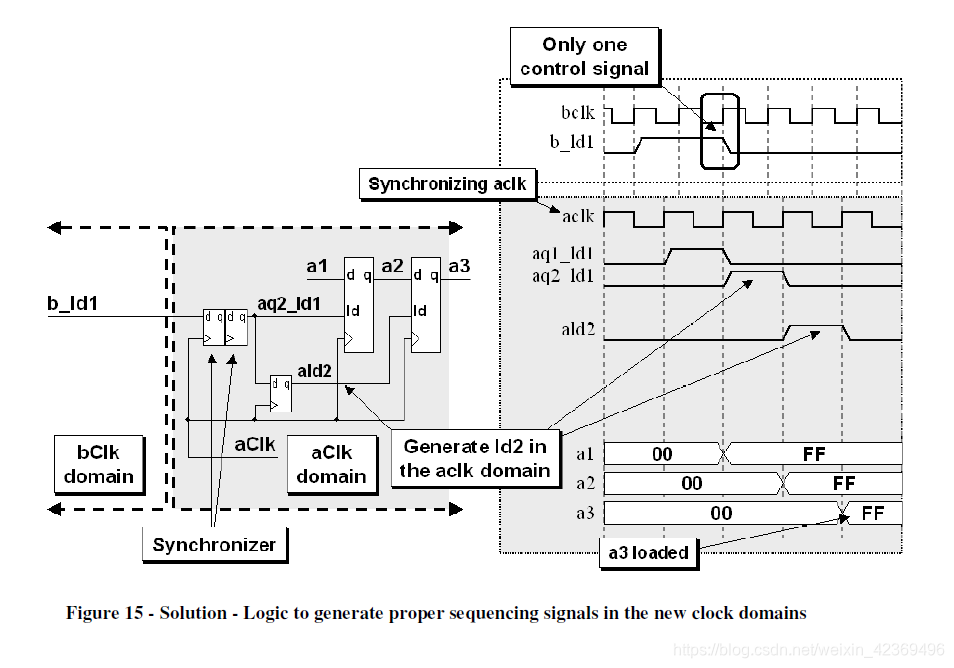

4.2.2.1 Solution - 合并并增加一个额外的触发器

该问题的解决方案,如图15所示,是仅将一个控制信号发送到接收时钟域,并在接收时钟域内产生第二个相移流水线使能信号。

4.3 多循环路径(MCP)公式

4.3.1 Problem - 多个CDC信号

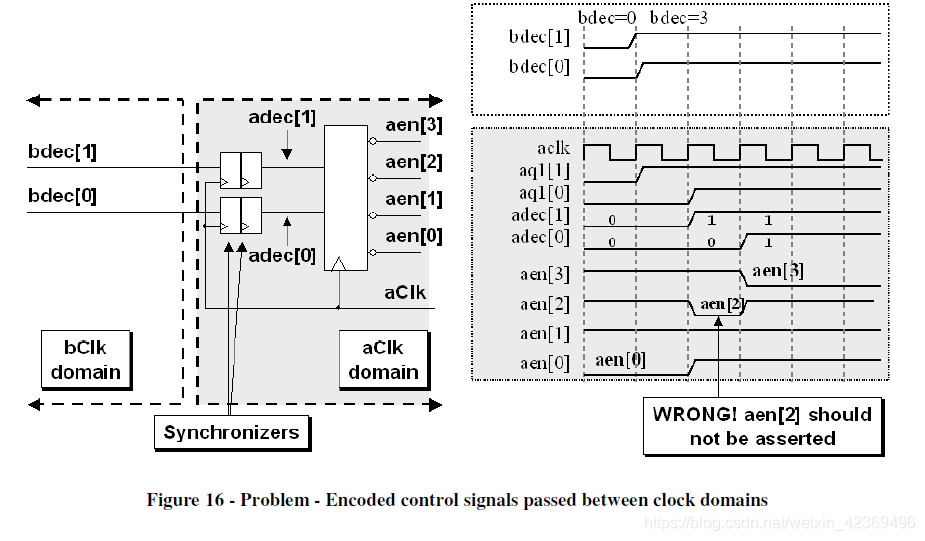

图16中的图表显示了在时钟域之间传递的两个编码控制信号。 如果两个编码信号在采样时稍微偏斜,则可以在接收时钟域中的一个时钟周期产生错误的解码输出。

4.3.1.1 Solutions for passing multiple CDC signals

多循环路径(MCP)公式和FIFO技术可用于解决与传递多个CDC信号相关的问题。 MCP的描述和定义在5.3节中给出

至少有两种多循环路径(MCP)公式可用于解决此问题:

(1)闭环 - 具有反馈的MCP配方。

(2)闭环 - 具有确认反馈的MCP配方。

还有至少两个FIFO策略作为此问题的闭环解决方案:

(1)异步FIFO实现。

(2)2-depth FIFO实现。

FIFO实现技术从5.5节开始描述。

4.3.2 多循环路径(MCP)公式??

使用MCP公式是安全传递多个CDC信号的常用技术。

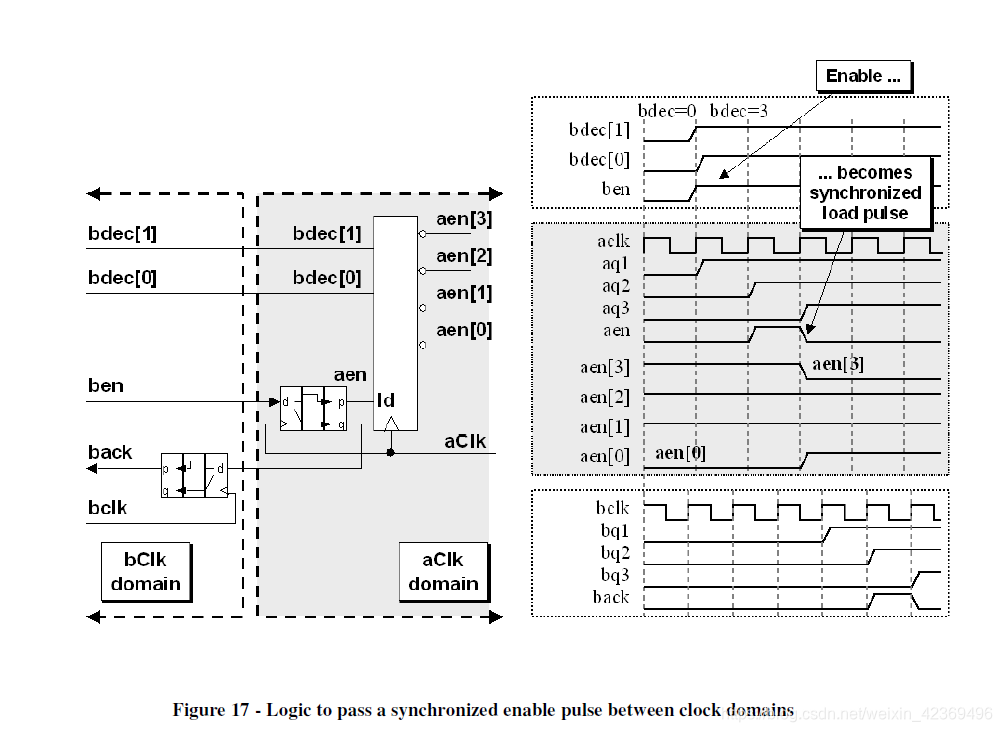

MCP公式是指将非同步数据发送到与同步控制信号配对的接收时钟域。同时发送数据和控制信号,允许数据在目标寄存器的输入上设置,同时控制信号在到达目标寄存器的加载输入之前被同步两个接收时钟周期。

优点:

(1)发送时钟域不需要计算在时钟域之间发送的适当脉冲宽度。

(2)发送时钟域仅需要将使能切换到接收时钟域以指示数据已经通过并准备加载。使能信号不需要返回其初始逻辑电平。

该策略在没有同步的情况下传递多个CDC信号,并同时将同步的使能信号传递到接收时钟域。不允许接收时钟域对多位CDC信号进行采样,直到同步使能通过同步并到达接收寄存器。

这种策略称为多周期路径公式,因为非同步数据字直接传递到接收时钟域并保持多个接收时钟周期,允许使能信号同步并识别到接收 允许非同步数据字改变之前的时钟域。

由于非同步数据在采样之前传递并保持稳定多个时钟周期,因此采样值不会变为亚稳态。

4.3.2.1 MCP方法使用同步使能脉冲

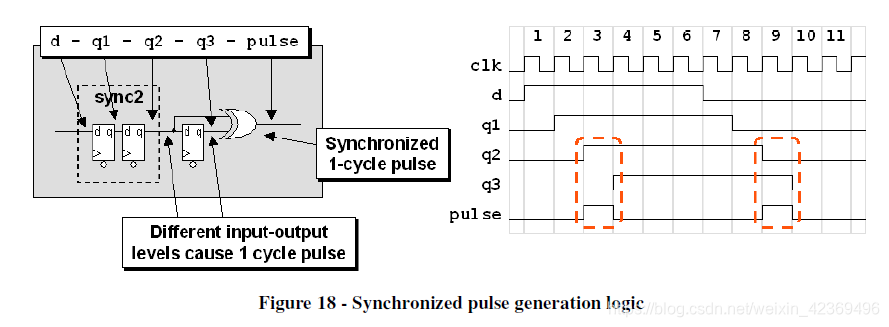

在时钟域之间传递同步使能信号的最常用方法可能是采用切换使能信号,该信号传递给同步脉冲发生器,以指示可以在下一个接收时钟边沿捕获非同步多周期数据字,如图所示在图18中。

这种同步使能脉冲产生的一个关键特征是输入信号的极性无关紧要。在图18中,d输入在周期1中切换为高,并且在周期4中,高信号已经通过三个同步触发器传播。在周期3中,q2和q3触发器的输出具有不同的极性,导致同步使能脉冲在同一周期中在异或门的输出上形成。类似地,d-输入在周期7中切换为低,并且在周期10中,高信号已经通过三个同步触发器传播。并且在周期9中,q2和q3触发器的输出具有不同的极性,导致同步使能脉冲形成在异或门的输出上。

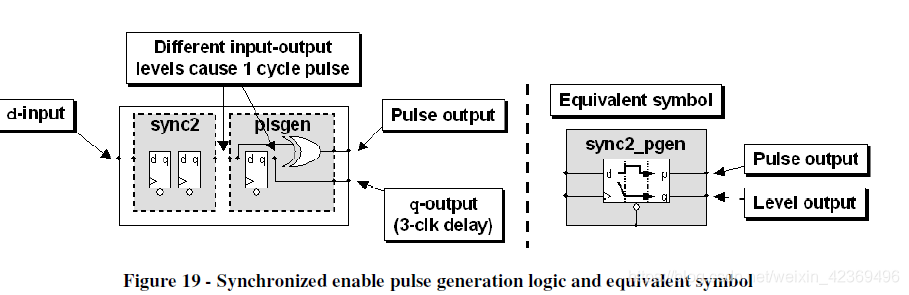

由于4.0节中描述的所有MCP配方都使用同步使能脉冲发生电路,因此认为创建和使用较小的等效符号来表示同步使能脉冲发生电路是有用的。 等效符号如图19所示。

除了产生任何d输入极性的脉冲之外,同步使能脉冲发生电路还具有q输出,该q输出跟随延迟三个时钟周期的d输入。 q输出经常用作反馈信号,并作为确认信号通过发送时钟域中的另一个同步使能脉冲发生电路。

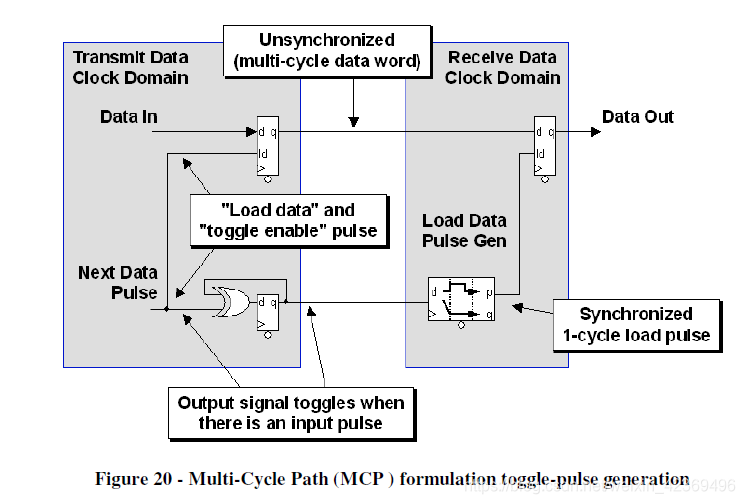

图20显示了典型的发送 - 接收切换脉冲生成设计。

使用这种技术,要求接收时钟域具有适当的逻辑以在检测到脉冲时捕获数据,因为脉冲仅对每个多周期数据字的一个接收时钟周期有效。

4.3.2.2 闭环 - 具有反馈的MCP公式

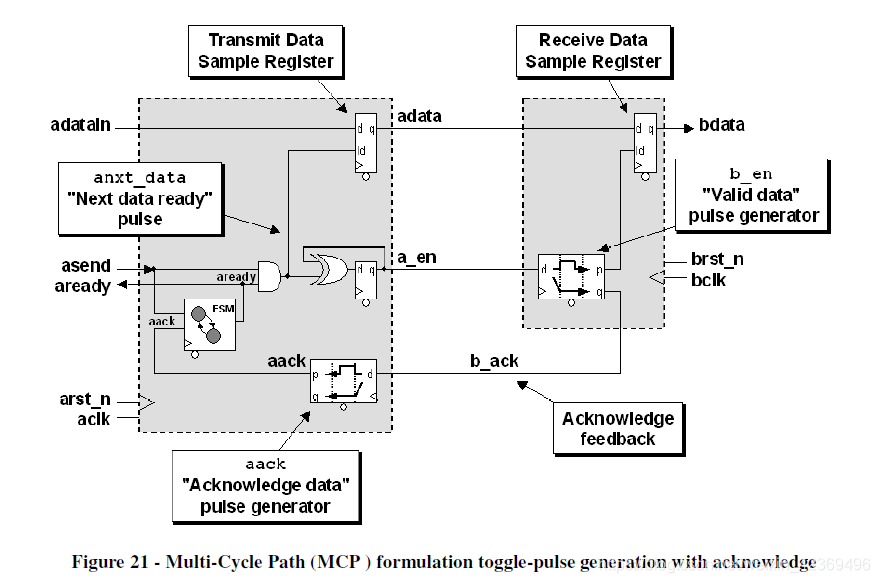

使用MCP公式时的一个重要技术是将使能信号作为确认信号传递回发送时钟域,如图21所示。

对于图21中的示例,确认反馈信号(b_ack)生成一个确认脉冲(aack),用作小型READY-BUSY,1态FSM模块的输入,该模块生成就绪信号(aready)以指示 现在可以安全地再次更改数据输入(adatain)值。 一旦信号变高,发送方就可以自由发送新数据(adatain)和随附的asend控制信号。

这是一个自动反馈路径,假设接收时钟域将始终为通过MCP公式同步的下一个数据字做好准备。

4.3.2.3 闭环 - 具有确认反馈的MCP

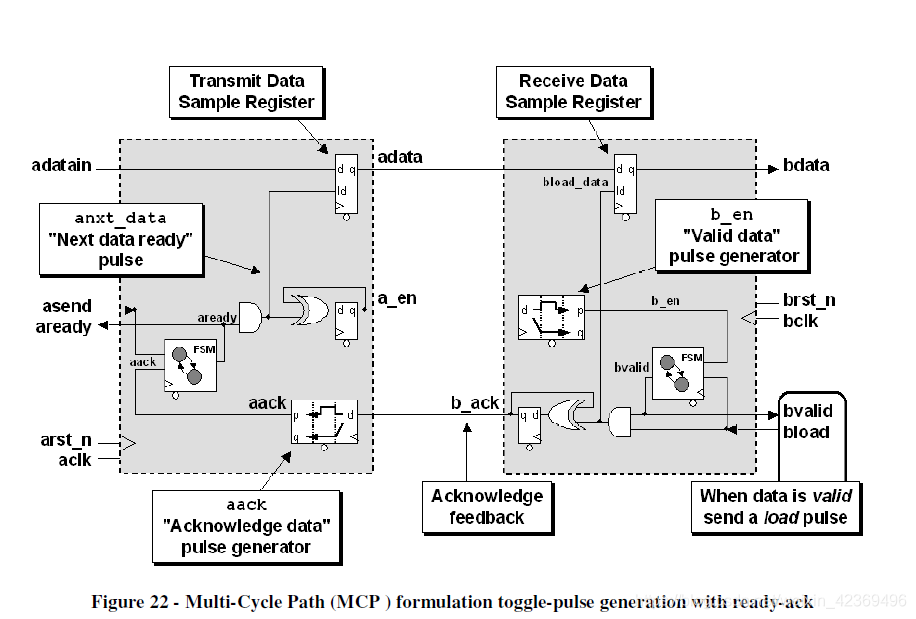

上一节节中描述的技术的完全响应变化使用MCP公式是仅在接收时钟域确认接收到具有bload脉冲的数据之后才将使能信号作为确认信号传递回发送时钟域,如图所示 在图22中。

对于图22中的示例,接收时钟域具有小的WAIT-READY,1状态FSM,当数据在数据寄存器的输入上有效时,它向接收逻辑发送有效信号(bvalid)。 在接收逻辑确认应通过断言bload信号来加载数据之前,实际上不会加载数据。

在数据加载之前,没有对发送时钟域的反馈,然后b_ack信号与具有自动反馈的MCP公式一样被发回。

这是一个反馈路径,需要在捕获数据并发送反馈之前对接收时钟域进行操作。

4.4 Synchronizing counters

是否需要对从一个时钟域传递到另一个时钟域的信号的每个值进行采样? 答案是不!

由于能允许有效设计跳过某些计数值样本,是否可以使用任何计数器在CDC边界上传递计数值? 答案是不。

4.4.1 Binary counters

二进制计数器的一个特征是所有顺序二进制递增操作的一半要求两个或更多个计数器位必须改变。 尝试跨CDC边界同步二进制计数器与尝试将多个CDC信号同步到新的时钟域相同。 如果一个简单的4位二进制计数器从地址7(二进制0111)变为地址8(二进制1000),则所有四个计数器位将同时改变。 如果同步时钟沿进入该转换的中间,则可以对任何4位二进制模式进行采样并同步到新的时钟域,如图23所示。

在FIFO设计中,新的同步二进制值可能触发错误的满标志或空标志,甚至更糟糕的是,它可能不会触发实际的满标志或空标志,导致数据由于FIFO溢出而丢失或导致无效数据被读取 当FIFO真的为空时,由于尝试读取数据而导致FIFO。

4.4.2 Gray codes

格雷码以Frank Grey [4]命名,可用于多时钟设计的最安全的计数器是格雷码计数器。 格雷码仅允许每个时钟转换一位改变,消除了与尝试在时钟域上同步多个改变的CDC位相关的问题。

标准格雷码具有非常好的转换属性,可以将灰色转换为二进制并再返回。 使用这些转换,设计高效的灰色代码计数器非常简单。

4.4.3 格雷码到二进制转换

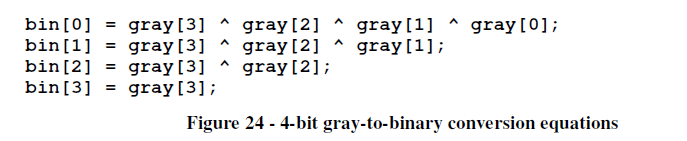

为了将格雷码转换为等效的二进制代码值,使用n位格雷码值作为示例,二进制位0等于与所有其他格雷码独占的格雷码0的异或。 位从1到n。 二进制位1是等于格雷码位1,与从2到n等所有其他格雷码位排除。最高有效二进制位恰好等于最高有效格雷码位。

图24显示了样本4位格雷码到二进制转换的公式。

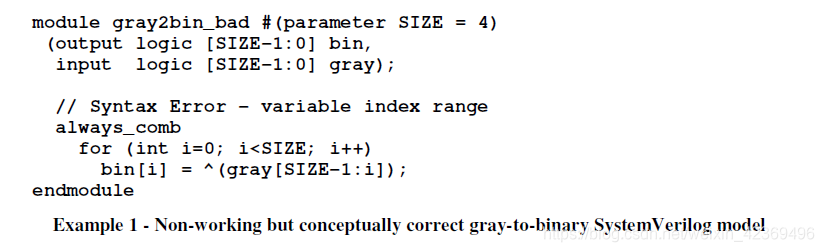

编写格雷码到二进制转换器的最简单方法是编写for循环并对具有可变索引范围的格雷码向量进行异或减少,其中每次循环时索引范围的LSB都会增加,直到 我们留下bin

[MSB] = ^ gray [MSB:MSB]的简单分配(只是格雷码向量的1位MSB),如例1所示。

遗憾的是,Verilog和SystemVerilog不允许使用变量索引范围进行部分选择,因此示例1中的代码虽然在概念上是正确的,但不会编译。

要解决这个问题,请记住,异或门实际上是一个可编程逆变器。 如果一个输入接高电平,则另一个输入反转并传递到输出。 类似地,如果一个输入接低电平,则另一个输入传递到输出而不进行反转(输入到输出没有变化)。

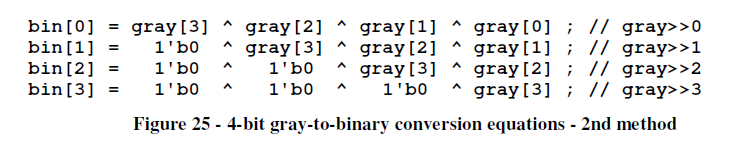

利用任何涉及0输入的附加异或操作不会改变操作结果的事实,格雷码到二进制转换的方法是异或格雷码位 填充0,如图25所示。

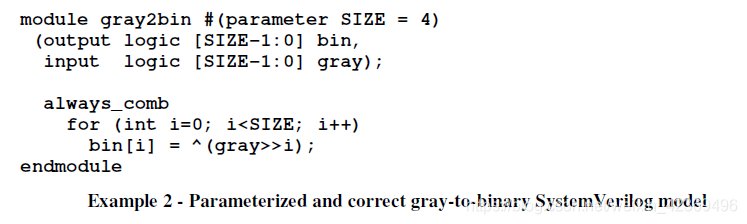

示例2中显示了此简化算法的相应参数化SystemVerilog模型。此示例在语法上是正确的,且编译确实有效。

输入与0相关的所有额外异或操作会发生什么? 综合工具认识到,可以优化一个输入上具有常数0的异或门,以推断设计的非常有效的实现。

4.4.4 二进制到格雷码转换

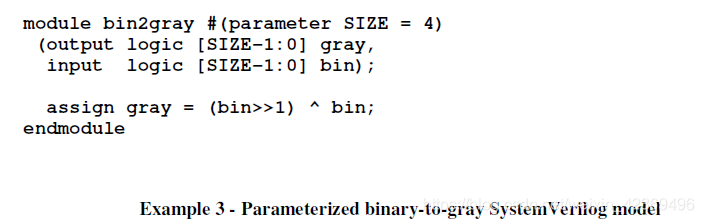

为了将二进制值转换为等效的格雷码值,使用n位二进制值作为示例,格雷码位0等于二进制位0和1的异或。格雷码位1相等 最高有效格式的格雷码位等于最高有效位的二进制位。

样本4位二进制到格雷码转换的公式如图26所示。

编写二进制到灰度转换器的最简单方法是编写一个简单的连续赋值,在二进制向量和相同二进制向量的右移版本之间执行逐位异或操作,如例3所示。 这个例子在语法上是正确的,将编译并确实有效。

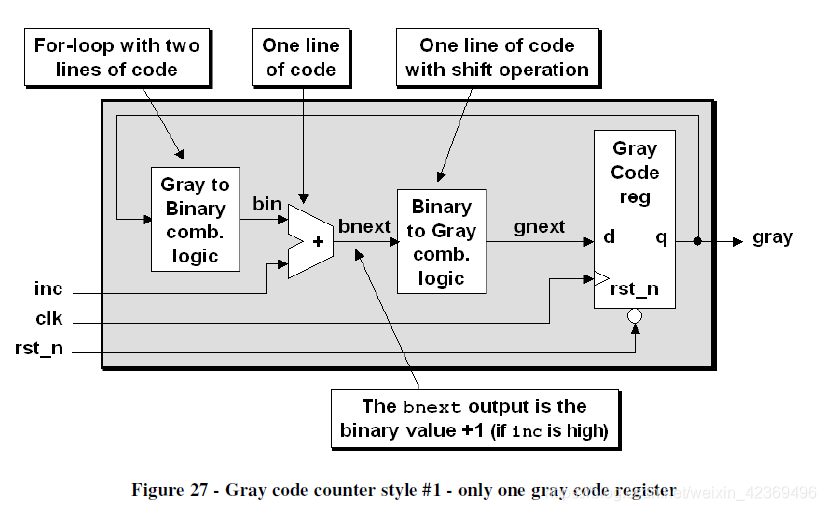

4.4.5 Gray code counter style #1

我们可以使用上两节中显示的转换来构建一个格雷码计数器。 对于任何格雷码计数器,重要的是要记住必须注册格雷码输出以消除设计中的任何组合稳定。

用于格雷码计数器样式#1的SystemVerilog代码包含灰色到二进制转换器,二进制到灰度转换器,并在转换之间递增二进制值,如图27所示。

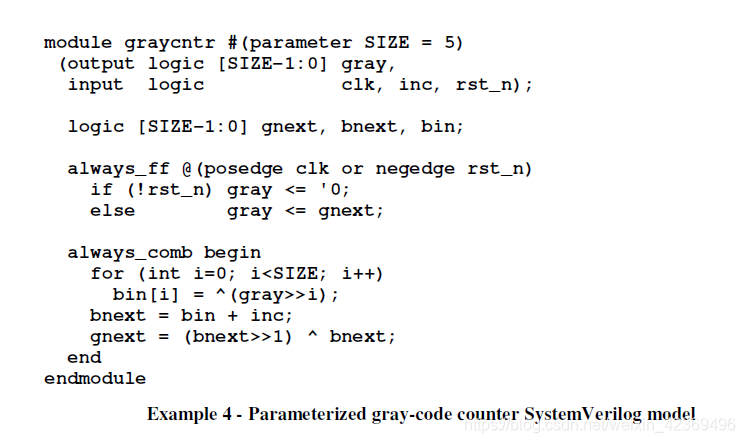

格雷码码计数器样式#1的相应参数化SystemVerilog模型如例4所示。

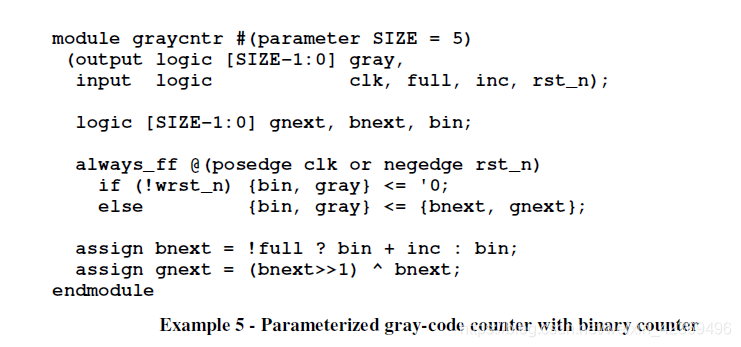

4.4.6 Gray code counter style #2

我们可以通过仅使用4.4.4节中显示的二进制到格雷码转换来构建第二种格式的灰色代码计数器。 该格雷码计数器实际上是二进制计数寄存器和格雷码计数寄存器。

用于灰色代码计数器样式#2的SystemVerilog代码包含一个二进制计数器,以消除对灰色到二进制转换的需要,并使用下一个二进制计数值进行二进制到灰色转换,然后将其注册到 格雷码寄存器。

这种风格使用两倍的触发器,但使用更短的组合逻辑路径来生成下一个格雷码值,这使得这种实现比灰色代码计数器样式#1更快。 格雷码计数器样式#2的框图如图28所示,

灰色代码计数器样式#2的相应参数化SystemVerilog模型如例5所示。

4.5 其他多位CDC技术

除了前面章节中描述的MCP配方技术之外,我还发现许多工程师使用标准FIFO在时钟域之间传递数据和控制信号。

至少有两种有趣的FIFO实现策略可用于解决多位CDC信号完整性:

(1)异步FIFO实现。

(2)2-depth FIFO实现。

4.5.1 使用异步FIFOS传递多位CDC信号

传输多个位,无论是数据位还是控制位,都可以通过异步FIFO完成。 异步FIFO是共享存储器或寄存器缓冲器,其中数据从写时钟域插入,数据从读时钟域移除。 由于发送器和接收器都在各自的时钟域内工作,因此使用双端口缓冲器(如FIFO)是在时钟域之间传递多位值的安全方法。

只要FIFO未满,标准异步FIFO设备就允许插入多个数据或控制字,只要FIFO不为空,接收器就可以在方便时提取多个数据或控制字。

FIFO设计中的大多数艰苦工作都是通过格雷码计数器的同步完成的,并且在中描述了成熟的FIFO设计技术。

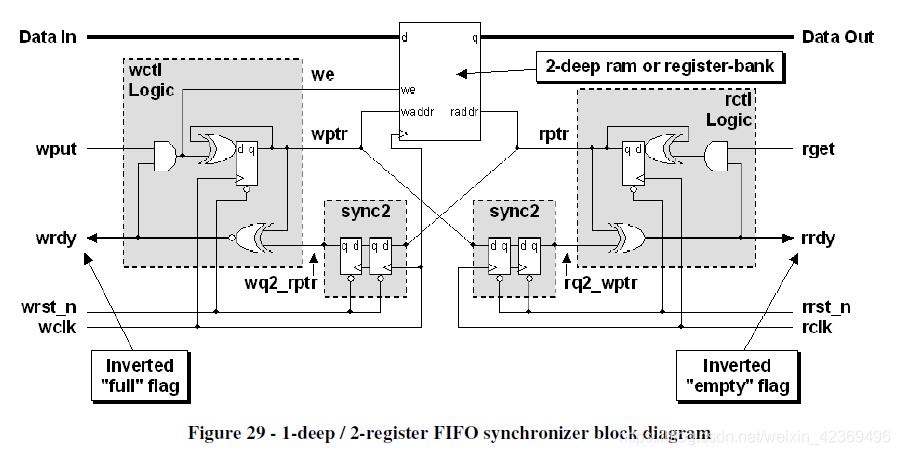

4.5.2 使用1-deep / 2-寄存器FIFO同步器传递多位CDC信号

在CDC边界上传递多个控制和数据位的另一个有趣变化涉及使用1-deep / 2-寄存器FIFO,如图29所示。

这个1-deep / 2-寄存器FIFO具有许多有趣的特性。由于FIFO只使用两个寄存器或一个2深的双端口RAM构建,用于检测满和空的灰色代码计数器是简单的切换触发器,这实际上只不过是1位二进制计数器(记住,标准格雷码的MSB与二进制码的MSB相同。

复位时,两个指针都被清除,FIFO为空,因此FIFO未满。我们使用反转未满条件来指示FIFO已准备好接收数据或控制字(wrdy为高)。在将数据或控制字放入FIFO(使用wput)之后,wptr切换并且FIFO变满,或者换句话说,wrdy信号变低,这也禁用了切换wptr的能力,因此也禁用了能够将另一个字放入2寄存器FIFO,直到接收时钟域逻辑从FIFO中移除第一个字。

这个设计特别有趣的是,wptr现在指向2寄存器FIFO中的第二个位置,所以当FIFO再次准备就绪时(当wrdy为高电平时),wptr已经指向下一个位置写。

在FIFO的接收侧复制相同的概念。当数据或控制字写入FIFO时,FIFO变为空。我们使用反转非空条件来指示FIFO具有准备接收的数据或控制字(rrdy为高)。

通过使用两个寄存器来存储多位CDC值,我们能够从发送MCP公式中移除一个时钟周期,并从确认反馈路径中移除另一个周期。

探讨了在多时钟设计中同步多个信号的复杂性,包括信号偏斜、多循环路径公式、格雷码计数器的应用以及FIFO技术。提出了多种策略,如信号合并、使用格雷码和MCP公式,以确保跨时钟域的数据安全传输。

探讨了在多时钟设计中同步多个信号的复杂性,包括信号偏斜、多循环路径公式、格雷码计数器的应用以及FIFO技术。提出了多种策略,如信号合并、使用格雷码和MCP公式,以确保跨时钟域的数据安全传输。

403

403

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?