同步计数器74x163 的实现

1 74x163介绍

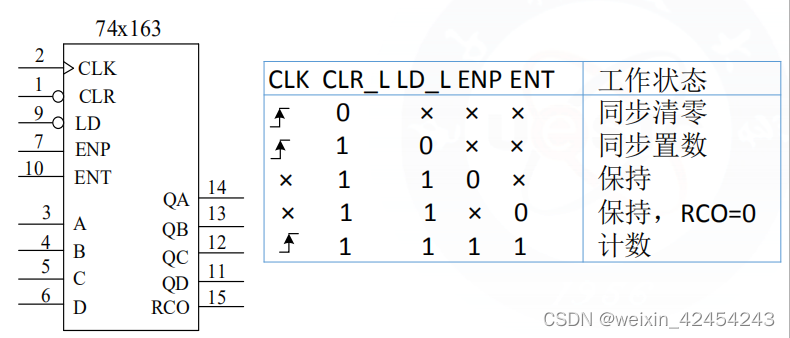

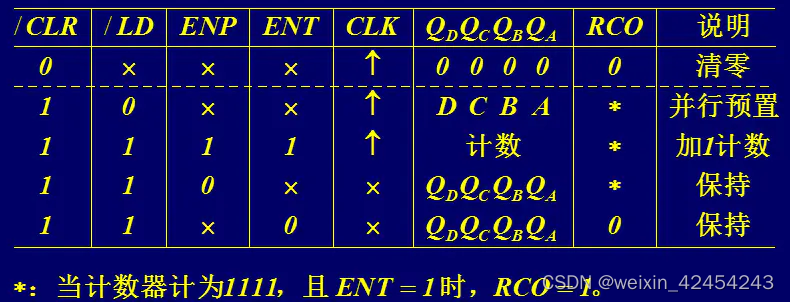

74LS163计数器有5个控制端、4个数据输入端和5个输出端,其逻辑功能和对应的逻辑符号如下图1和图2所示:(该例子在教材《Xilinx FPGA原理与实践—基于Vivado和Verilog HDL——卢有亮》P95页)

(CLR非)是异步清零端——低有效清零端

(LD非)是同步置数控制端——数据装载输入

ENT和ENP是计数控制端——使能

CLK用作时钟信号输入端

ABCD用作4位预置数据输入——数据输入,是装载到4个触发器上

QAQBQCQD表示四位计数器的状态——数据输出

RCO为计数器进位输出端

同步置数:当clk上升沿时,clr_l清零无效(clr_l=1),ld_l是0,是装载的功能,如输入ABCD=1010,即输出QAQBQCQD也是1010;

保持:当clr_l清零无效(clr_l=1),ld_l是1也无效,ENP是0,四个D触发器的值保存不变;

保持,RCO=0:当clr_l清零无效(clr_l=1),ld_l是1也无效,ENT是0;

计数:当clk上升沿时,当clr_l清零无效(clr_l=1),ld_l是1也无效,ENP是1,ENT是1,计数功能

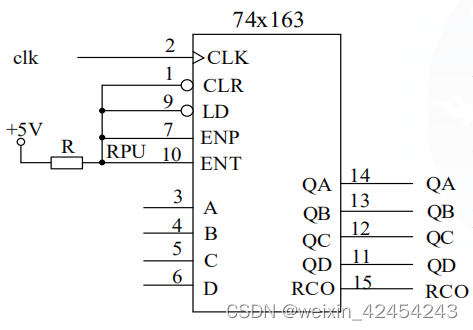

2 74x163自由工作模式

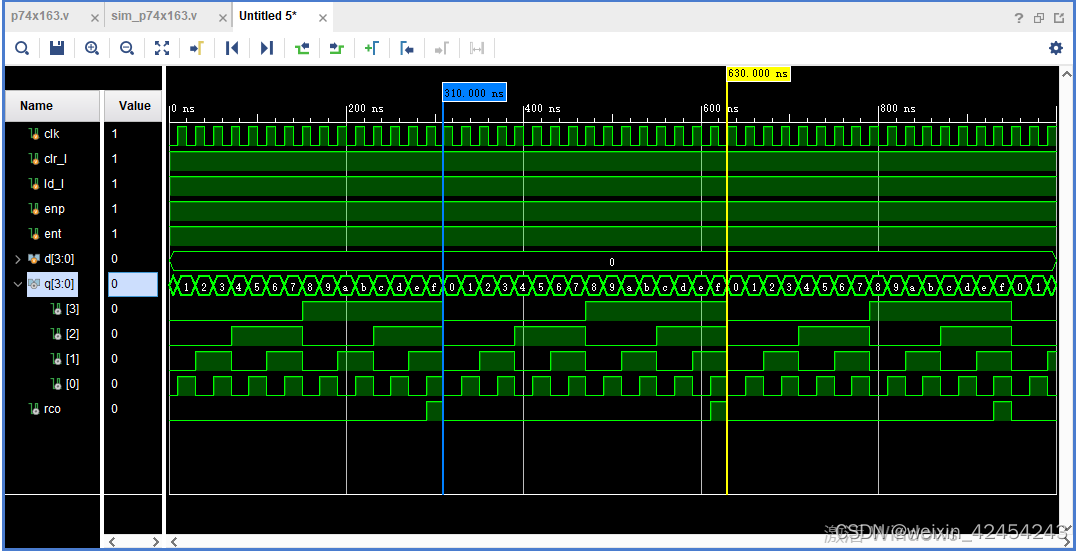

自由模式时,QDQCQBQA输出在每个时钟边沿变化, 从0000开始计数,0000-0001-0010…1111-0000…完成从0到15的循环计数,当计数值为15时,RCO有效,输出1。

3 设计文件

module p74x163(clk,clr_l,ld_l,enp,ent,d,q,rco);

input clk,clr_l,ld_l,enp,ent;

input[3:0] d;

output [3:0] q;

output rco;

reg [3:0] q=0;

reg rco=0;

always @ (posedge clk) begin

if (clr_l==0) q<=0;

else if (ld_l==0) q<=d;

else if ((enp==1) && (ent==1)) q<=q+1;

else q<=q;

end

always @ (q or ent) begin

if ((ent==1) && (q==15)) rco=1;

else rco=0;

end

endmodule

4 仿真文件

`timescale 1ns / 1ps

module sim_p74x163;

reg clk=0;

reg clr_l=1;

reg ld_l=1;

reg enp=1;

reg ent=1;

reg[3:0] d=0;//输入用reg

wire[3:0] q; //输出用wire

wire rco;

p74x163 uut(clk,clr_l,ld_l,enp,ent,d,q,rco);

always # 10 clk=~clk;

endmodule

5 仿真结果

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?