今天偶然看到一个有关等精度频率计设计的东西。感觉用处挺大,遂做以研究。

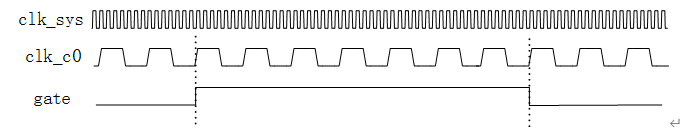

其原理为:如图所示:

在固定门控时间gate内,通过计数被测时钟的时钟个数cnt1,与基准时钟的时钟个数cnt2,

有 cnt1/(clk_c0) =time_gate 式1

cnt2/(clk_sys) =time_gate 式2

则通过联立两式可计算得被测时钟的频率,如式3

clk_c0=cnt1*clk_sys/cnt2; 式3

下面进行程序设计:系统时钟clk_sys给定为50MHz,为了进行等精度频率计设计,通过pll进行被测时钟clk_c0分频为10MHz,若通过程序设计仿真计算的被测时钟频率为10MHz,则设计成功。

代码如下:

module test ( input clk_sys,//系统时钟50M

input rst_n, //系统复位

output reg[31:0]freq //输出频率

);

//reg

reg gate;

reg gate_clk_c0_1;

reg gate_clk_c0_2;

reg gate_clk_sys_1;

reg gate_clk_sys_2;

reg [10:0]gate_cnt;

reg [10:0]cnt1;

reg [13:0]cnt2;

//wire

wire nege_clk_sys_gate;

wire nege_clk_c0_gate;

wire clk_c0;

pll_10M pll_10M(

.inclk0(clk_sys),

.clk_c0(clk_c0)

);

//门控时钟计数,计数周期1020,门控前后个10个clk_c0时

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?