内容

实验一:7人表决器的设计

实验二:算数逻辑单元的设计

实验三:JK触发器的设计

实验四:环形计数器的设计

实验五:顺序排列的设计

实验六:二进制除法器的设计

实验七:数字显示频率计的设计

实验八:序列检测器的设计

实验九:数字秒表的设计

实验十:自助售票机的设计

实验七:数字显示频率计的设计

设计一个8 位数字显示的简易频率计

①能够测试10Hz~10MHz 方波信号;

②电路输入的基准时钟为1Hz,要求测量值以8421BCD 码形式输出;

③系统有复位键;

④采用分层次分模块的方法;

//程序:

module freq(rst,clk_b,clk_a,fin);

input rst,clk_b,clk_a;

output[7:0]fin;

wire mul_clk, rst_comp;

wire [7:0]ratio_start;

and U0(rst_comp,rst,clk_a);

task1 U1(.ain(clk_b),.din(clk_a),.mul(mul_clk));

task2 U2(.clk(mul_clk),.count(ratio_start),.rst(rst_comp));

task3 U3(.ratio_start(ratio_start),.fin(fin));

endmodule

module task2 (clk,count,rst);

parameter bit=8;

input clk,rst;

output[bit-1:0]count;

reg[bit-1:0]count;

always@(posedge clk or negedge rst)

if(!rst) count<=8'b0;

else count<=count+1;

endmodule

module task1(ain,din,mul);

parameter width=1;

input[width-1:0]ain,din;

output[width*2-1:0]mul;

assign mul=ain*din;

endmodule

module task3 (ratio_start,fin);

input[7:0]ratio_start;

output[7:0]fin;

assign fin=2*ratio_start;

endmodule

//测试代码:

module freq_tb;

reg clk_a,clk_b,rst;

wire[7:0]out;

freq U(.rst(rst),.clk_b(clk_b),.clk_a(clk_a),.fin(out));

initial begin rst=0;clk_b=0;clk_a=0;end

initial begin #15 rst=1;#500 rst=0;#15 rst=1;end

always #1 clk_b=~clk_b;

always #10 clk_a=~clk_a;

endmodule

结果分析:

测试结果表明,该电路能够测试10Hz~10MHz 方波信号;电路输入的基准时钟为1Hz,输出为8421BCD 码形式;系统有复位键;采用了分层次分模块的方法;

实验八:序列检测器的设计

在每一个时钟下降沿检查输入数据,当输入数“10011”时,输出asm被置为1;其余情况asm为0。 并画出fsm(有限状态机)

//程序

module detector(clk, reset, d, y);

input clk, reset, d;

output wire y;

reg [2 : 0] state;

parameter idle = 3'b000, s1 = 3'b001, s2 = 3'b010, s3 = 3'b011,

s4 = 3'b100, s5 = 3'b101, s6 = 3'b110, s7 = 3'b111;

always@(posedge clk or posedge reset)

begin

if(reset) state <= idle; else begin

casex(state)

idle: begin if(d == 1) state <= s1; else state <= idle; end

s1: begin if(d == 0) state <= s2; else state <= s1; end

s2: begin if(d == 0) state <= s3; else state <= s7; end

s3: begin if(d == 1) state <= s4; else state <= s6; end

s4: begin if(d == 0) state <= s5; else state <= s1; end

s5: begin if(d == 1) state <= s1; else state <= s3; end

s6: begin if(d == 1) state <= s7; else state <= s6; end

s7: begin if(d == 1) state <= s1; else state <= s2; end

default: state <= idle;

endcase end

end

assign y = (state == s4 && d == 0) ? 1 : 0;

endmodule

//测试代码:

`timescale 1ns/1ns

`define halfperiod 10

module detector_tb(clk, reset, d, y);

output clk, reset, d, y;

reg clk, reset;

reg [23 : 0] data;

wire d, y;

initial

begin

clk = 0; reset = 0;

#5 reset = 1;

#20 reset = 0; data = 24'b0011_1100_1001_0000_1001_0100;

#(`halfperiod * 200) $stop;

end

always #`halfperiod clk = ~clk;

always@(negedge clk) #5 data = {data[22 : 0], data[23]};

assign d = data[23];

detector m0(.clk(clk), .reset(reset), .d(d), .y(y));

endmodule

结果分析:

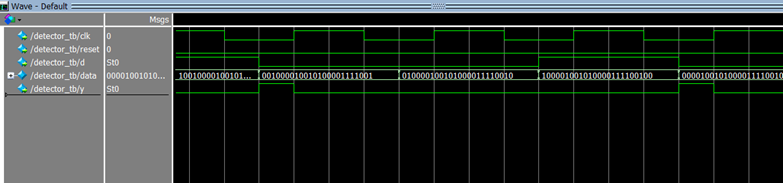

为了检测输入数据中的存在的10010序列,采用状态机实现的方法,对8个状态进行编码,状态机如上图所示,当检测出10010序列,输出高电平,输出采用数据流描述的方式,采用组合逻辑输出;测试代码首先定义一个24位用于存放待测数据码的寄存器变量,生成测试信号并执行100个时钟周期,用循环移位的方式待测数据码流,将最高位输入到序列检测器中,由上面仿真波形可知,10010序列仿真已经实现,设计满足预期。

66

66

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?