基于等精度测量的数字频率计仿真工程

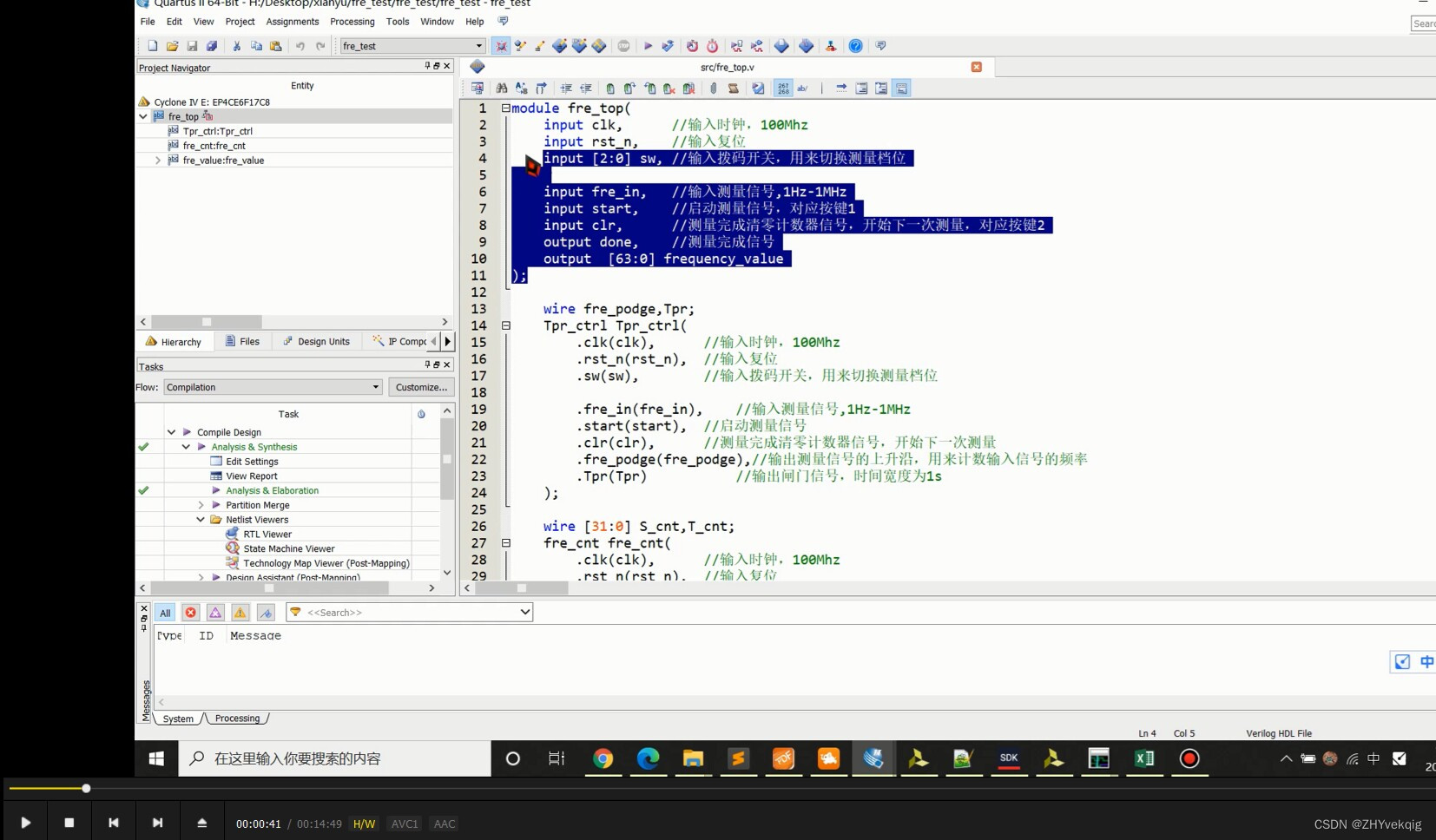

本设计按照等精度测量原理,设计三个模块,分别是闸门时间模块,计数器模块,测量结果模块,最后用顶层文件封装起来,编写测试文件在quartus+modelsim联合仿真完整结果,还有专门录制的视频对工程讲解,手把手教你对这个工程仿真,可看图片

这个频率计的功能可以测量频率1Hz-50MHz,只要最高系统时钟频率是测量频率的2倍就行,可以按照不同的频率范围使用不同的闸门时间宽度,也就是量程切换,具体的代码都会有注释,适合有fpga基础的人联系来学习,如何仿真验证一个工程,同时也可以仿真占空比,相位差,脉冲宽度的工程,需要的话可以聊,做成硬件的也可以,也有现成做好的硬件,关键是做成的对学习和研究有帮助就都可以帮忙

包括完整的quartus工程和视频(15分钟左右)

基于等精度测量的数字频率计仿真工程

随着现代电子技术的飞速发展,数字电路技术已成为电子工程的重要分支,数字频率计作为数字电路领域的研究热点之一,受到了广泛的关注和研究。本文将深入分析基于等精度测量的数字频率计的仿真工程,为有FPGA基础的人提供学习和研究参考。

设计原理

等精度测量原理是数字频率计的核心设计思想,该原理是将要测量的脉冲信号与参考信号进行比较,并累加比较结果,从而精确地测量频率,实现等精度测量。

基于等精度测量原理,我们设计了三个模块:闸门时间模块,计数器模块,测量结果模块。闸门时间模块用于控制闸门时间的开启和关闭,计数器模块用于计数,并将计数结果通过测量结果模块进行处理和输出。最后,我们用顶层文件封装起来,实现完整的数字频率计的仿真工程。

设计实现

在本设计中,我们主要使用了Quartus和Modelsim软件,分别进行逻辑设计和仿真验证。通过逐步梳理设计思路,我们最终实现了基于等精度测量的数字频率计仿真工程。

首先,我们在Quartus中创建模块,包括闸门时间模块、计数器模块和测量结果模块。在每一模块的设计实现中,我们注重保证模块的稳定性和可靠性,兼容性和扩展性。其中,闸门时间模块主要是通过包含一个周期计数器,实现对闸门时间的控制,计数器模块主要是对输入信号进行计数,并进行计数结果的存储和传输,而测量结果模块主要是对计数结果进行处理,计算出实际测量的频率值。

其次,我们通过顶层文件将三个模块进行封装,并进行仿真验证。在Modelsim中,我们编写测试文件进行联合仿真,并通过仿真验证核心功能是否正常运行、数据的准确性和稳定性等方面进行全面的检验。同时,我们还通过录制视频的方式进行模块的详细讲解,手把手教你对这个工程仿真,使读者更好地理解数字频率计的设计原理和实现方法。

功能特点

本设计实现的数字频率计,可以实现对频率1Hz-50MHz的测量,且只要最高系统时钟频率是测量频率的2倍即可。此外,我们还可以根据不同的频率范围使用不同的闸门时间宽度,即实现量程切换。而且,在设计代码中,我们还提供了详细的注释,方便读者对设计过程进行理解和学习。

除此之外,我们还可以将仿真验证的内容拓展到占空比、相位差、脉冲宽度等方面的工程。如果需要,可以与我们进一步交流。

结论

本文基于等精度测量原理,深入分析基于等精度测量的数字频率计的仿真工程。通过Quartus和Modelsim软件的联合设计和仿真验证,我们成功实现了对频率1Hz-50MHz的测量,且能够实现量程切换的功能。同时,我们还提供了详细的设计代码注释和录制视频,让读者更好地理解数字频率计的设计原理和实现方法。

相关代码,程序地址:http://lanzouw.top/620255055769.html

3507

3507

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?