HLS是什么

Vivado HLS——一个是采用高级语言去描述系统行为即用 C/C++来实现系统建模,软件工程师可以借此提高系统性能:也就是说之前可能需要 CPU/DSP/GPU 实现的一些算法,我们都可以借助 Vivado HLS 直接通过 C/C++编程来用 FPGA 实现,一方面提高了并行性,也就是提高了系统的吞吐率,另一方面还可以降低系统的功耗。

在用 C/C++描述完算法之后,还需要相应的测试程序来测试算法的正确性。同时生成的 HDL 代码在验证时也会用的 C/C++编写的测试激励。从这个角度而言,Vivado HLS 生成的 HDL 代码并不是要求我们看懂的,因为生成的 HDL 代码命名本身并没有什么可读性,所以我们需要做的就是在 C/C++层面把算法做更多的优化,以及对综合工具采用相应的指导(directives)。

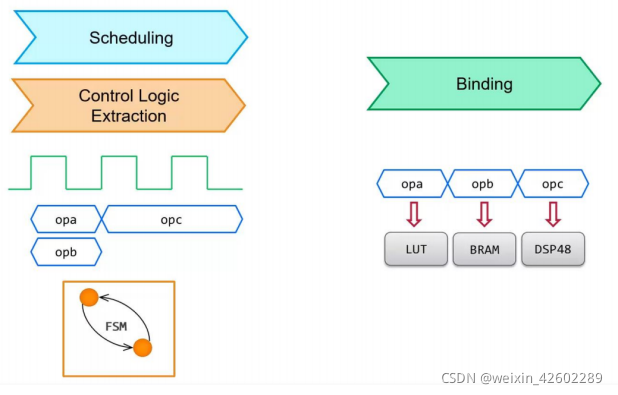

Vividao HLS 在将 C/C++代码转换成 HDL 代码时所经历的阶段如图所示:

调度(Scheduling):实现控制逻辑的提取,确定每个时钟周期应该执行的操作,计算操作所需要的时钟周期和可以并行执行的操作,会生成相应的状态机,

绑定(B

本文介绍了Vivado HLS工具如何使用C/C++实现FPGA设计,包括C源码仿真、高层次综合等步骤。通过HLS,软件工程师可以提升系统性能,优化算法,并将代码转换为HDL。文章详细阐述了HLS的编译过程,如调度、绑定阶段,并提到了Test Bench在验证中的作用。最后,作者提供了创建新项目、设置FPGA型号以及进行C源码仿真的指南。

本文介绍了Vivado HLS工具如何使用C/C++实现FPGA设计,包括C源码仿真、高层次综合等步骤。通过HLS,软件工程师可以提升系统性能,优化算法,并将代码转换为HDL。文章详细阐述了HLS的编译过程,如调度、绑定阶段,并提到了Test Bench在验证中的作用。最后,作者提供了创建新项目、设置FPGA型号以及进行C源码仿真的指南。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2145

2145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?