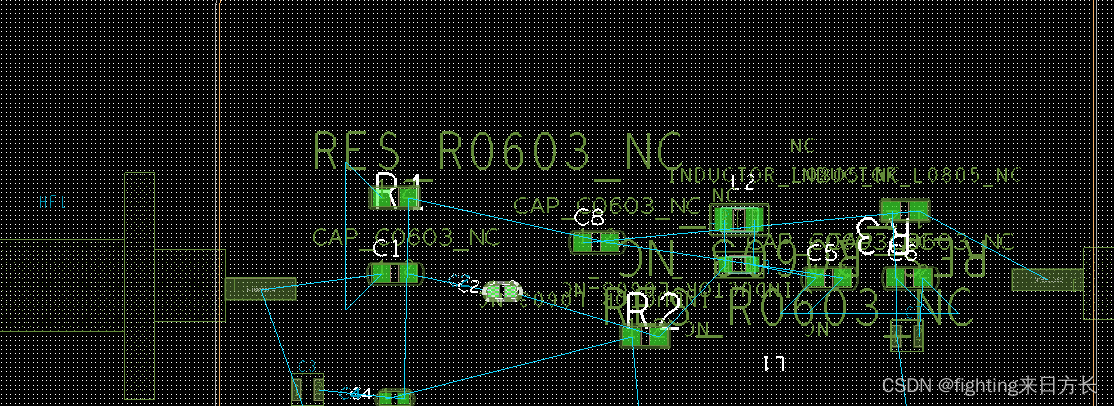

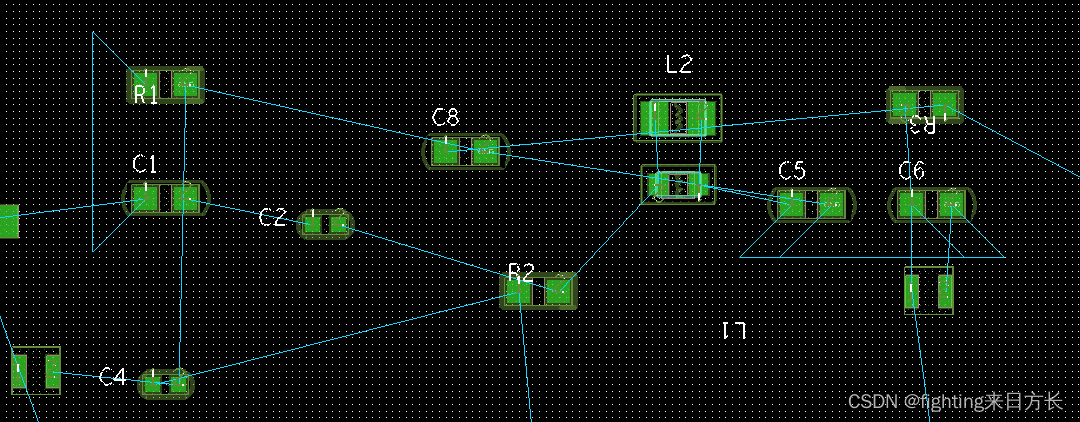

因为生成PCB时用的是各个库中集成的,所包含的内容很多,生成PCB时界面很乱

但其实布局的时候,最主要的就是根据refdes中的silkscreen top来布局,调试,所以需要把其他不需要的隐藏起来,再将silkscreen top的text按照统一的设置。

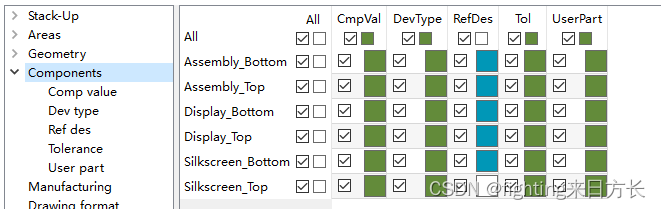

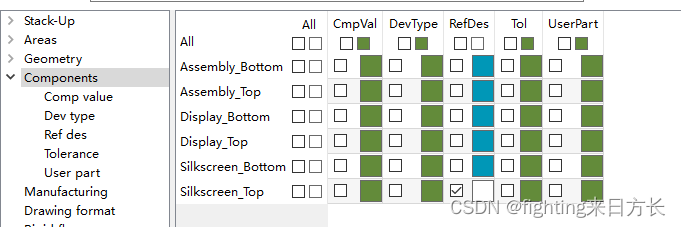

选择color里的components,将所有的都关闭,只选择一个

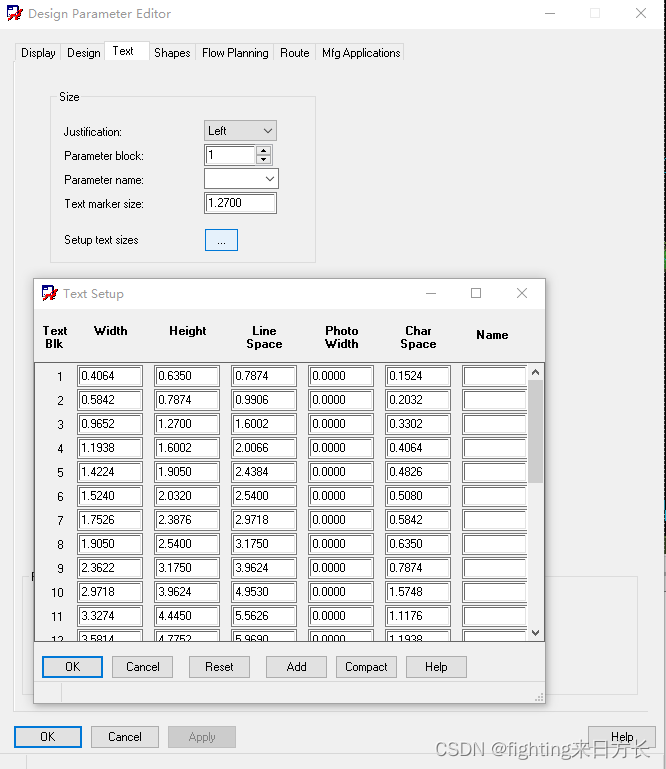

再统一修改text

edit changel里选择,右侧options仅选择text,再对齐进行改变。

放置元器件丝印需要注意的几个原则:

1.不要与元器件的焊盘,丝印框,过孔等重合

2.在TOP层,看丝印的字母,正常元器件横放的时候,在左,竖放的时候,在下

在BOTTOM层,横放的时候在右,竖放的时候在下.(涉及到一个镜像的问题)

丝印层:25,30,1,5,1mil大概排列.

Cadence里PCB的丝印层修改操作

于 2022-06-02 17:50:17 首次发布

在创建PCB时,为避免界面混乱,关键在于根据refdes的silkscreentop布局。要隐藏不必要的组件,统一设置text属性。布局原则包括避免丝印与焊盘、丝印框等重合,并遵循特定的丝印位置规则。在TOP层,丝印通常在左或下,而BOTTOM层则相反。此外,了解丝印层的排列也很重要。

在创建PCB时,为避免界面混乱,关键在于根据refdes的silkscreentop布局。要隐藏不必要的组件,统一设置text属性。布局原则包括避免丝印与焊盘、丝印框等重合,并遵循特定的丝印位置规则。在TOP层,丝印通常在左或下,而BOTTOM层则相反。此外,了解丝印层的排列也很重要。

4376

4376

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?