目前正在学习FPGA,用的是Xinlinx 黑金板子,结合正点原子例程和黑金的例程去学习,而黑金却没有该IP核之PLL实验,于是根据正点原子的例程进行学习。

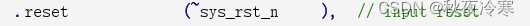

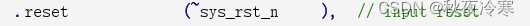

根据正点原子的文档,写了程序,但是仿真的结果却无法实现,其sys_rst_n和sys_clk一直显示高阻态,最后查找发现是下方图片忘记取反了

还有查找的时候,发现了这个篇好文章,结合正点原子的记录一下

https://blog.csdn.net/yishuihanq/article/details/130760772

作者在使用Xilinx黑金板学习FPGA时,遇到缺少PLL实验IP的问题。按照正点原子的例程编写程序后,仿真结果显示sys_rst_n和sys_clk为高阻态。通过查阅资料发现是信号取反问题,解决了这一困扰。

作者在使用Xilinx黑金板学习FPGA时,遇到缺少PLL实验IP的问题。按照正点原子的例程编写程序后,仿真结果显示sys_rst_n和sys_clk为高阻态。通过查阅资料发现是信号取反问题,解决了这一困扰。

目前正在学习FPGA,用的是Xinlinx 黑金板子,结合正点原子例程和黑金的例程去学习,而黑金却没有该IP核之PLL实验,于是根据正点原子的例程进行学习。

根据正点原子的文档,写了程序,但是仿真的结果却无法实现,其sys_rst_n和sys_clk一直显示高阻态,最后查找发现是下方图片忘记取反了

还有查找的时候,发现了这个篇好文章,结合正点原子的记录一下

https://blog.csdn.net/yishuihanq/article/details/130760772

1267

1267

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?