在经典模拟电路理论中,我们常常依赖运算放大器的“虚短”特性来推导电路行为:V+≈V−。然而,这种结论建立在“运放开环增益无限大且无延迟”的理想假设之上。实际的高速放大器远非如此——开环增益随频率迅速下降,内部补偿带来相位滞后,并且输入端存在不可忽略的输入电容Cin。当信号频率升高时,虚短条件快速失效,导致峰值较大的瞬时差分电压 (Vd = V+ - V-),直接触发以下问题:

- 输出信号过冲

- 振铃

- 轻微到严重的边缘振荡

- 在极端情况下,引发自激振荡

因此,在高速差分放大器设计中,工程师常会在运放输入端的 V+ 与 V- 之间并联一个电阻,看似简单,却非常关键。

一、问题根源:输入电容 + 运放延迟共同破坏相位裕度

1. 输入电容与反馈电阻构成低通环节

运放输入端本身存在一个电容:

Cin=Cdiff+Ccm+寄生电容

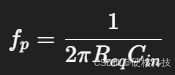

当反馈电阻 ( R_f ) 和输入电阻 ( R_g ) 与其形成 RC 网络时,会引入额外 pole:

该 pole 带来额外相位滞后,使相位裕度下降。

相位裕度不足 → 过冲、振铃、甚至振荡

差分运放输入并联电阻作用解析

差分运放输入并联电阻作用解析

订阅专栏 解锁全文

订阅专栏 解锁全文

2969

2969

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?