谐振、品质因数与串并联转换解析

1. 引言

在电子电路中,谐振(Resonance)是一个重要的现象,它通常发生在由电感(L)、电容(C)和电阻(R)构成的电路中。在谐振条件下,电路的总反应仅由电阻控制,电感和电容的影响互相抵消,导致电路的阻抗变得最小(对于串联电路而言),或者最大(对于并联电路而言)。理解谐振现象对于设计高效能的射频(RF)电路至关重要,尤其是在设计滤波器、振荡器、谐振腔等电路时。

在本节中,我们将详细探讨谐振的基本原理、品质因数(Q因数)的计算方式、串并联RLC电路的区别,并分析如何通过串并联电路的转换来优化设计。

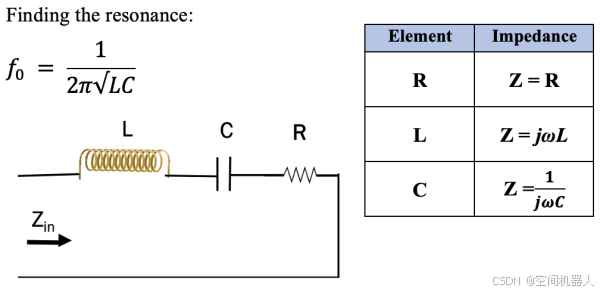

2. 谐振现象解析

谐振发生在RLC电路中,当电感和电容的反应相互抵消时,电路的总反应主要由电阻决定。谐振是一个频率相关的现象,在谐振频率下,电感的感抗(X_L)和电容的容抗(X_C)互相抵消,从而使得电路的总阻抗达到最小(串联电路)或最大(并联电路)。

在串联RLC电路中,电感的感抗为X_L = 2πfL,而电容的容抗为X_C = 1 / (2πfC)。当电感的感抗和电容的容抗相等时,电路就达到了谐振状态,即:

X_L = X_C

此时,电路的总阻抗仅由电阻R决定。谐振频率f₀可以通过以下公式计算:

f₀ = 1 / (2π√(LC))

当频率达到这个值时,电路的总反应为纯电阻性,且电能在电感和电容之间进行高效地交换。

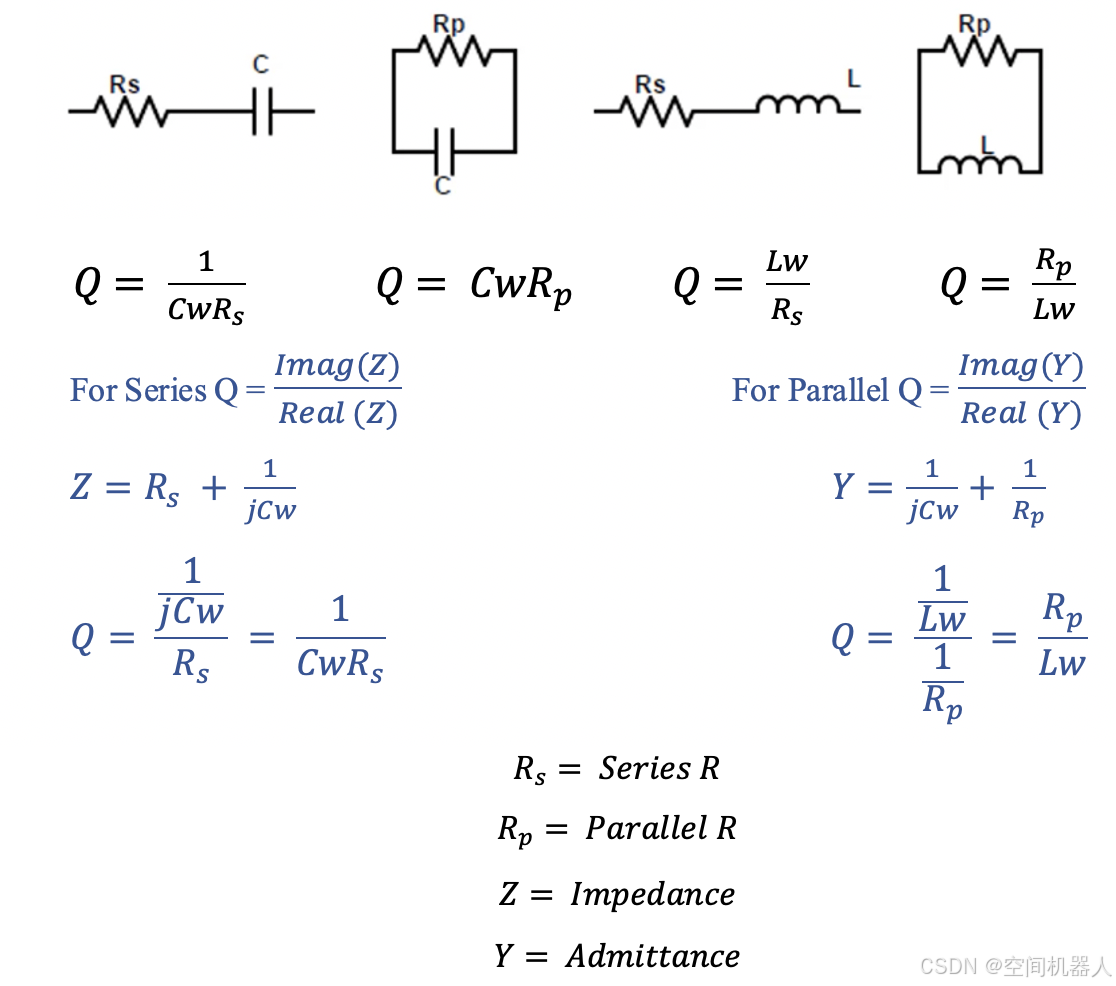

3. 品质因数(Q因数)

品质因数Q是描述电路谐振质量的一个重要参数,表征了电路的能量损耗与能量储存能力的比值。具体来说,Q因数越高,电路在谐振频率下的选择性越好,能量损失越小,电路的带宽越窄;而Q因数越低,电路的选择性较差,能量损耗较大,带宽较宽。

Q因数的定义如下:

Q = X_L / R = X_C / R

其中,R为电路的电阻,X_L为电感的感抗,X_C为电容的容抗。在高Q电路中,由于能量损失较小,电路具有较高的稳定性和选择性,因此常被用于要求高精度频率选择的应用,如滤波器和振荡器。

Q因数的另一种表达形式为:

Q = f₀ / Δf

其中,Δf为电路的带宽,表示电路能够响应的频率范围。当电路的Q因数较高时,带宽Δf较小,电路对频率的选择性很高,只对非常接近谐振频率的信号有响应。

4. 串联与并联RLC电路的区别

串联RLC电路和并联RLC电路是两种基本的电路配置,虽然它们使用相同的元件(电阻、电感、电容),但其电气特性、谐振频率和Q因数有显著的差异。

4.1 串联RLC电路

在串联RLC电路中,电阻、电感和电容按顺序连接,电流通过所有元件。在谐振频率下,电感的感抗与电容的容抗相等,电路的总阻抗为纯电阻R:

Z_total = R

此时,电路的电流达到最大值,能量在电感和电容之间进行有效地交换。谐振频率f₀的计算公式为:

f₀ = 1 / (2π√(LC))

对于串联RLC电路,Q因数的计算为:

Q = f₀ / Δf

Q因数越高,电路的带宽越窄,选择性越强。

4.2 并联RLC电路

在并联RLC电路中,电阻、电感和电容是并联连接的,电压在各元件上是相同的。此时,电感的感抗和电容的容抗相互抵消,电路的总阻抗趋向于无穷大。在谐振频率下,电感和电容的总反应抵消,电路对外部信号的响应处于最强状态。

并联电路的总阻抗Z_total的计算公式为:

1 / Z_total = 1 / R + 1 / jX_L + 1 / jX_C

在并联RLC电路中,谐振频率与串联电路相同,计算公式为:

f₀ = 1 / (2π√(LC))

然而,在并联RLC电路中,由于其总阻抗在谐振时趋向于无穷大,Q因数通常较高,电路的选择性较好。

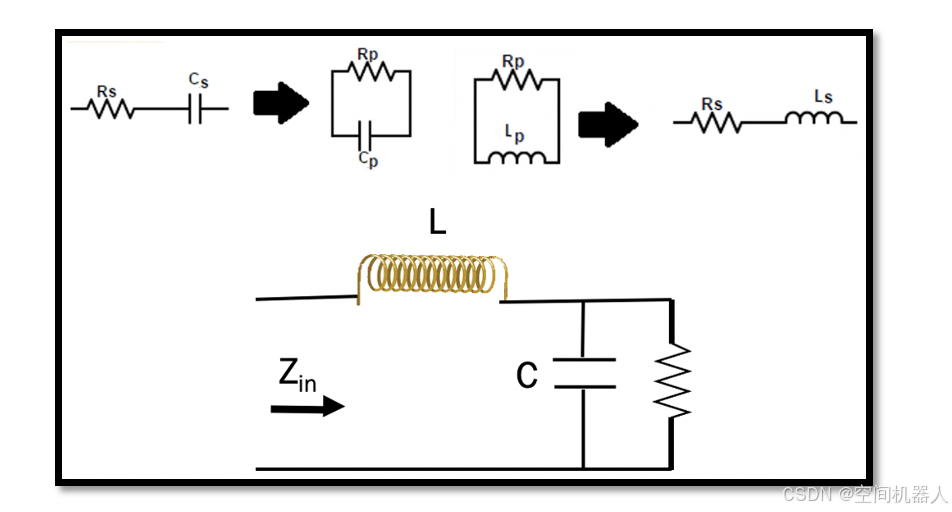

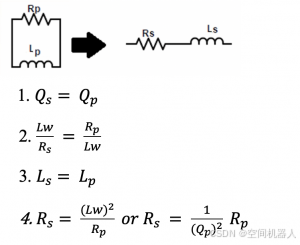

5. 串并联RLC电路转换

串并联RLC电路的转换是射频电路设计中常见的一个需求。通过串并联的不同配置,可以优化电路的阻抗匹配、频率响应和能量传输效率。串并联电路的转换关系不仅影响电路的性能,还影响其谐振频率和Q因数的表现。

在实际应用中,串联电路常用于高Q、高选择性的滤波器设计,而并联电路通常用于振荡器和低Q、宽带滤波器中。转换时需要考虑阻抗的变化。例如,串联电路的阻抗为R,而并联电路的阻抗通常较大,因此需要在转换时进行阻抗匹配,以保持电路性能的稳定性。

6. 技术瓶颈与改进方向

随着通信技术的进步,射频电路的设计面临着越来越多的挑战,尤其是在高频、高带宽和高Q因数的电路中。当前的技术瓶颈主要体现在以下几个方面:

-

高Q电路的制造难度: 随着工作频率的提高,电感和电容的寄生效应变得越来越显著,制造精度要求极高。高Q电路往往需要采用高精度的元器件和精密的电路设计技术,制造成本较高。

-

带宽限制: 高Q因数电路的带宽较窄,在宽带信号的处理上存在局限性。因此,在设计高Q电路时需要平衡带宽和选择性之间的关系,避免带宽过窄导致信号失真。

-

电路小型化与集成化: 射频电路的小型化和集成化是一个重要发展方向,但传统的分立元件组合在高频应用中可能会面临非线性和高损耗的问题。因此,集成化射频电路的设计和工艺仍需改进,以实现更高的性能和更低的功耗。

7. 结论

谐振、品质因数与串并联RLC电路的理解对于射频设计至关重要。通过深入了解谐振原理、Q因数的计算和串并联电路的转换,可以有效地优化射频电路的设计,提高信号处理效率。在面对高频、高Q的电路设计时,我们不仅需要关注谐振频率和Q因数的计算,还要考虑如何克服制造精度、带宽限制和集成化设计等挑战。未来射频电路的设计将继续朝着高集成度、低功耗、高性能的方向发展,推动通信技术的不断进步。

3233

3233

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?