目录

1. 新建文件夹,存放需要仿真的Verilog源代码和testbench测试文件

2. 使用cd命令进入该文件夹路径下,对需要编译的文件生成file.list文件

前言

零基础初学数字IC,在此整理学习笔记。学会什么写什么,与大家一起进步。

本篇主要介绍逻辑仿真工具VCS的图形化界面使用方法,下一篇介绍如何书写makefile脚本进行仿真。

利用图形化界面的方法使用VCS

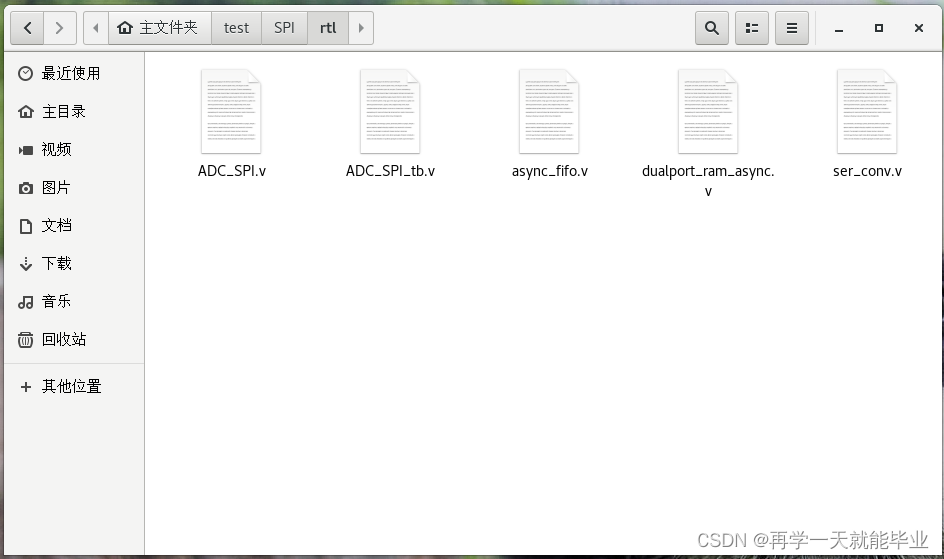

1. 新建文件夹,存放需要仿真的Verilog源代码和testbench测试文件

2. 使用cd命令进入该文件夹路径下,对需要编译的文件生成file.list文件

file.list 文件用于存放我们需要编译的所有文件的路径,方便后续使用vcs进行编译。

如果rtl文件的路径不在当前文件夹下,可以在 -name 之前加上文件的相对路径即可。

find -name '*.v' > file.list

gvim file.list

3. 使用vcs命令编译仿真需要的verilog代码

vcs -full64 -sverilog -debug_access+all -f file.list -timescale=1ns/1ns -l com.logvcs -full64 使用EDA逻辑仿真工具编译源代码

-sverilog 可以识别system verilog 语言

-debug_access+all 编译命令选项,可以保存debug过程中生成的各种文件

-f file.list 读取file.list文件中每个路径下的Verilog文件

-timescale=1ns/1ns 定义仿真时间

-l com.log 保存日志文件 com.log

+v2k 支持Verilog2001标准

编译完成后就会生成simv可执行文件,可用于后续仿真。

4. 启动VCS图形化界面

dve && 表示在后台打开dve图形化界面,不占用当前terminal

5. 进行仿真,生成波形

在命令行窗口输入run,进行仿真

仿真完成后,添加希望观察的波形

生成最终波形

总结

以上就是简单的VCS使用方法,学习笔记如果有错误的地方,欢迎大家留言纠正~

另外有VCS的使用技巧,欢迎留言补充~

这篇博客介绍了如何使用VCS进行数字IC的逻辑仿真,包括新建文件夹存放源代码,生成file.list,使用vcs命令编译,启动VCS图形化界面dve进行仿真及观察波形。适合零基础的初学者学习,逐步掌握VCS工具的使用。

这篇博客介绍了如何使用VCS进行数字IC的逻辑仿真,包括新建文件夹存放源代码,生成file.list,使用vcs命令编译,启动VCS图形化界面dve进行仿真及观察波形。适合零基础的初学者学习,逐步掌握VCS工具的使用。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?