目录

2. 生成 filelist.f 文件,罗列所有rtl文件的路径

前言

零基础初学数字IC,学会什么写什么,与大家一起进步。

书接上篇,本文主要介绍如何使用makefile脚本进行VCS逻辑仿真。

为什么我们要使用makefile脚本来进行操作呢?

我们在Window系统下进行仿真时,大部分情况下使用的都是基于图形化界面的方法——使用鼠标点击相应的按键、选项等完成各种操作。这样的操作虽然便于理解,但是代码有错误需要进行修改的时候,我们就需要将所有的图形化界面操作重新手动操作一次,相对来说有些麻烦;如果在Linux系统下,我们就可以通过编写makefile脚本的方式让软件自动一条命令一条命令自动执行,大大简化了手动操作量。

makefile脚本的方式使用VCS

1. 新建文件夹,存放需要仿真的rtl代码

在rtl文件夹下放置需要进行逻辑仿真的rtl代码与testbench测试文件

有一点需要注意,因为我们是使用脚本一键式完成整个操作过程,所以需要在testbench文件中加入以下代码,用于生成 .vpd 文件。

initial

begin

$vcdpluson;

end2. 生成 filelist.f 文件,罗列所有rtl文件的路径

find -name '*.v' > filelist.f如果rtl文件的路径与生成的 filelist.f 文件不在同一路径下,可以在 -name 之前加上存放rtl代码文件夹的相对路径即可。

3. 书写makefile脚本

在terimal下打开gvim新建一个makefile文件

gvim makefilemakefile文件如下:

all: com sim run_dve

com:

vcs -full64 -f filelist.f -R +v2k -debug_access+all -timescale=1ns/1ns -l com.log

sim:

./simv -l sim.log

run_dve:

dve -vpd vcdplus.vpd &

clean:

rm -rf *.log csrc DVEfiles *.key *.swp make all 是一条总命令,包含make com, make sim, make run_dve 三条命令;

vcs -full64: 使用64位计算支持; -f filelist.f: 读取 filelist.f 文件; -R: 编译完成后立即进行仿真;+v2k: 支持Verilog-2001标准; -debug_access+full: 启用UCLI命令和DVE,使线路步进; -timescale=1ns/1ns: 定义仿真单位; -l com.log: 生成编译日志文件;

./simv: 运行可执行文件simv; -l sim.log: 生成仿真日志文件;

dve -vpd vcdplus.vpd &: 在后台打开dve,运行.vpd 波形文件;

rm -rf: 仿真完成后删除无用的文件(可以自行决定);

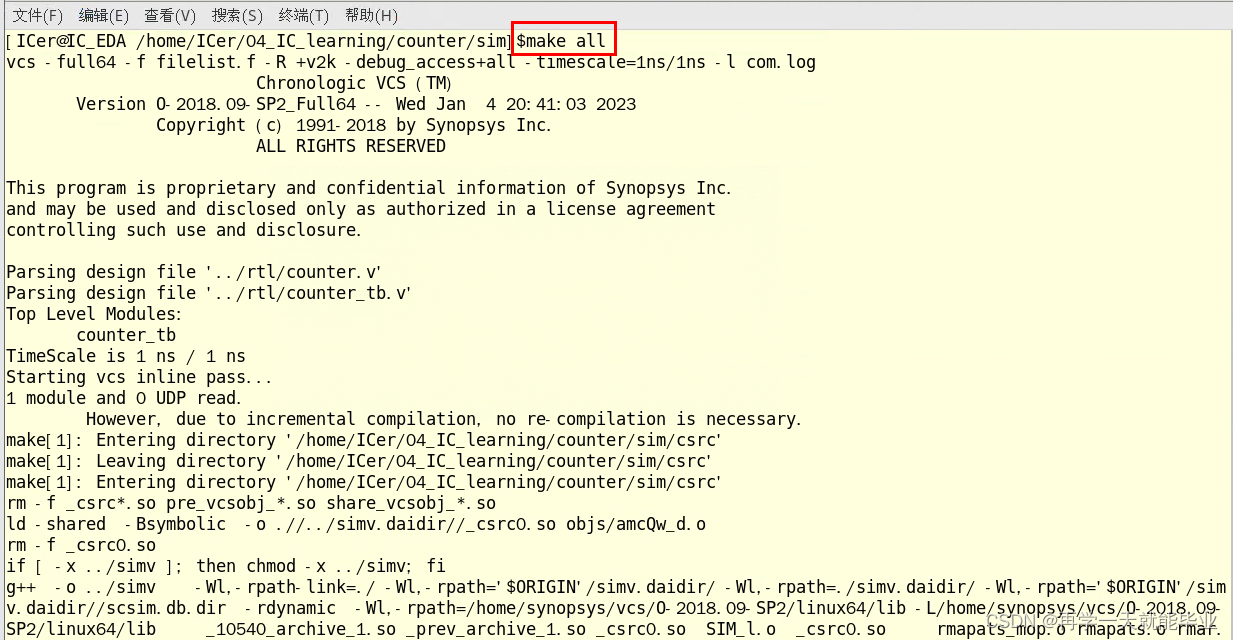

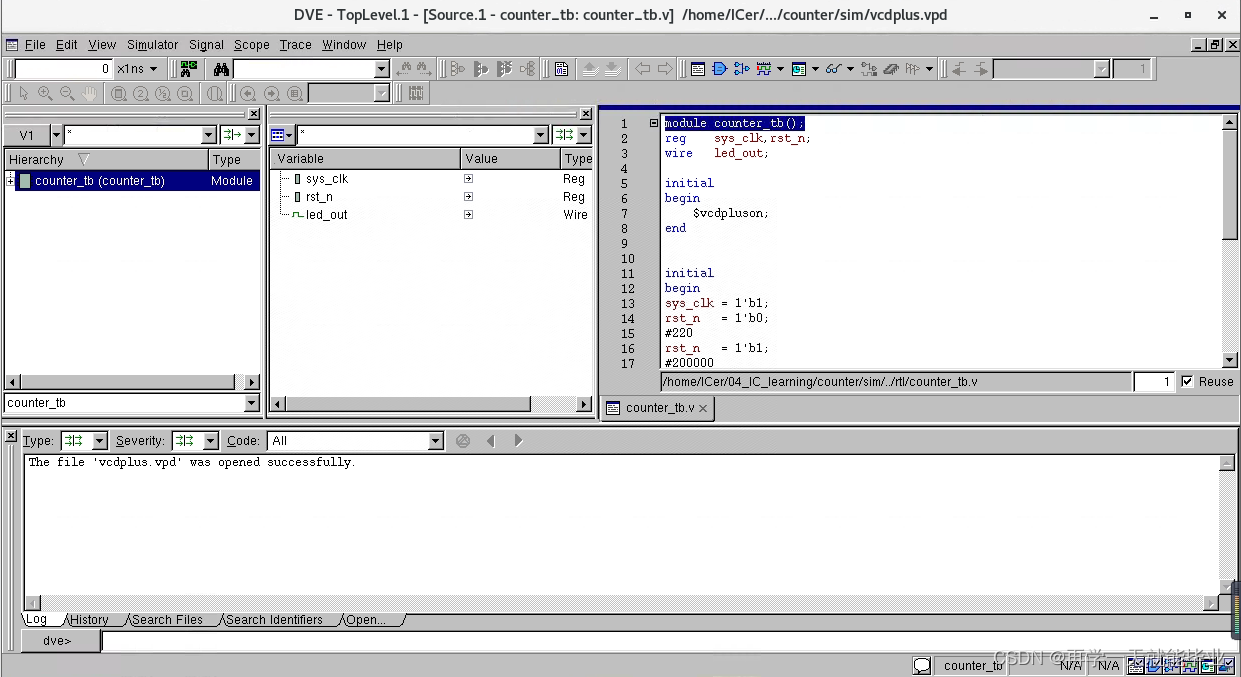

4. terimal中运行命令,进行仿真

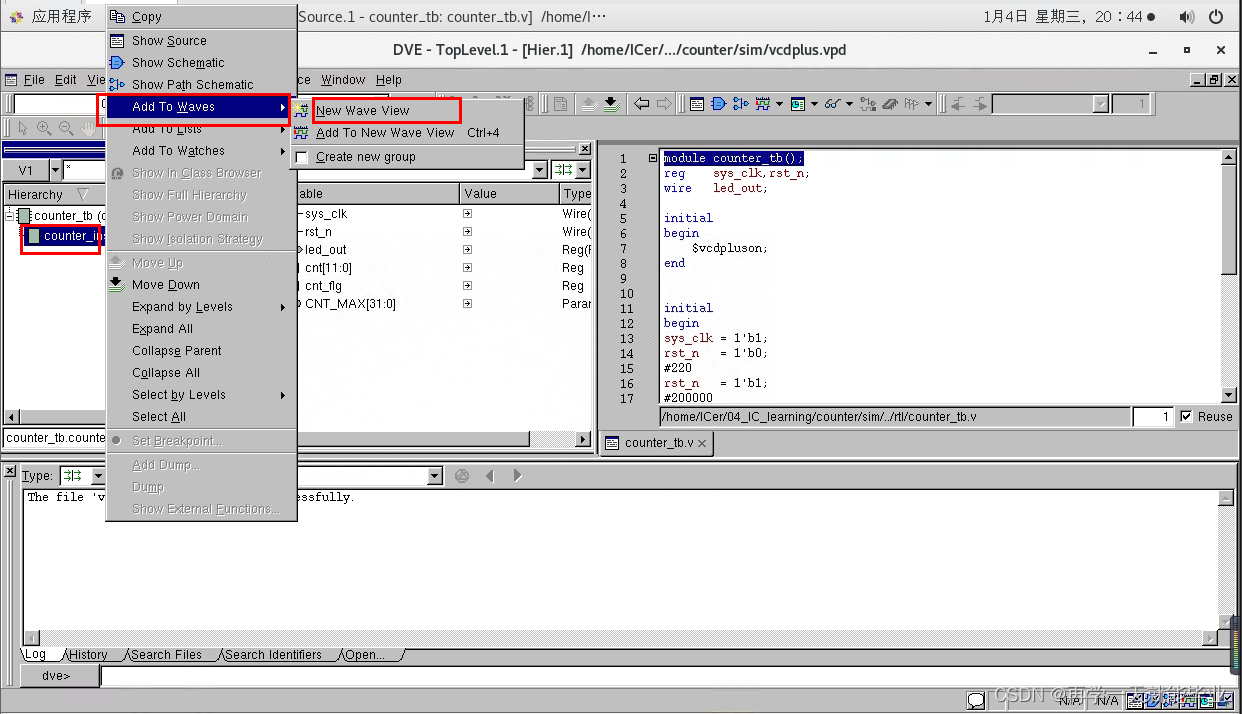

输入make all 命令之后自动执行相应命令,打开 dve GUI 界面;将想要分析的端口添加到波形窗口即可看到相应的波形。

总结

以上就是利用makefile脚本方式使用VCS的方法,笔记如果有错误的地方,欢迎大家留言纠正~

1608

1608

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?