前言

零基础初学数字IC,学会什么写什么,与大家一起进步。

本周梳理以下IC设计面试中经常问道的一部分内容:静态时序分析。

一、什么是静态时序分析?

静态时序分析就是对数字电路的时序进行预估、计算的工作流程。

在综合、布局、布线的过程中普遍都要进行静态时序分析,主要分析建立时间和保持时间。

建立时间 Tsetup:时钟上升沿到来之前数据需要保持稳定的时间;

保持时间 Thold:时钟上升沿到来之后数据需要保持稳定的时间;

传输时间 Tpd:时钟上升沿到来之后,数据从输入端到输出端的最小时间间隔。

二、为什么要进行静态时序分析?

如果电路没有办法满足建立时间与保持时间,那么电路的状态就无法确定,进入亚稳态。我们无法确定电路的输出,也无法确定电路何时能稳定到正确的电平,因此可见进行静态时序分析是非常必要的。

这里再挖一个坑,大家也可以思考一下,为什么必须满足建立时间和保持时间才能让触发器正常工作呢?或者说为什么会有建立时间和保持时间这样的要求呢?

其实这是由触发器的内部电路结构所决定的,以后有机会会发文详解。

三、如何进行静态时序分析?

这里我们以DC为例:Design Complier 会自动根据工艺库给出的电路延时和我们人为设置的时序约束来计算电路是否存在建立时间和保持时间的违例并给出裕量。

DC会计算 data arrival time 和 data required time, slack(裕量)为正表示电路可以满足要求。

setup time slack = data arrival time - data required time

hold time slack = data required time - data arrival time

所以,在综合的时候我们只需要给出时序约束即可,软件会自动进行时序分析。如何进行DC的时序约束可以参考上一篇博客:

四、如何分析时序报告?

DC做完时序分析后会得出时序分析报告,那么这个报告包含那些内容呢,我们又该如何分析?

1. 时序分析的原理

时序路径

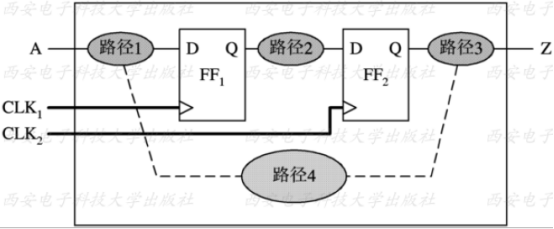

时序路径是一条点到点的数据通路,数据沿着时序路径进行传递。每一条时序路径有一个起点startpoint 和一个终点 endpoint。startpoint 定义为输入端口或者寄存器、触发器的时钟引脚,endpoint 定义为输出端口或者寄存器、触发器除时钟引脚以外的输入引脚。

那么这样,我们就可以将所有的时序路径划分为以下四种:输入到寄存器,寄存器到寄存器,寄存器到输出,输入到输出,如下图所示:

更详细的来说:(注意具体的端口)

input -----> DFF_D

DFF_CLK -----> DFF_D

DFF_CLK -----> output

input -----> output

所有时序路径中延时最长的一条路径,称为 关键路径 。

时序分析原理

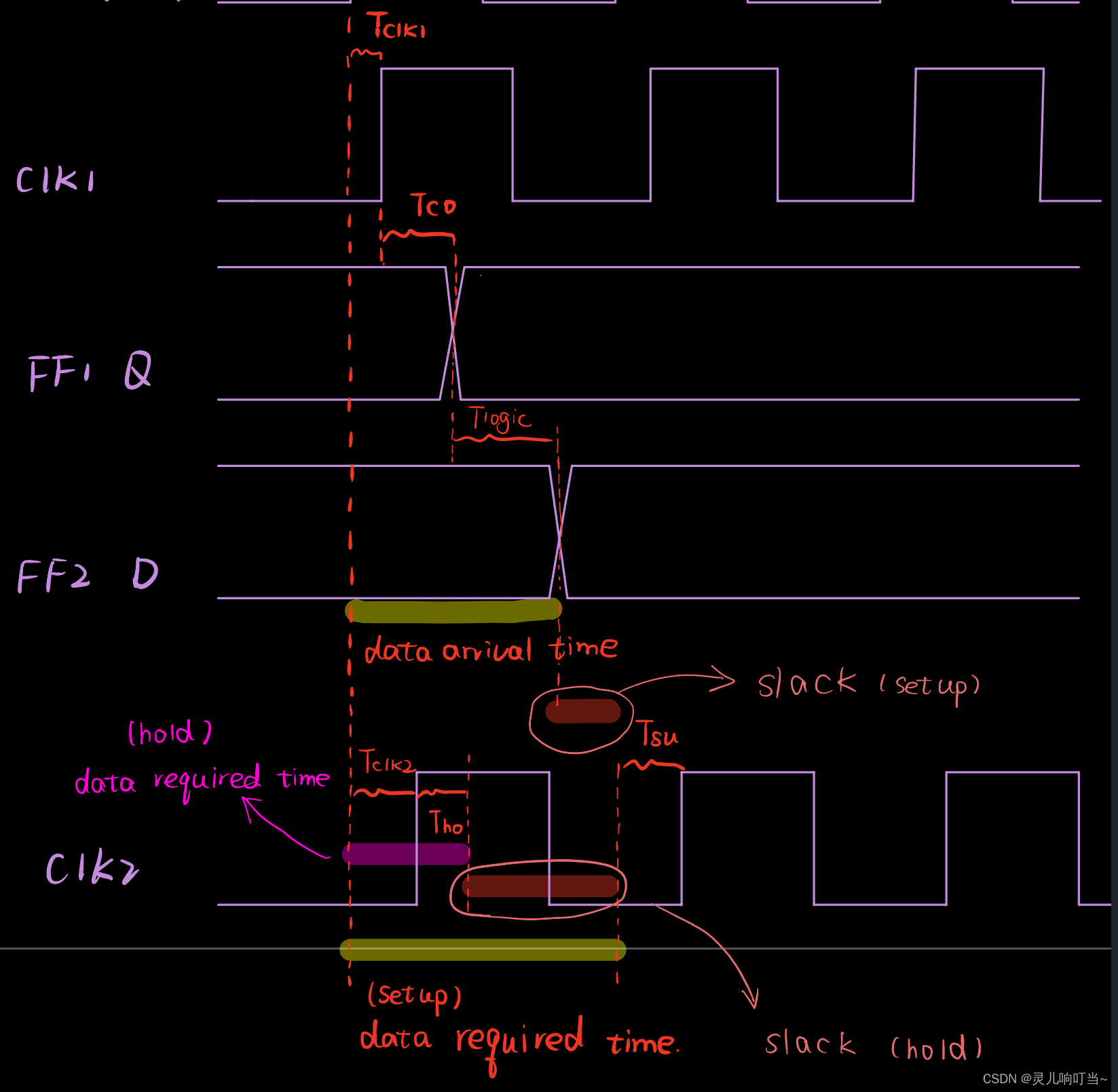

以最常见的寄存器到寄存器的时序路径为例进行分析:

Tclk1:从时钟源(比如晶振)到触发器FF1时钟引脚的延时;

Tclk2:从时钟源到触发器FF2时钟引脚的延时;

Tco:数据从触发器D引脚传输到Q引脚需要的时间;

Tlogic:组合逻辑电路的延时;

Tsu:建立时间;

Tho:保持时间;

T:时钟周期;

建立时间与保持时间的分析波形图如下:

从图中我们可以看出:

- 对于建立时间

data arrival time = Tclk1 + Tco + Tlogic

data required time = Tclk2 + T - Tsu

setup time slack = data required time - data arrival time

= T + (Tclk2 - Tclk1) - (Tco + Tlogic) - Tsu

Tclk2 - Tclk1 越大,建立时间裕量越大。

- 对于保持时间

data arrival time = Tclk1 + Tco + Tlogic

data required time = Tclk2 + Tho

hold time slack = data arrival time - data required time

= (Tco + Tlogic) - (Tclk2 - Tclk1) - Tho

Tclk2 - Tclk1 越大,保持时间裕量越小。

只有当建立时间和保持时间的裕量都大于0时,我们才认为电路是可以正常工作的。同时,也可以很明显的看出,保持时间的分析相对于建立时间来说,会提前一个时钟周期。

2. 分析时序报告

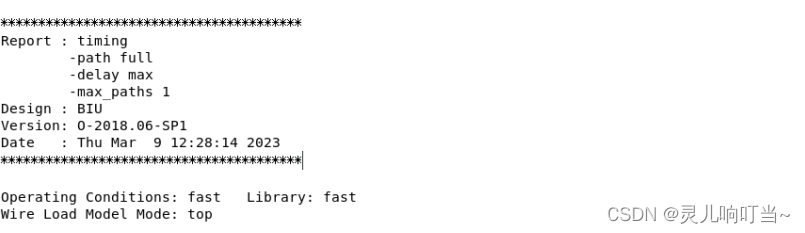

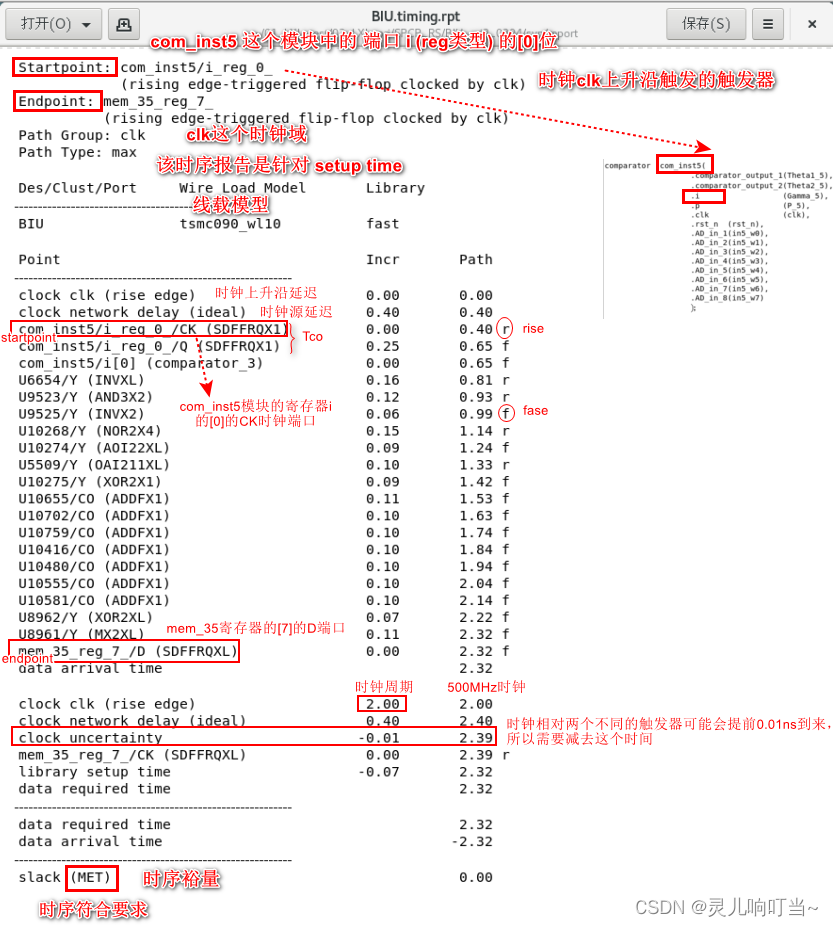

下图所示是DC综合完之后得到的一个时序报告,主要可以分为两个部分:基本信息介绍+关键路径时序。

- 基本信息

报告的基本情况:timing 表示这是一份时序报告,delay max表示是关键路径,延时最长的路径;设计的名称,DC软件的版本以及报告生成的时间。

operating conditions、Library:fast 表示工作状态是fast相对较好的情况,除此之外常见的还有 slow 和 typical;

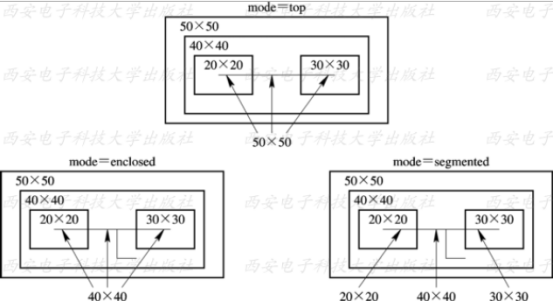

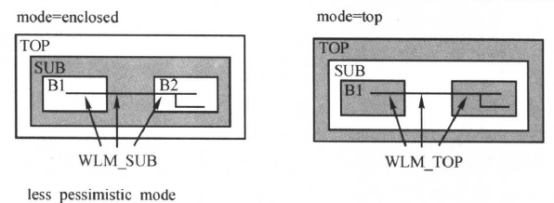

Wire Load Model Mode:top 表示线载模型的模式是 top 模式,采取的是一种相对来说比较保守的估计方式;除此之外还有 segment 和 enclosed,三种模式示意图如下所示:

一个顶层模块TOP,包含了一个子模块SUB,该子模块SUB又包含了两个更小的子模块B1和B2,他们的线载模型分别为50*50,40*40,20*20 和 30*30。现在有一条连线横跨了B1和B2两个子模块,并处在子模块SUB中,该连线的线载模型应该采用哪一种?

mode = top 是一种相对比较悲观的方式,该连线采用顶层模块的线载模型,因为顶层模块的设计规模最大,所以线载模型最悲观,为50*50;

mode = enclosed 是一种比较不悲观的方式,该连线的线载模型会选择完全包裹住该连线的模块的线载模型,也就是子模块SUB,40*40。

mode = segment 表示将这条连线根据所处的不同模块划分开,每一块分别采用所处模块的线载模型,即20*20,30*30,40*40。

- 关键路径时序

如图所示,首先说明该关键路径的 startpoint 和 endpoint,括号里会说明这个端点是触发器还是输入或者输出端口等信息,图中的 startpoint 和 endpoint 都是时钟上升沿触发的触发器。

path group 说明这条路径处在哪一个时钟域控制下,path type 说明这条路径分析的是建立时间还是保持时间,max 表示建立时间,min 表示保持时间。

wire load model,Library:在某个工艺库下的某个线载模型。

整条关键路径列出 data arrival time 和 data required time 分别进行分析,point 一列表示的是路径的每一步走到的器件的引脚的名称,incr 表示每一小段路劲的延时,path表示当前走过的路劲的总延时。最后,slack 给出该关键路径的时序裕量,裕量大于等于0(MET)表示路径满足时序要求,小于0(VOILATE)表示时序违例。

总结

以上就是今天学习的静态时序分析相关的内容,欢迎大家一起讨论交流~

参考资料:

Tcl与Design Compiler (六)——基本的时序路径约束 - IC_learner - 博客园 (cnblogs.com)

Tcl与Design Compiler (七)——环境、设计规则和面积约束 - IC_learner - 博客园 (cnblogs.com)

静态时序分析(原理最清晰版本) - 知乎 (zhihu.com)

2660

2660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?