文章目录

10.pci

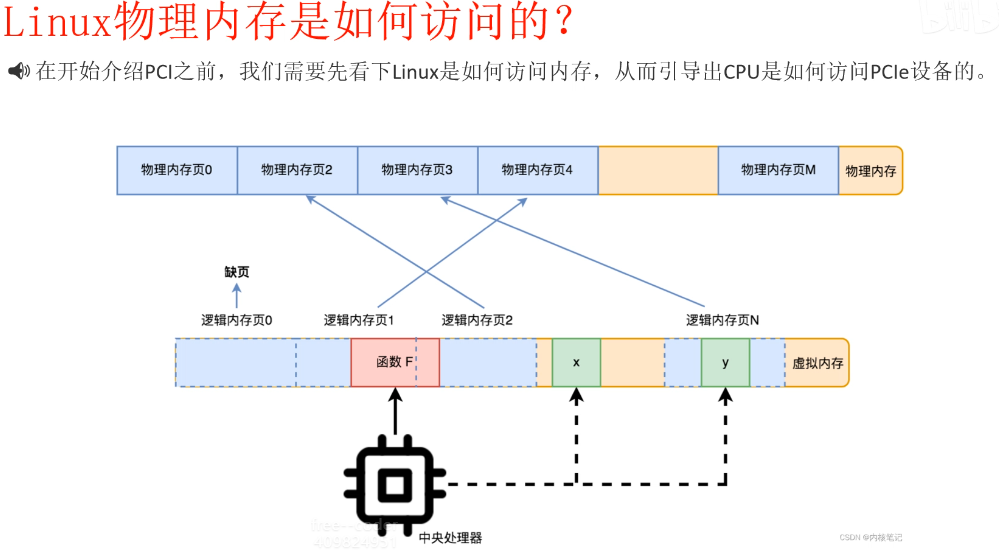

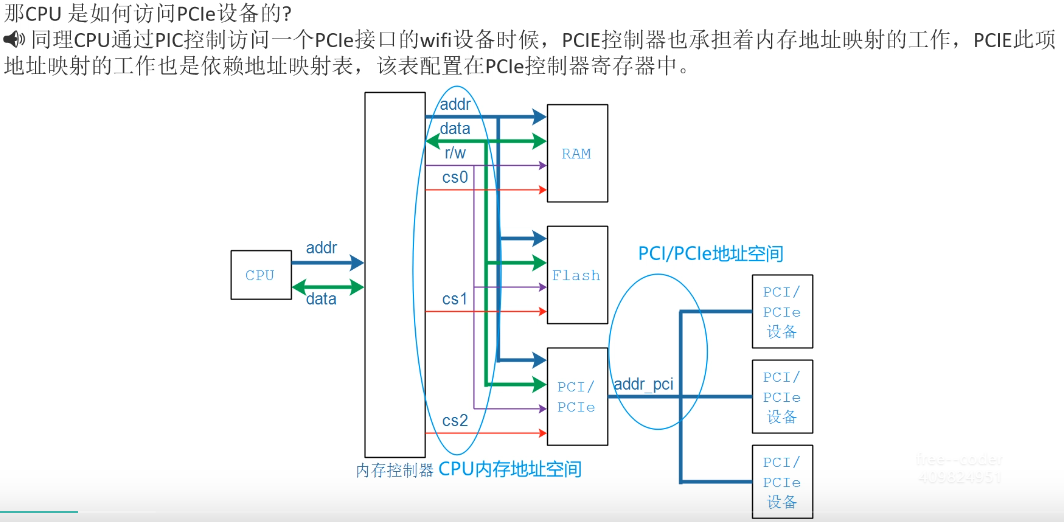

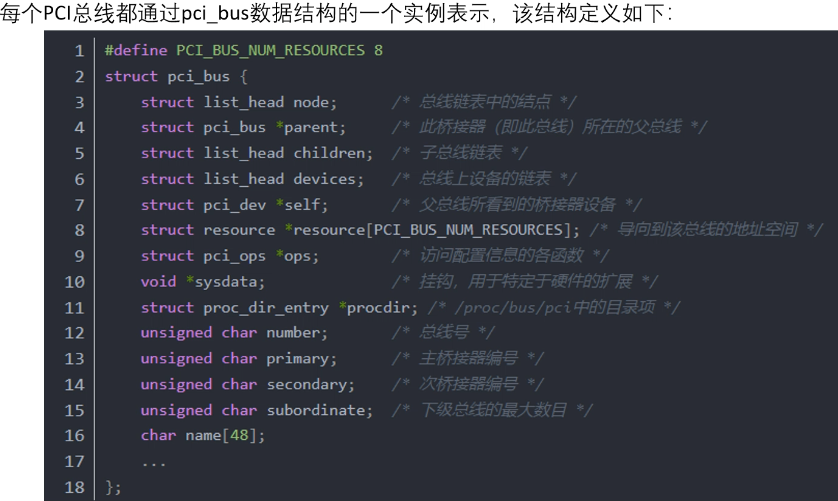

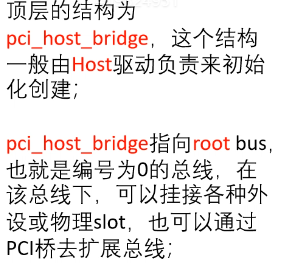

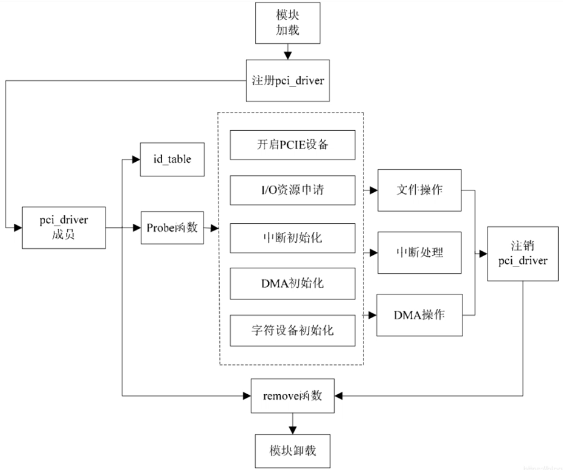

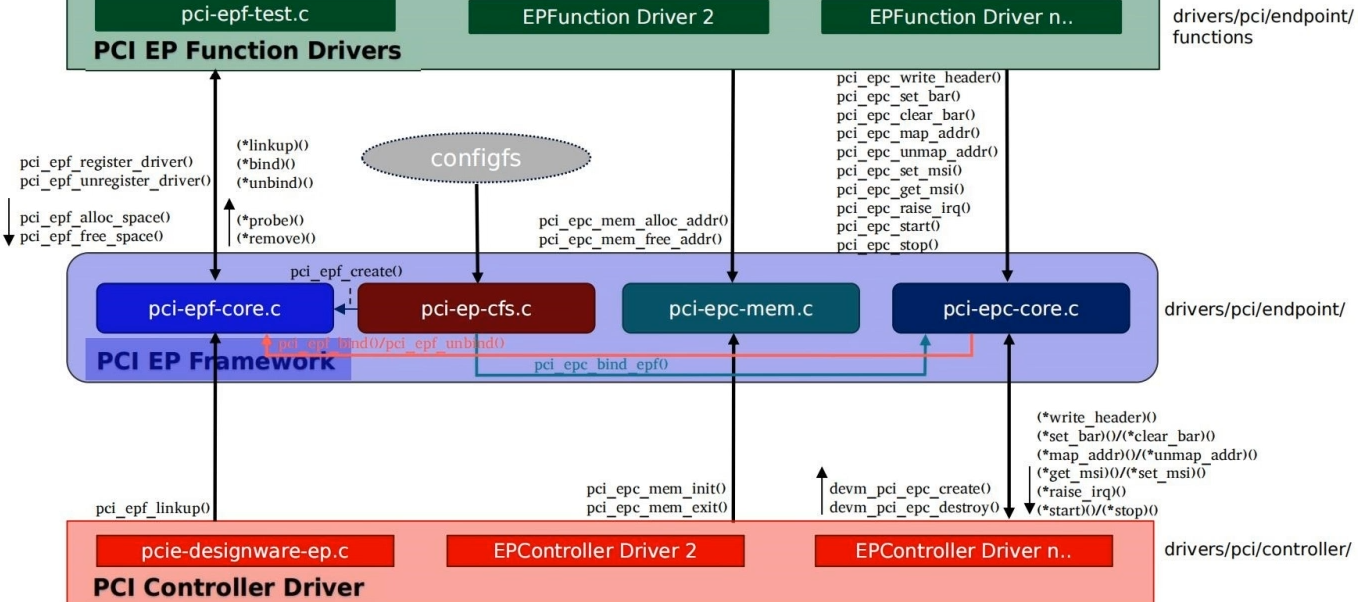

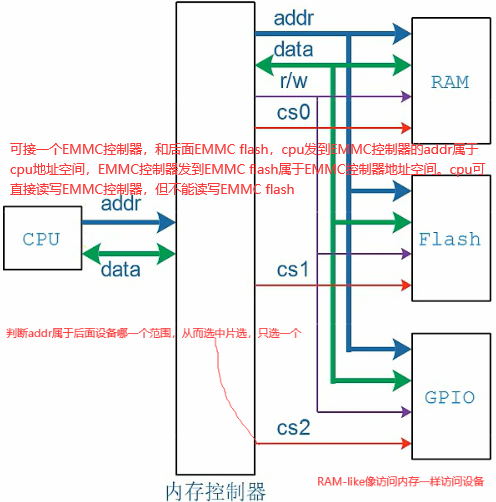

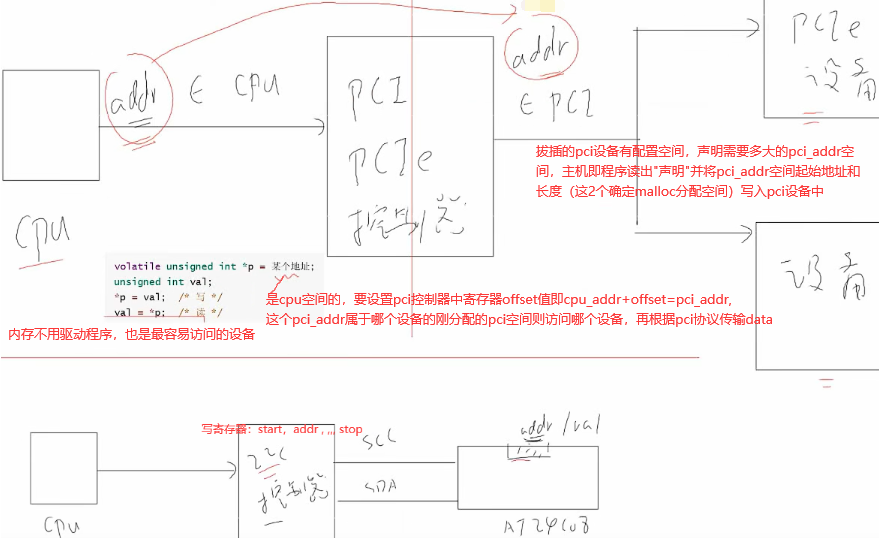

6.PCI设备驱动:pci是一种标准总线可实现块/网络/字符设备驱动,一部分是pci总线部分,另一是设备业务部分(和具体设备有关不讨论)

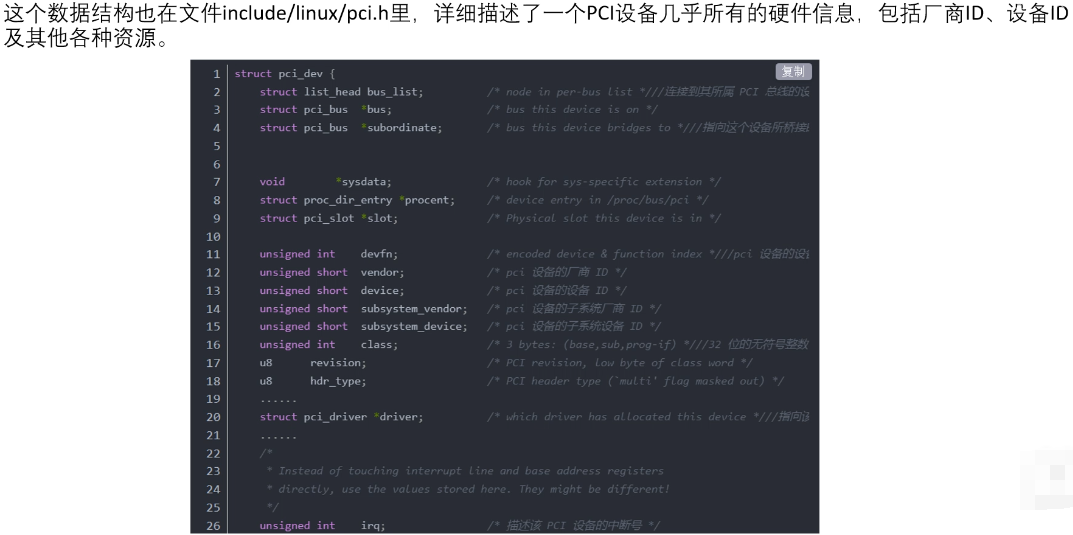

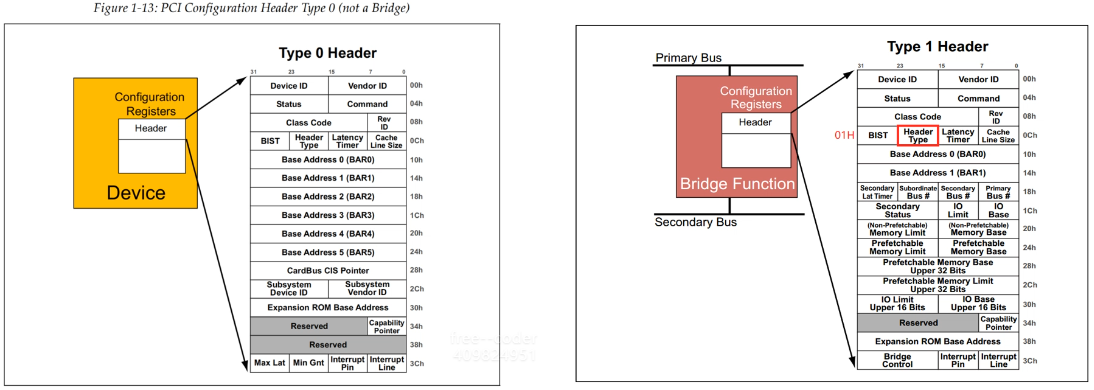

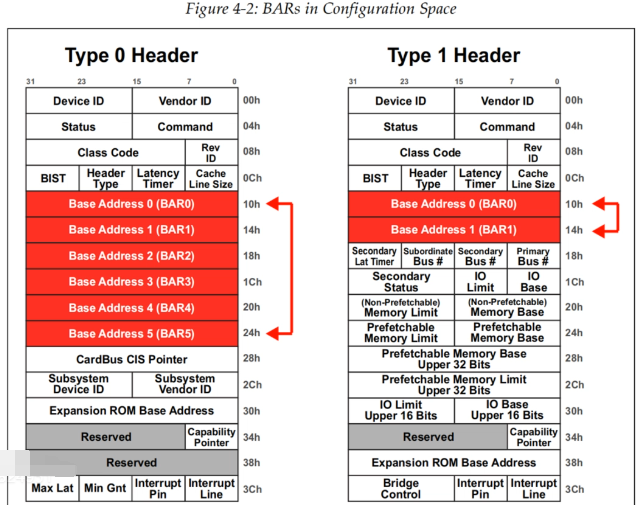

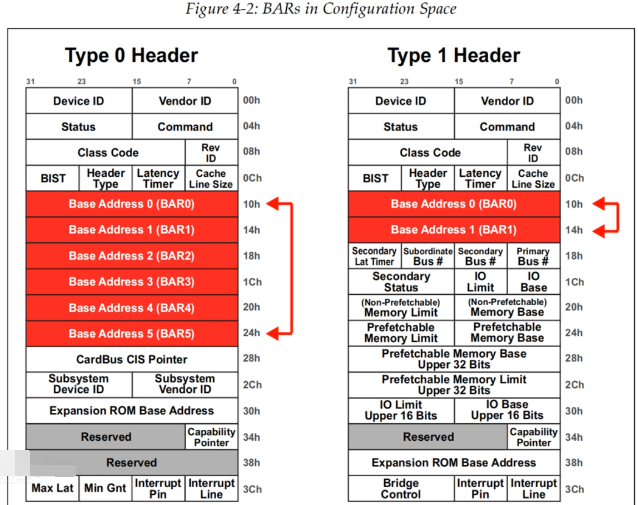

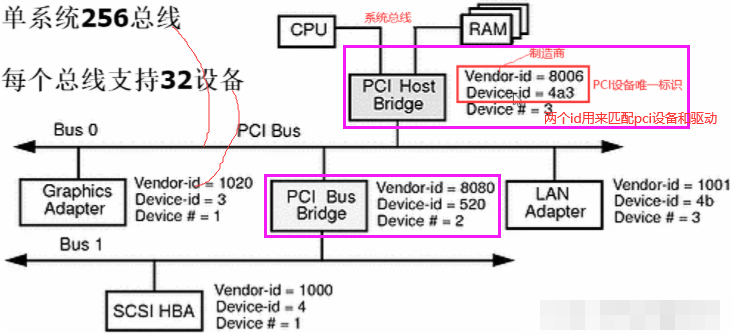

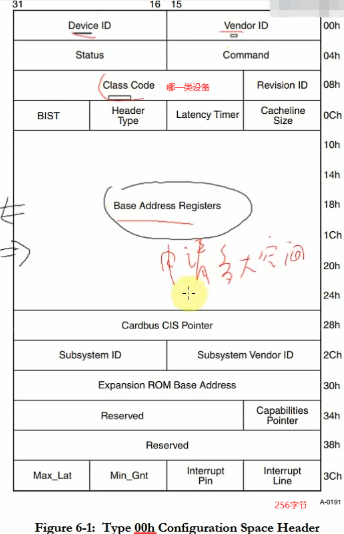

如下是PCI设备的配置寄存器值:每个PCI设备中都有一个配置区域,这个区域保存了PCI设备信息,下图是前64字节内容(标准化的)。

// pci_skel.c

/*

struct pci_device_id 用这结构体构造一个数组,数组中包含驱动支持的所有设备

PCI_DEVICE() 这个宏通过vendor-id和device-id填充上面pci_device_id结构体内容

PCI_DEVICE_CLASS() 通过class类填充pci_device_id结构体内容

MODULE_DEVICE_TABLE() 上面填充好结构体构造的数组后,调用MODULE_DEVICE_TABLE()宏,导出pci_device_id结构体到用户空间,使热插拔和模块装载系统知道什么模块针对什么硬件设备

struct pci_driver 利用这结构体将驱动注册到内核中

pci_register_driver() 注册

pci_unregister_driver() 注销

在读取pci设备的配置寄存器或io空间/io地址时,需要先如下调用:

pci_enable_device() 激活/初始化pci设备,比如唤醒设备、读写配置信息等

pci_disable_device() 关闭设备

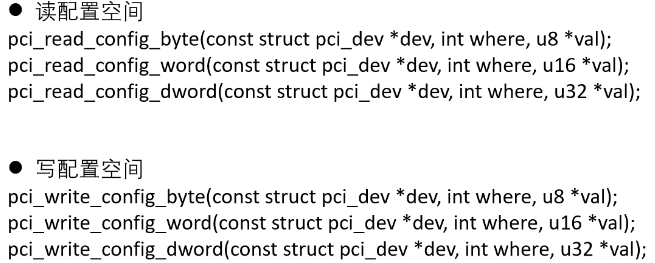

如下内核提供一系列函数读取pci设备配置信息

pci_read_config_byte() 8位

pci_read_config_word() 16位

pci_read_config_dword() 32位

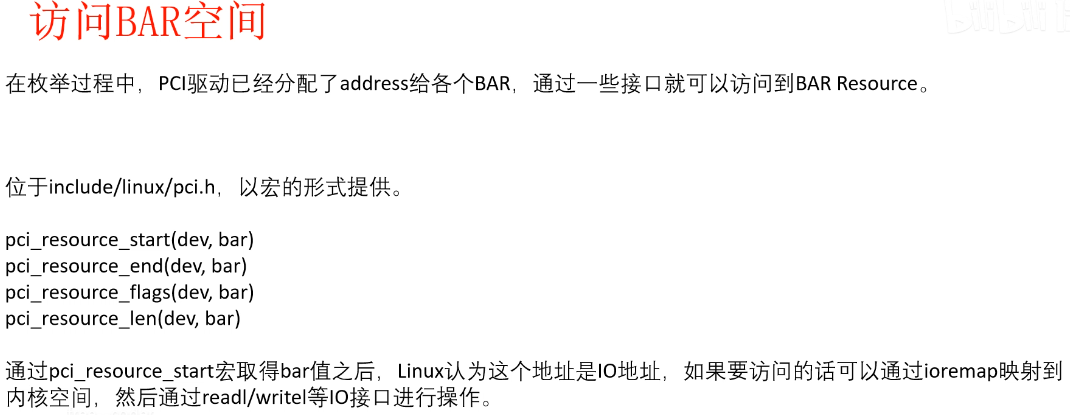

pci_resource_start() 获取区域信息(bar info) pci支持6个区域(io端口/io内存),获取io空间起始地址

pci_resource_end() 获取io空间结束地址

pci_resource_flags() 获取io空间标志信息

pci_request_regions() 获得io空间地址后,调用这行函数申请这片区域,跟request_mem_region()一样

pci_release_regions()

pci_ioremap_bar() 物理地址映射到虚拟地址空间,跟ioremap一样,作了必要的检查

pci_set_drvdata() 设置驱动私有数据

pci_get_drvdata() 获取驱动私有数据

*/

#include <linux/module.h>

#include <linux/pci.h>

struct pci_card //私有数据

{

//端口读写变量

resource_size_t io; //io空间起始地址

long range,flags; //空间大小,空间标志

void __iomem *ioaddr; //地址被映射后的虚拟地址

int irq; //pci设备中断号

};

static struct pci_device_id ids[] = { //pci_device_id里面包含这驱动支持的所有pci设备

{ PCI_DEVICE(PCI_VENDOR_ID_INTEL, 0x100e) }, //第一个参数:厂商号。第二个参数:设备id

{ PCI_DEVICE(PCI_VENDOR_ID_INTEL,PCI_DEVICE_ID_INTEL_80332_0) },

{ 0, } //最后一组是0,表示结束

};

MODULE_DEVICE_TABLE(pci, ids); //导出到用户空间:第一个参数:总线类型。第二个参数:上面数组名称。

void skel_get_configs(struct pci_dev *dev) //测试读写配置空间

{

uint8_t val1;

uint16_t val2;

uint32_t val4;

pci_read_config_word(dev,PCI_VENDOR_ID, &val2);

printk("vendorID:%x",val2);

pci_read_config_word(dev,PCI_DEVICE_ID, &val2);

printk("deviceID:%x",val2);

pci_read_config_byte(dev, PCI_REVISION_ID, &val1);

printk("revisionID:%x",val1);

pci_read_config_dword(dev,PCI_CLASS_REVISION, &val4);

printk("class:%x",val4);

}

/* 设备中断服务*/

static irqreturn_t mypci_interrupt(int irq, void *dev_id)

{

struct pci_card *mypci = (struct pci_card *)dev_id;

printk("irq = %d,mypci_irq = %d\n",irq,mypci->irq);

return IRQ_HANDLED;

}

//11111111111111111111111111111111111111111111111111111111111111111111111

static int probe(struct pci_dev *dev, const struct pci_device_id *id) // 第一个参数pci设备结构体,第二个参数匹配的pci_device_id

{

int retval = 0;

struct pci_card *mypci;

printk("probe func\n");

if(pci_enable_device(dev)) //激活pci设备

{

printk (KERN_ERR "IO Error.\n");

return -EIO;

}

mypci = kmalloc(sizeof(struct pci_card),GFP_KERNEL); //私有数据分配一空间

if(!mypci)

{

printk("In %s,kmalloc err!",__func__);

return -ENOMEM;

}

//如下是给私有数据的属性赋值

mypci->irq = dev->irq; //给私有数据中断号赋值,内核启动时扫描pci设备,给pci设备分配中断号获取基本信息

if(mypci->irq < 0)

{

printk("IRQ is %d, it's invalid!\n",mypci->irq);

goto out_mypci;

}

mypci->io = pci_resource_start(dev, 0); //获得区域0的开始地址

mypci->range = pci_resource_end(dev, 0) - mypci->io + 1; //结束地址 - 开始地址 + 1 : 就是空间大小

mypci->flags = pci_resource_flags(dev,0); //获取区域0标志,这标志会指示这区域是io内存还是io端口

printk("start %llx %lx %lx\n",mypci->io,mypci->range,mypci->flags);

printk("PCI base addr 0 is io%s.\n",(mypci->flags & IORESOURCE_MEM)? "mem":"port"); //判断是io内存还是io端口

//retval=request_mem_region(mypci->io,mypci->range, "pci_skel");

retval = pci_request_regions(dev,"pci_skel"); //要操作这内存区域,首先要分配这内存区,作用同上行

if(retval)

{

printk("PCI request regions err!\n");

goto out_mypci;

}

mypci->ioaddr = pci_ioremap_bar(dev,0); //分配成功,就将物理地址映射到内核的虚拟地址中,作用同下行,不过pci.h提供pci_ioremap_bar就用这个

//mypci->ioaddr = ioremap(mypci->io,mypci->range); 这里变量的类型与函数参数的类型必须一致,否则会出错

if(!mypci->ioaddr)

{

printk("ioremap err!\n");

retval = -ENOMEM;

goto out_regions;

}

//申请中断IRQ并给中断号绑定中断服务子函数pci_ioremap_bar

retval = request_irq(mypci->irq, mypci_interrupt, IRQF_SHARED, "pci_skel", mypci);

if(retval)

{

printk (KERN_ERR "Can't get assigned IRQ %d.\n",mypci->irq);

goto out_iounmap;

}

pci_set_drvdata(dev,mypci); //将私有数据保存到pci设备结构体中

printk("Probe succeeds.PCIE ioport addr start at %llX, mypci->ioaddr is 0x%p,interrupt No. %d.\n",mypci->io,mypci->ioaddr,mypci->irq);

skel_get_configs(dev); //测试读写配置空间

return 0;

out_iounmap:

iounmap(mypci->ioaddr);

out_regions:

pci_release_regions(dev);

out_mypci:

kfree(mypci);

return retval;

} //当probe函数结束后就拿到了pci设备io空间地址,之后业务逻辑代码操作这io地址进行

static void remove(struct pci_dev *dev) //移除PCI设备,清除在prob函数中做的工作

{

struct pci_card *mypci = pci_get_drvdata(dev); //获得私有数据

free_irq (mypci->irq, mypci); //释放中断号

iounmap(mypci->ioaddr); //取消地址映射

//release_mem_region(mypci->io,mypci->range);

pci_release_regions(dev); //释放申请的空间

kfree(mypci); //释放私有数据

pci_disable_device(dev); //关闭pci设备

printk("Device is removed successfully.\n");

}

//11111111111111111111111111111111111111111111111111111111111111111111

static struct pci_driver pci_driver = {

.name = "pci_skel", //一般和模块名称一样即本文件名称

.id_table = ids, //支持的所有设备结构体数组的名称

.probe = probe, //当内核检测到和驱动匹配后会调用probe

.remove = remove,

};

static int __init pci_skel_init(void)

{

printk("HELLO PCI\n");

return pci_register_driver(&pci_driver); //上面结构体地址

}

static void __exit pci_skel_exit(void)

{

printk("GOODBYE PCI\n");

pci_unregister_driver(&pci_driver); //注销驱动程序

}

MODULE_LICENSE("GPL");

module_init(pci_skel_init);

module_exit(pci_skel_exit);

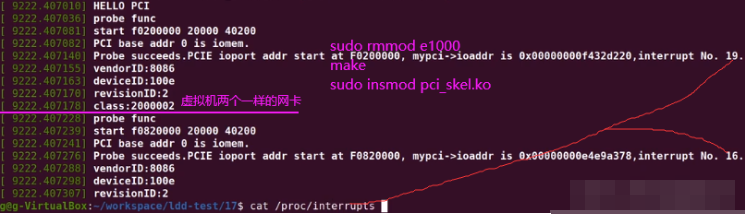

如下网卡驱动在设备启动时就加载了,需先将模块驱动移除rmmod。显示probe func说明调用了probe函数,发现了匹配的设备。mypci->ioaddr是映射后的虚拟地址。

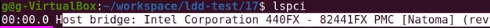

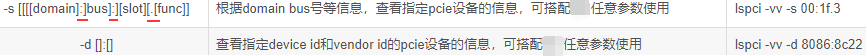

lspci:列出系统中所有pci的简略信息,总线:设备.功能。

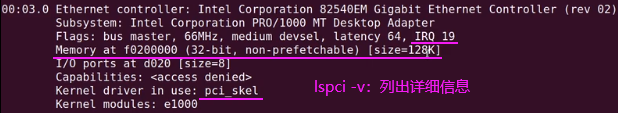

如下还有一个pci网卡信息。cat /pro/bus/pci/devices也会列出pci设备详细信息。

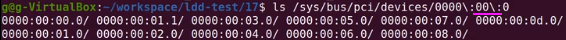

如下进入目录得到pci设备信息文件。

1.内核源码中添加驱动:单独编译devtool build linux-aspeed

// linux-aspeed/drivers/char/hello/: 3个文件

// hello.c

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/init.h>

static int __init init_hello( void )

{

printk("this is my first driver module: Hello world!\n");

return 0;//必须返回0

}

static void __exit exit_hello( void )

{

printk("this is my first driver module: Goodbey world!\n");

}

module_init(init_hello);

module_exit(exit_hello);

MODULE_LICENSE("GPL");

MODULE_AUTHOR("123");

// Kconfig

config HELLO

tristate 'Create a my hello module'

default y

help

This is a module to print Hello World!

// Makefile

obj-$(CONFIG_HELLO) += hello.o

// 修改linux-aspeed/drivers/char目录下的Kconfig文件,在尾部的endmenu之前添加:

source "drivers/char/hello/Kconfig"

// 修改linux-aspeed/drivers/char目录下的Makefile文件,在尾部添加以下:注意后面有个 / 符号

obj-$(CONFIG_HELLO) += hello/

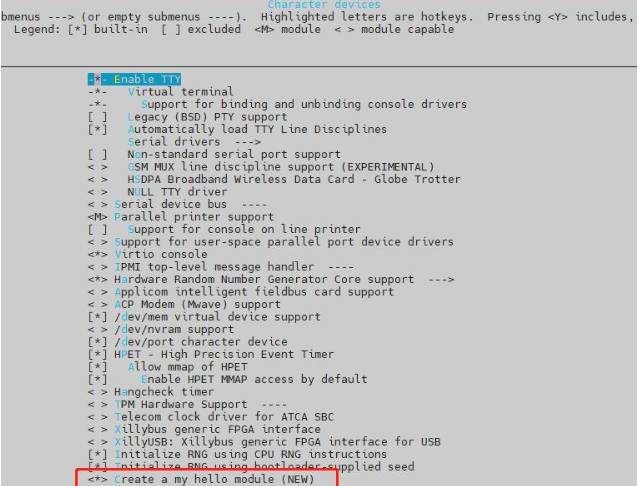

最后source,bitbake -f linux-aspeed -c menuconfig(要sudo权限弹出下面),在Device Drivers->Character devices中找到Create a my hello module选项勾上,保存退出。

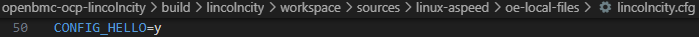

如下方式就不用上面的menuconfig,=y的话lsmod看不到。

2.

# bb中添加工具pciutils:dts添加设备生成节点,驱动添加如下:

drivers/pci/controller/Kconfig图形界面添加:config PCIE_ASPEED

drivers/pci/controller/Makefile: obj-$(CONFIG_PCIE_ASPEED) += pcie-aspeed.o aspeed-h2x.o # 移植drivers/pci/controller/pcie-aspeed.c,打开CONFIG_PCIE_ASPEED=y

gpioset gpiochip0 173=0 #switch芯片上电

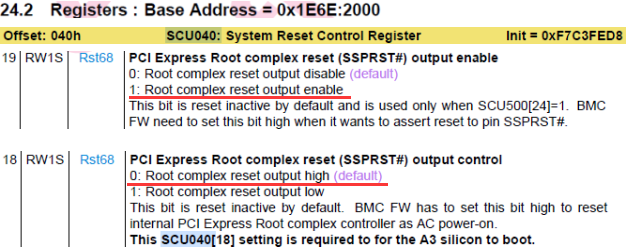

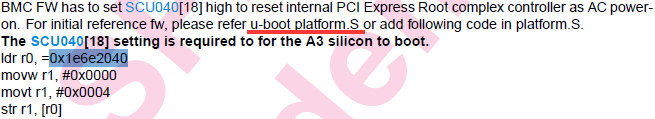

hex_value=`devmem 0x1e6e2040`

result=$(( $hex_value | 0x00080000 )) #将hex_value第19位设为1赋给result

# result=$(( $result | 0x00040000 )) #将result第18位设为1赋给result

result=$(( $result & 0xFFFBFFFF )) #将result第18位设为0赋给result

devmem 0x1e6e2040 32 $result

bDone=`gpioget gpiochip0 100` #switch FW加载完成

// uboot中173 switch上电

#define POWER_ON_CXL_SWITCH

void power_on_cxl_switch(void)

{

debug("power on cxl switch manually\n");

// GPIOV5 output // 41.3 Registers : Base Address = 0x1E78:0000 (Parallel GPIO)

*(volatile u32 *)(0x1e78008c) |= (1 << 13); // 08ch

// GPIOV5 low

*(volatile u32 *)(0x1e780088) &= ~(1 << 13);

}

__weak int board_init(void){

#ifdef POWER_ON_CXL_SWITCH

power_on_cxl_switch();

#endif

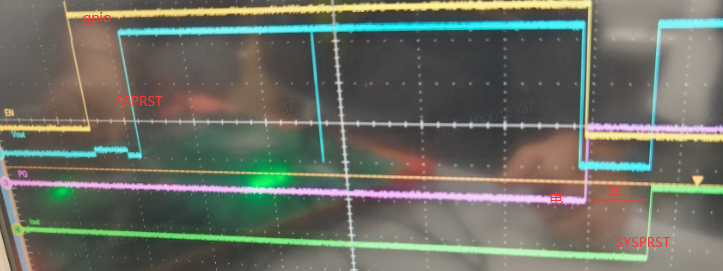

如下是将0x00040000写入0x1e6e2040。SSPRST对于BMC而言,SSPRST对端PRST对于switch而言(reset pcie功能,不是system reset重启芯片整个功能)。当i2c扫不到,需要system reset

高低高是一次reset(相当于手动跳帽一次pin),System reset and PCIe reset绑定在一起,不能为低扯着,为高释放掉(和gpio一样),为高时dev才能正常扫到。dev reset

devmem 0x1e6e2040 32 0x4ACE06C0

gpioset gpiochip0 173=0

sleep 3

devmem 0x1e6e2044 32 0x40000

2.lspci:lspci -nn(等同-n)显示设备上所有pcie设备的vendor id和device id

多了eth,ip a才看到,ifconfig只能看到有ip的eth。

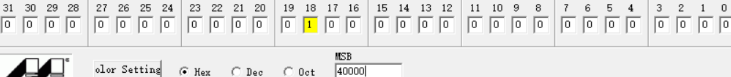

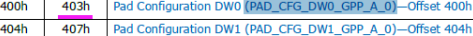

如下阴影是32位寄存器即31-0对应400-403【400,401,402(存储16-9bit),403(存储8-0bit)】大端存储,devmem2…403 b 读取一个字节。gpio dw0 : tx rx 高低电平。native function :i2c。

如下bios配gpio地址,如果是community 1组,地址就是FD00 0000 + AE 0000 + 寄存器偏移。

3.

root@ast2600-default:~# lspci

0001:80:00.0 Host bridge: ASPEED Technology, Inc. Device 2600

0001:80:08.0 PCI bridge: ASPEED Technology, Inc. AST1150 PCI-to-PCI Bridge (rev 06)

root@ast2600-default:~# echo 1 > /sys/bus/pci/rescan # 如下不是downstream bridge模式即all port显示出

[ 524.690796] pci 0001:81:00.0: [1f16:c500] type 01 class 0x060400

[ 524.698133] pci 0001:81:00.0: PME# supported from D0 D3hot

[ 524.704567] pci 0001:81:00.0: 2.000 Gb/s available PCIe bandwidth, limited by 2.5 GT/s PCIe x1 link at 0001:80:08.0 (capable of 126.028 Gb/s with 32.0 GT/s PCIe x4 link)

[ 524.722281] pci 0001:81:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 524.731671] pci_bus 0001:82: busn_res: can not insert [bus 82-81] under [bus 81] (conflicts with (null) [bus 81])

[ 524.748476] PCI: bus130: Fast back to back transfers enabled

[ 524.754856] pci_bus 0001:82: busn_res: [bus 82-81] end is updated to 82

[ 524.762337] pci_bus 0001:82: busn_res: can not insert [bus 82] under [bus 81] (conflicts with (null) [bus 81])

[ 524.773587] pci 0001:81:00.0: devices behind bridge are unusable because [bus 82] cannot be assigned for them

[ 524.784717] pcieport 0001:80:08.0: bridge has subordinate 81 but max busn 82

[ 524.792710] pci 0001:81:00.0: PCI bridge to [bus 82]

root@ast2600-default:~# lspci

0001:80:00.0 Host bridge: ASPEED Technology, Inc. Device 2600

0001:80:08.0 PCI bridge: ASPEED Technology, Inc. AST1150 PCI-to-PCI Bridge (rev 06)

0001:81:00.0 PCI bridge: Device 1f16:c500 (rev a0)

root@ast2600-default:~# lspci -tv

-[0001:80]-+-00.0 ASPEED Technology, Inc. Device 2600

\-08.0-[81]----00.0-[82]--

root@ast2600-default:~# lspci -vvvs 01:81:00.0 #有显示CXL

0001:81:00.0 PCI bridge: Device 1f16:c500 (rev a0) (prog-if 00 [Normal decode])

Control: I/O- Mem- BusMaster- SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Interrupt: pin A routed to IRQ 80

Bus: primary=81, secondary=82, subordinate=82, sec-latency=0

I/O behind bridge: 0000f000-00000fff [disabled] [32-bit]

Memory behind bridge: fff00000-000fffff [disabled] [32-bit]

Prefetchable memory behind bridge: 00000000fff00000-00000000000fffff [disabled] [64-bit]

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity+ SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=375mA PME(D0+,D1-,D2-,D3hot+,D3cold-)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [50] MSI: Enable- Count=1/1 Maskable- 64bit+

Address: 0000000000000000 Data: 0000

Capabilities: [70] Express (v2) Upstream Port, MSI 00

DevCap: MaxPayload 512 bytes, PhantFunc 0

ExtTag+ AttnBtn- AttnInd- PwrInd- RBE+ SlotPowerLimit 0W

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag+ PhantFunc- AuxPwr- NoSnoop-

MaxPayload 128 bytes, MaxReadReq 512 bytes

DevSta: CorrErr- NonFatalErr- FatalErr- UnsupReq- AuxPwr- TransPend-

LnkCap: Port #0, Speed 32GT/s, Width x4, ASPM L1, Exit Latency L1 <64us

ClockPM- Surprise- LLActRep- BwNot- ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 2.5GT/s (downgraded), Width x1 (downgraded)

TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt-

DevCap2: Completion Timeout: Not Supported, TimeoutDis- NROPrPrP+ LTR+

10BitTagComp+ 10BitTagReq+ OBFF Not Supported, ExtFmt+ EETLPPrefix+, MaxEETLPPrefixes 4

EmergencyPowerReduction Not Supported, EmergencyPowerReductionInit-

FRS-

AtomicOpsCap: Routing+

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis- LTR- 10BitTagReq- OBFF Disabled,

AtomicOpsCtl: EgressBlck-

LnkCap2: Supported Link Speeds: 2.5-32GT/s, Crosslink- Retimer+ 2Retimers+ DRS-

LnkCtl2: Target Link Speed: 32GT/s, EnterCompliance- SpeedDis-

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance Preset/De-emphasis: -6dB de-emphasis, 0dB preshoot

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete- EqualizationPhase1-

EqualizationPhase2- EqualizationPhase3- LinkEqualizationRequest-

Retimer- 2Retimers- CrosslinkRes: Upstream Port

Capabilities: [b0] MSI-X: Enable- Count=1 Masked-

Vector table: BAR=0 offset=00000000

PBA: BAR=0 offset=00000010

Capabilities: [100 v2] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr-

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 00, ECRCGenCap+ ECRCGenEn- ECRCChkCap+ ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

Capabilities: [148 v1] Device Serial Number 00-00-00-00-00-00-00-00

Capabilities: [158 v1] Power Budgeting <?>

Capabilities: [168 v1] Secondary PCI Express

LnkCtl3: LnkEquIntrruptEn- PerformEqu-

LaneErrStat: 0

Capabilities: [198 v1] Physical Layer 16.0 GT/s <?>

Capabilities: [1c8 v1] Lane Margining at the Receiver <?>

Capabilities: [210 v1] Extended Capability ID 0x2a

Capabilities: [24c v1] Latency Tolerance Reporting

Max snoop latency: 0ns

Max no snoop latency: 0ns

Capabilities: [254 v1] L1 PM Substates

L1SubCap: PCI-PM_L1.2+ PCI-PM_L1.1+ ASPM_L1.2+ ASPM_L1.1+ L1_PM_Substates+

PortCommonModeRestoreTime=10us PortTPowerOnTime=14us

L1SubCtl1: PCI-PM_L1.2- PCI-PM_L1.1- ASPM_L1.2- ASPM_L1.1-

T_CommonMode=0us LTR1.2_Threshold=0ns

L1SubCtl2: T_PwrOn=10us

Capabilities: [2a8 v1] Vendor Specific Information: ID=0002 Rev=4 Len=100 <?>

Capabilities: [3a8 v1] Vendor Specific Information: ID=0001 Rev=1 Len=038 <?>

Capabilities: [3e0 v1] Data Link Feature <?>

Capabilities: [3ec v1] Extended Capability ID 0x2f

Capabilities: [3fc v1] Designated Vendor-Specific: Vendor=1e98 ID=0007 Rev=1 Len=20: CXL

FBCap: Cache+ IO+ Mem+ 68BFlit- MltLogDev-

FBCtl: Cache+ IO+ Mem+ SynHdrByp- DrftBuf- 68BFlit- MltLogDev- RCD- Retimer1- Retimer2-

FBSta: Cache- IO- Mem- SynHdrByp- DrftBuf- 68BFlit- MltLogDev-

FBModTS: Received FB Data: 000000

Capabilities: [410 v1] Designated Vendor-Specific: Vendor=1e98 ID=0003 Rev=0 Len=40: CXL

CXLPortSta: PMComplete-

CXLPortCtl: UnmaskSBR- UnmaskLinkDisable- AltMem- AltBME- ViralEnable-

AlternateBus: 00-00

AlternateBus: 0000-0000

Capabilities: [438 v1] Designated Vendor-Specific: Vendor=1e98 ID=0000 Rev=1 Len=56: CXL

CXLCap: Cache+ IO+ Mem+ Mem HW Init- HDMCount 1 Viral+

CXLCtl: Cache- IO+ Mem- Cache SF Cov 0 Cache SF Gran 0 Cache Clean- Viral-

CXLSta: Viral-

CXLSta2: ResetComplete- ResetError- PMComplete-

Cache Size Not Reported

Range1: 0000000000000000-ffffffffffffffff

Valid- Active- Type=CDAT Class=CDAT interleave=0 timeout=1s

Range2: 0000000000000000-ffffffffffffffff

Valid- Active- Type=CDAT Class=CDAT interleave=0 timeout=1s

Kernel driver in use: pcieport

root@ast2600-default:~# lspci -vvvs 1:80:08.0 #没有显示CXL

0001:80:08.0 PCI bridge: ASPEED Technology, Inc. AST1150 PCI-to-PCI Bridge (rev 06) (prog-if 00 [Normal decode])

Subsystem: ASPEED Technology, Inc. AST1150 PCI-to-PCI Bridge

Control: I/O- Mem- BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr+ Stepping- SERR+ FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 64 bytes

Interrupt: pin A routed to IRQ 80

Bus: primary=80, secondary=81, subordinate=81, sec-latency=0

I/O behind bridge: 0000f000-00000fff [disabled] [32-bit]

Memory behind bridge: fff00000-000fffff [disabled] [32-bit]

Prefetchable memory behind bridge: 00000000fff00000-00000000000fffff [disabled] [64-bit]

Secondary status: 66MHz+ FastB2B- ParErr- DEVSEL=medium >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity+ SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [50] MSI: Enable- Count=1/1 Maskable- 64bit+

Address: 0000000000000000 Data: 0000

Capabilities: [78] Power Management version 3

Flags: PMEClk- DSI- D1+ D2+ AuxCurrent=375mA PME(D0+,D1+,D2+,D3hot+,D3cold+)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [80] Express (v2) Root Port (Slot-), MSI 00

DevCap: MaxPayload 512 bytes, PhantFunc 0

ExtTag+ RBE+

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag+ PhantFunc- AuxPwr- NoSnoop+

MaxPayload 128 bytes, MaxReadReq 512 bytes

DevSta: CorrErr- NonFatalErr- FatalErr- UnsupReq- AuxPwr+ TransPend-

LnkCap: Port #0, Speed 5GT/s, Width x1, ASPM L0s L1, Exit Latency L0s <1us, L1 <64us

ClockPM- Surprise- LLActRep- BwNot+ ASPMOptComp+

LnkCtl: ASPM Disabled; RCB 64 bytes, Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 2.5GT/s, Width x1

TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt-

#################### Width x1代表link成功,没有link成功显示X0

RootCap: CRSVisible-

RootCtl: ErrCorrectable- ErrNon-Fatal- ErrFatal- PMEIntEna+ CRSVisible-

RootSta: PME ReqID 0000, PMEStatus- PMEPending-

DevCap2: Completion Timeout: Range ABCD, TimeoutDis+ NROPrPrP- LTR-

10BitTagComp- 10BitTagReq- OBFF Not Supported, ExtFmt- EETLPPrefix-

EmergencyPowerReduction Not Supported, EmergencyPowerReductionInit-

FRS- LN System CLS Not Supported, TPHComp- ExtTPHComp- ARIFwd-

AtomicOpsCap: Routing- 32bit- 64bit- 128bitCAS-

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis- LTR- 10BitTagReq- OBFF Disabled, ARIFwd-

AtomicOpsCtl: ReqEn- EgressBlck-

LnkCtl2: Target Link Speed: 5GT/s, EnterCompliance- SpeedDis-

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance Preset/De-emphasis: -6dB de-emphasis, 0dB preshoot

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete- EqualizationPhase1-

EqualizationPhase2- EqualizationPhase3- LinkEqualizationRequest-

Retimer- 2Retimers- CrosslinkRes: unsupported

Capabilities: [c0] Subsystem: ASPEED Technology, Inc. AST1150 PCI-to-PCI Bridge

Capabilities: [100 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=1

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=00 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64- WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=Fixed TC/VC=ff

Status: NegoPending+ InProgress-

Capabilities: [800 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr-

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 00, ECRCGenCap- ECRCGenEn- ECRCChkCap- ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

RootCmd: CERptEn- NFERptEn- FERptEn-

RootSta: CERcvd- MultCERcvd- UERcvd- MultUERcvd-

FirstFatal- NonFatalMsg- FatalMsg- IntMsg 0

ErrorSrc: ERR_COR: 0000 ERR_FATAL/NONFATAL: 0000

Kernel driver in use: pcieport

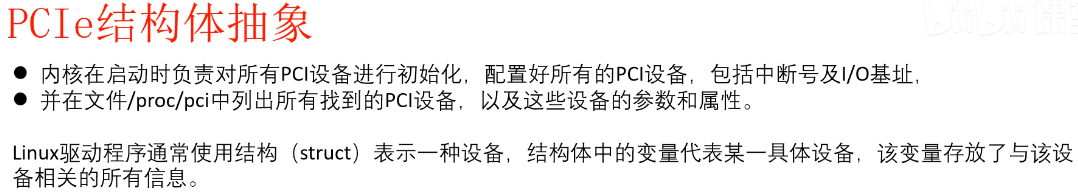

4.pcie

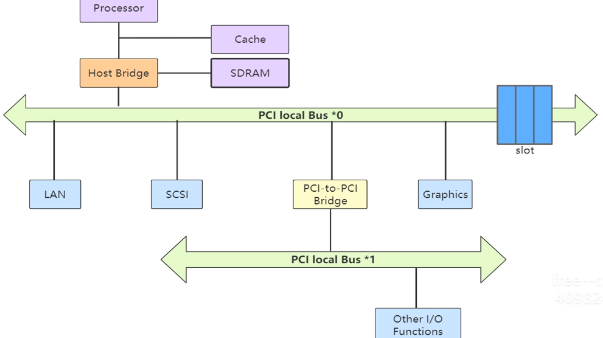

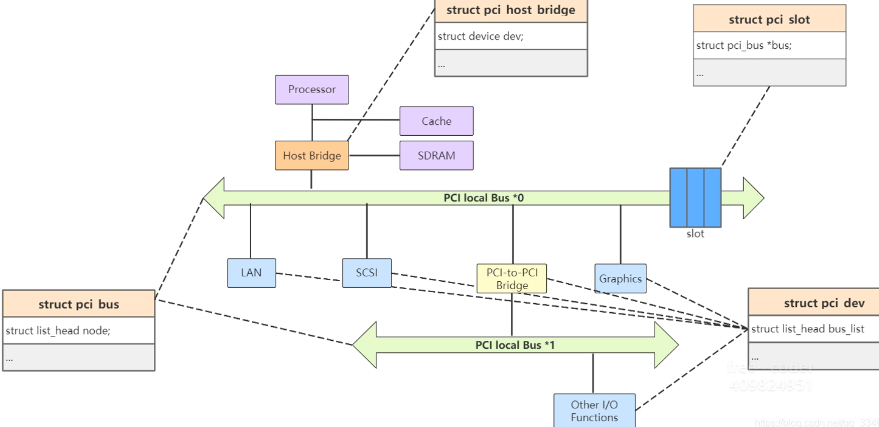

pci插槽插声卡,网卡,视频卡。pcie(express快)是pci的升级也是intel提出。

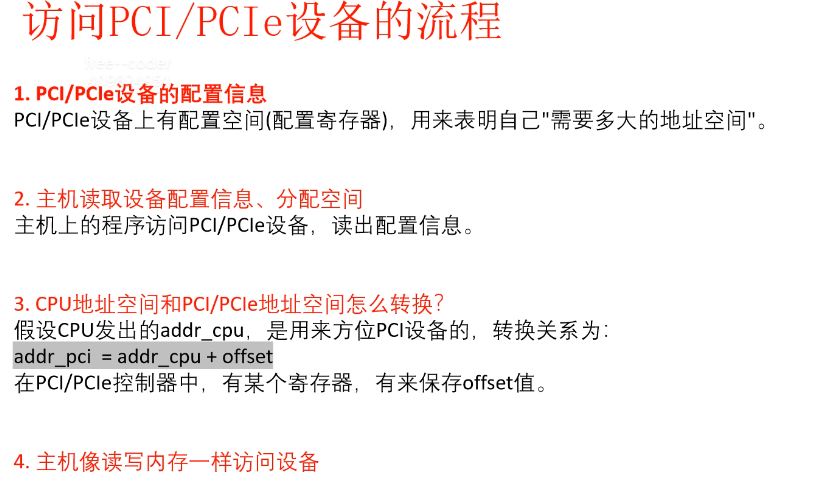

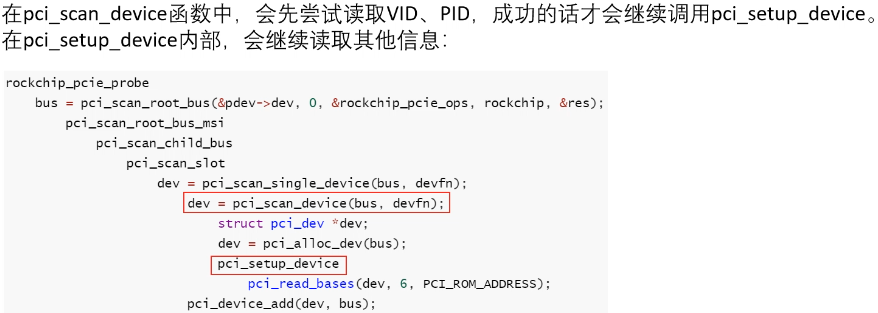

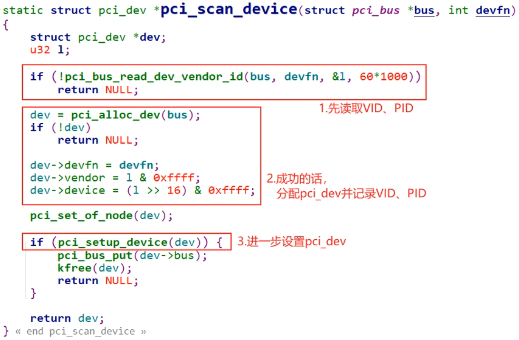

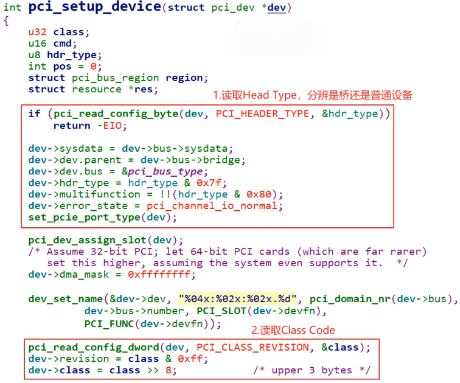

主机即pci驱动程序初始化会扫描设备即读出配置寄存器,知道了是某类型寄存器和想申请多大空间。所以先配置pci设备后就可像内存一样读写。

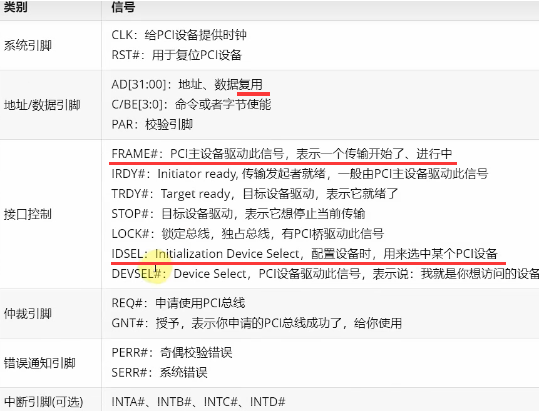

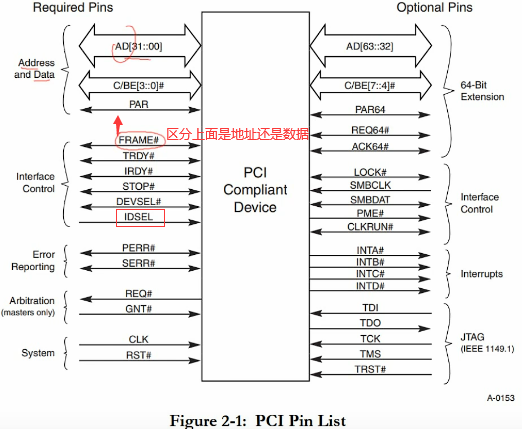

要弄清上面的配置过程,要知道pci总线上有哪些硬件信号:

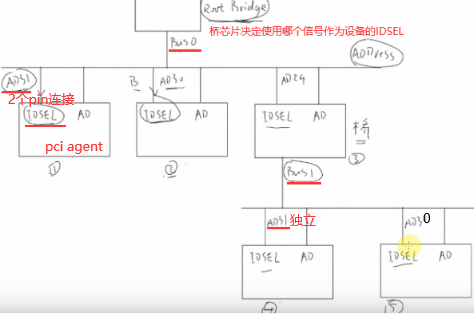

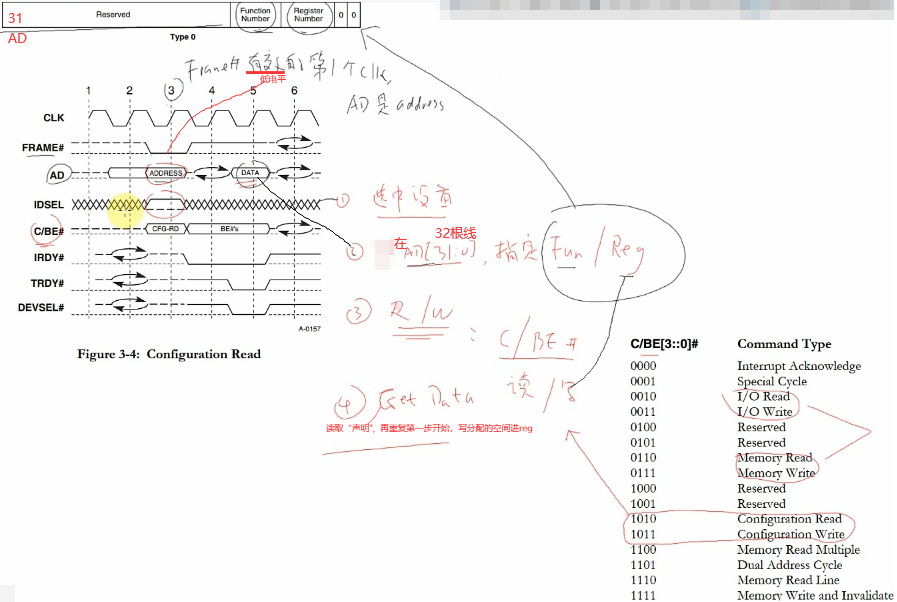

如下是pci3.0规范:一开始配置(如读addr空间)时,怎样才能选中哪个设备去配置?用IDSEL引脚选中物理设备目的是读取256字节的配置寄存器

一个pci设备最多有8种功能,每种功能都有256字节的配置寄存器,怎样选中某一种功能,再怎么选中功能里哪一个寄存器?

如下第2,3步骤反一下。

如上一个设备就被配置好了地址和范围写入下面reg,程序就能像访问内存一样访问pci设备。如下Header Type=00是普通设备(非桥)。

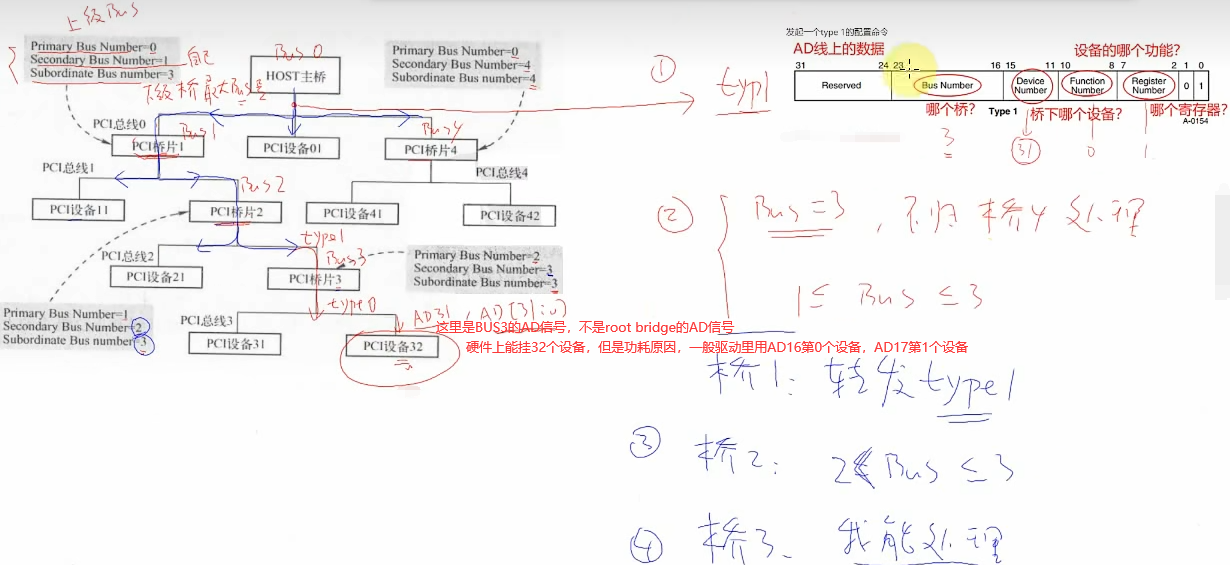

如下配置bridge:IDSEL后读headtype寄存器是1后,则发type1命令。

235

235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?