Descriptor描述符

作用:指定DMA传输中,source,destination 和传输长度。

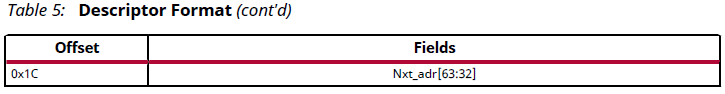

由driver产生且存储在host memory中,格式:

(PG195-Page25)

The DMA has Bit_width * 512 deep FIFO to hold all descriptors in the descriptor engine. This

descriptor FIFO is shared with all selected channels.

例如:gen3x16 4H2C 4C2H, AXI data width 512bits,

fifo depth = 512bit512 = 64Byte512=32KBytes 8个DMA engine公用该FIFO。

RQ/RC interface

RQ:requester request

user app发送请求 -------------> pcie core

RC:requester completion

pcie core返回user app请求对应的完成包

CQ/CC interface

CQ:completer requester

pcie core发送请求 --------------> user app

CC:completer completion

user app 返回pcie core请求对应的完成包

独立的 DMA engines ,能够通过AXI4-S或者AXI4-MM映射到user app

AXI4-S直接传数据*(什么格式的数据???)*

AXI4-MM则需要addr+data

H2C:

生成对PCIe的读请求(我觉得是host 写请求);传输数据给USER APP;对USER APP发送写请求

主要负责 根据最大读请求大小和内部可用资源(Data FIFO) 来拆分读请求

C2H:

生成对PCIe的写请求(with data)(我觉得应该是Host发出读请求);

注意:H2C/C2H通道和host DMA Bypass通道的区别

Bridge接收来自host 的(读)请求,基于BAR,请求通过AXI4-Lite master或CQ Bypass端口定向到内部目标用户。User app通过AXI4-Lite master或CQ bypass的读数据/读地址通道返回求情响应。Bridge打包这些数据,生成一个(读)CplD TLP,通过CC通道发给PCIe接口。

example design中

xdma_0有一个CQ bypass接口(IP core生成时设置的bypass模式)与user_app模块相连。

注:AXI4-Lite Slave不能够访问PCIe core中的寄存器,只能用于host对DMA internal register读写

IRQ module:

接收来自user logic的可配置数量的中断线;

接收一根来自每个DMA channel的中断线;

产生PCIe中断,MSI-X MSI legacy

DMA操作:

the host sets up buffer space in system memory and creates descriptors that the DMA engine use to move the data.

C2H transfer 有一个AXI源地址和一个PCIe地址作为目的地地址;H2C则反之。

example中,初始化H2C时,在DATA_STORE中写入了160*8bits数据 DATA_STORE[1024]开始

弄明白EP中 user RAM的作用

5251

5251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?