一、I2C协议、

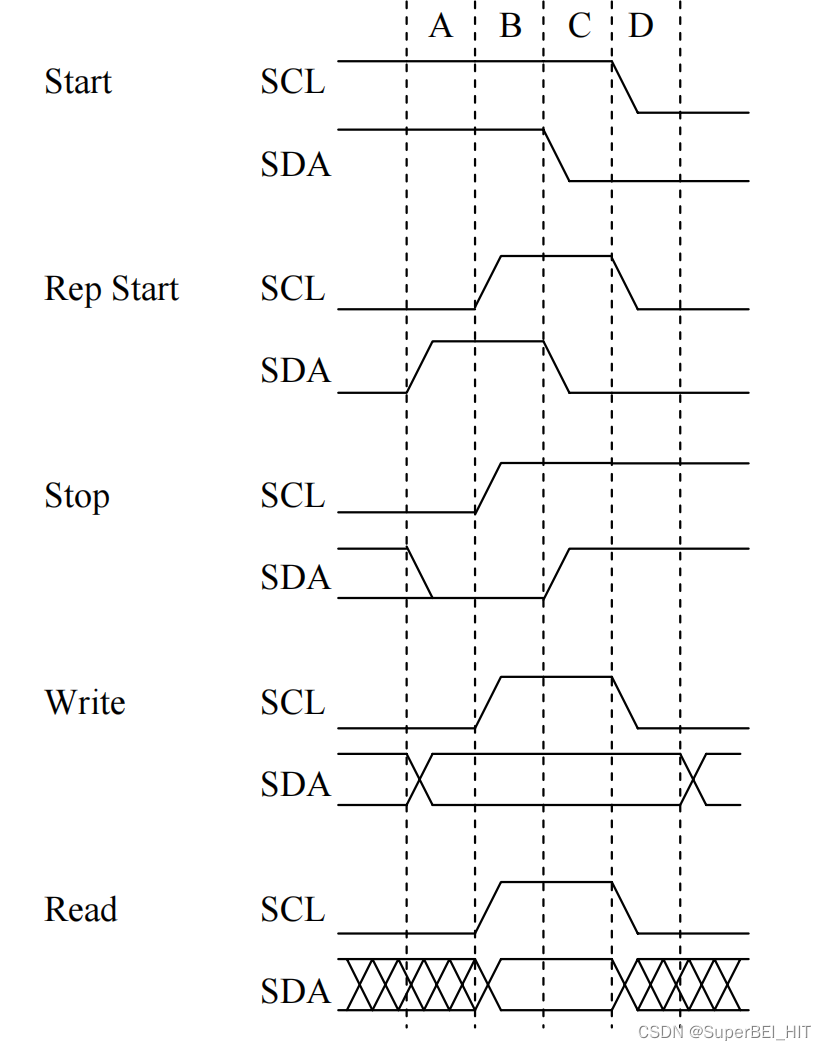

两个信号:SCL(时钟)、SDA(数据)

每传输一字节后需要1bit的回应信号ACK,

每bit在SCL的高位采样,所以,在SDA传输的数据必须在SCL的低电平进行改变,高电平保持

无论什么状态,SCL始终由Master来驱动

A Repeated START is a START signal without first generating a STOP signal. The master uses this method to communicate with another slave or the same slave in a different transfer direction (e.g. from writing to a device to reading from a device) without releasing the bus.

二、总体架构

三、i2c_master_top.v

这里使用了wishbone协议,

对于SDA和SCL信号,应在更高层次对其封装,如图

在top模块中定义了六个寄存器,方便对低层次模块进行调控,

3740

3740

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?