1、为什么要有外部存储器接口XINTF?

对于复杂的应用而言,28335内部集成的存储器FLASH、SRAM和ROM可能不够用,因此通过XINTF接口进行扩展外部存储空间。

2、了解XINTF接口

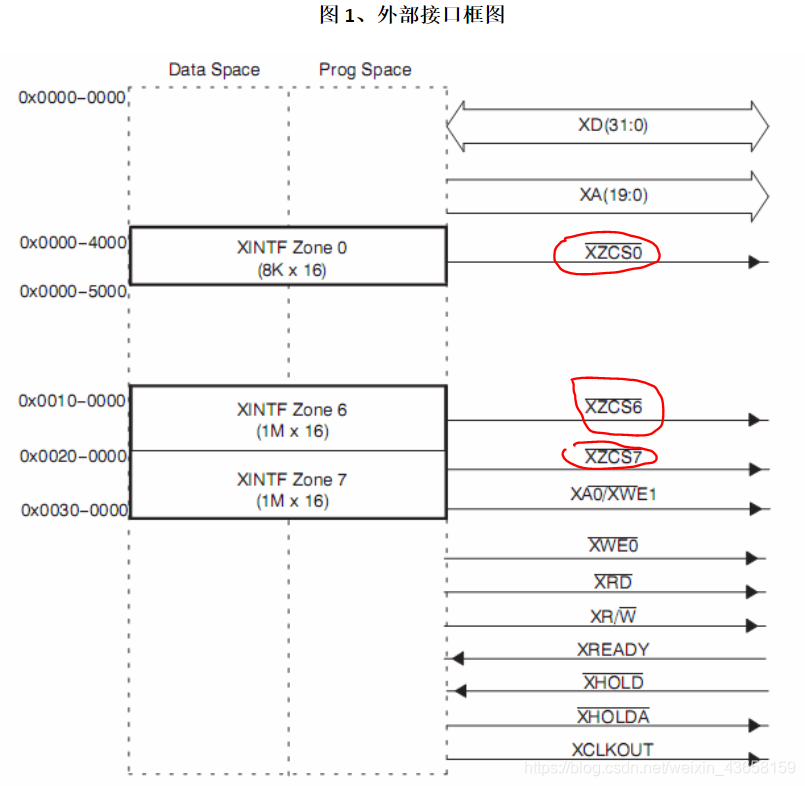

XINTF接口有3个固定存储器映射区域:Zone0、Zone6、Zone7,通过对片选线XZCS0、XZCS6、XZCS7置低选择对应读写区域。

时钟-75MHz

XINTF时钟设置为75MHz。

时钟决定访问时序,访问时序以内部时钟XTIMCLK为基准,设置为系统时钟SYSCLKOUT的一半:

SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1;

XINTCNF2.XTIMCLK = 0x01;

3、访问操作-SRAM

选择Zone0区域:

1、定义地址,如:Uint16 * SRAM_StartAddr = (Uint16 * ) 0x4041;

#define SRAM_StartAddr * SRAM_StartAddr

2、初始化,20位地址线(XA0-XA19)、16位数据线(XD0-XD15)、XZCS0片选线置低;

3、写:SRAM_StartAddr = 3600;

4、读:if(SRAM_StartAddr == 3600) return ture;

else return false

4、写后读的流水线保护

问题:28335多级流水机制,一次操作中,读相位超前于写相位

目标:写后读

实际:读后写

结果:导致读数据结果不是最新的数据,读的旧数据

注意:具有保护机制的区域,CPU会自动将读操作指令后插入空时钟周期以便在读操作前完成写操作,Zone0区域具有此保护功能。

那没有此保护功能的区域怎么解决此问题?

软件上实现保护机制的功能,使其起到相同效果。

1、在写和读的操作之间插入3个NOP指令;

2、在写和读的操作之间插入超过3个周期的指令;

816

816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?