第一章 集成电路设计概论

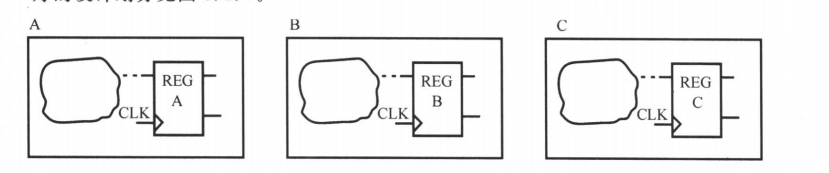

IP模块包括软IP,固化IP和硬IP三种类型。其中软IP用HDL描述;固化IP用门级网表描述;硬IP是指实现到物理版图的硅块(Silicon Block)。

1.2 集成电路系统的组成

一个常见的集成电路系统,有如下模块:

(1)数字电路模块

(2)模拟电路模块

(3)知识产权IP核

(4)边界扫描模块

(5)输入/输出PAD

(6)内存

数字电路大致可以分为数据通路(Data Path)和控制通路(Control Path)。数据通路主要指加减乘除的运算器。控制通路是控制管理数据流通和信号开关等的逻辑。

模拟电路一般有:数模转换器,将数字信号转换为模拟信号。模数转换器,将模拟信号转换为数字信号。可编程增益放大器(PGA),通过数字电路来控制模拟增益。锁相环(PLL),用于产生高频的时钟和进行时钟信号的相位校正。

知识产权IP核:推动寄存器传输级的设计自动化进程。知识产权核的设计再利用是保证系统级芯片开发效率和质量的重要手段。USB既是IP核,也是一种输入输出设备。

边界扫描电路(如JTAG):边界扫描技术的基本思想是在芯片端口和芯片内部逻辑电路之间,即芯片的边界上加上边界扫描单元(移位寄存器单元)。因为这些移位寄存器单元都分布在芯片的边界上,所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片核心和外围的输入输出隔离开来。通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。

对于芯片的输入端口管脚,可以通过与之相连的边界扫描寄存器单元把信号加载到该管脚中去;对于芯片的输出端口管脚,也可以通过与之相连的边界扫描寄存器捕获该管脚上的输出信号。芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。边界扫描链可以串行地输入和输出,通过相对应的时钟信号和控制信号,可以方便的观察和控制处在调试状态下的芯片。

输入/输出PAD

PAD是直接与外部世界相连接的特殊单元,因此必须考虑外部电路的寄生参数影响、静电保护、封装要求、电压转换、过压保护和信号完整等。I/OPAD通常分为三类:输入PAD、输出PAD和双向PAD。一般来说,I/O PAD比集成电路核心的单元有更长的延迟和更高的驱动能力。

由于连线之间的距离很近,连线之间的耦合电容会引起信号的串扰(cross talk)。串扰会影响时序,使原本收敛的设计,又产生时序违反(Timing Violation),使芯片不能正常工作。

连线的电阻寄生效应会导致显著的电压下降,从而影响芯片的供电电压和信号电平。在IC系统中,通过电源网络来供电。一个数字电路系统要能正常工作,必须为它的逻辑单元提供稳定的直流电压,并且这个电压的起伏要尽可能的小。加宽电源线可以降低电阻,从而减少压降,并且会增加允许通过的峰值电流,但是会占用过多的面积。

第二章 数字电路的高级设计和逻辑综合

2.1 RTL硬件描述语言设计

硬件描述语言支持行为级、寄存器传输级和门级三个不同级别的设计,目前人们普遍使用寄存器传输级源代码进行设计。

2.1.1行为级硬件描述语言

Behavioral Level HDL使用行为来描述设计的功能。这种行为的描述需要详细制定何时读进输入,何时对输入进行操作,何时把操作结果写到输出端口。在行为级语言时,并不需要指出由有限状态机控制设计或何时执行每个操作时钟周期。需要工具在综合时决定这些操作。

2.1.2 寄存器传输级硬件描述语言

RTL代码中通常既不包含电路的时间(路径延迟),也不包含电路的面积。

RTL代码定义了:(1)电路的寄存器结构和寄存器的数目

(2)定义了电路的拓扑结构

(3)输入/输出接口与寄存器之间组合电路的逻辑功能,寄存器与寄存器之间组合电路的逻辑功能。

这些组合电路的逻辑功能是如何由具体的电路实现,需要对电路施加约束,由工具产生。

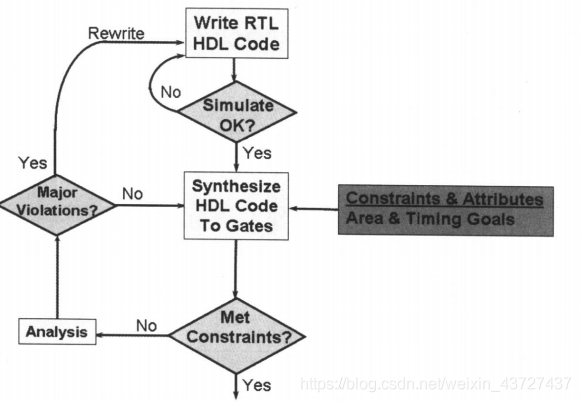

RTL源代码的功能验证完成后,用DC综合处门级电路。

2.1.3 结构化硬件描述语言

结构化描述语言定义了形成物理电路之间的连接关系。门级硬件描述语言(Gate Level HDL)或门级网表(Gate Level Netlist)是结构级硬件描述语言。用Verilog或VHDL语言描述各个逻辑单元之间的连接关系,以及输入输出端口和逻辑单元之间的连接关系。门级电路的生成一般可以由逻辑综合来实现。

2.2 逻辑综合(logic synthesis)

综合是把概念转换为可以制造器件的转移过程,而该器件能执行预期的功能。

2.1.1 逻辑综合的基本步骤

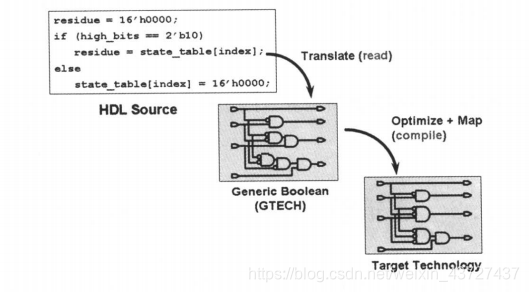

电路的逻辑综合一般由三步组成,即

综合(Synthesis) = 转化(Translation) + 逻辑优化(Logic Optimization) + 映射(Mapping)。

先通过read命令将RTL代码转换成通用的布尔等式,即GTECH(Generic Technology)格式;然后执行complile命令,该命令按照设计的约束对电路进行综合和优化,使电路能满足设计的目标或约束,并且使用目标工艺库中的逻辑单元映射成门级网表。

使用HDL语言和逻辑综合进行设计,有如下优点:

(1)提高设计效率

(2)抽象设计

(3)设计诀窍

(4)重复复用

(5)验证方便

(6)便携性强

综合的结果和设计的约束有很大的关系,通过设计的约束(design constraint)设置目标,综合工具对设计进行优化来满足我们的目标。

综合以时序路径为基础进行优化。DC在对设计做综合时,其过程包括了进行静态时序分析(Static Timing Analysis ,STA)。DC使用其内建的静态时序分析器把设计分解成多条时间路径,然后根据设计的约束对这些路径进行优化。STA计算每一条路径的延迟(Delay),然后把延迟的结果和约束进行比较,如某条路径的时间延迟大于约束的值,则该路径时序违规(Timing Violation)。这时电路不能正常工作,无法到达原来的设计目标。

2.2.2 综合工具 Design Compiler

逻辑综合包括读入HDL源代码和对设计进行优化。

在综合过程中,优化进程尝试完成库单元的组合,使组合电路能最好地满足设计的功能、时序和面积的要求。

编译(compile)是DC的一个命令,设计者使用该命令对设计进行优化。在读入设计和做完其他必要的任务后(如加上设计约束),设计者执行compile命令为设计产生优化的门级网表。

2.2.3 目标库和初始环境设置

综合 = 转化 + 逻辑优化 + 映射

技术综合库包括单元的延迟。单元的延迟与输入的逻辑转换时间(Input Translation Time)和输出的负载(Output load)有关。根据每个单元的输入逻辑转换时间和输出负载,可以在技术综合库提供的查找表中查出单元的延迟。

DC在做编译时,使用目标库(Target Library)来构成电路图。映射电路图时,DC在用目标库指定的综合库中选用功能正确的逻辑门单元,使用厂商所提供的这些门单元的时间数据计算电路的路径延迟。

DC中,target_library是保留变量,设置这个变量以指向厂商提供的综合库文件。例如

set target_library my_tech.db

连接库(link_library)是保留变量,用于分辨电路中逻辑门单元和子模块的功能。

set link_library “* my_tech.db”

DC读入设计时,它自动读入由link_library变量指定的库。

分辨门单元和模块(也叫做连接)意味着要找出网表中门单元和模块逻辑和功能,并且用实际的库单元或子模块替代他们。

第三章 系统的层次划设计和模块划分

3.1 设计组成及DC-Tcl

端口(ports)可以有方向、驱动单元、最大电容等属性和约束

单元(cells)可以有功能、连线、面积的大小和时间信息的属性

设计(designs)可以有面积、最大工作条件、功耗等的属性和约束

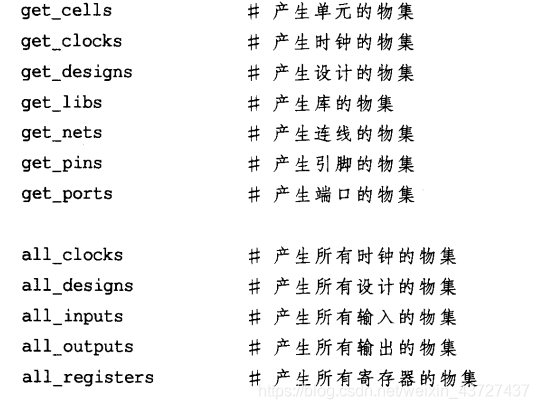

3.1.1 设计物体(Design Object)

DC中,每个设计由6个设计物体(Design Object)组成,分别是设计(design)、端口(ports)、单元(cell)、引脚(pin)、连线(net)和时钟(clock)。其中时钟是特别的端口,它存放在DC内存中,使用户自己定义的物体。

creat_clock -period 4 [get_ports CLK]

如果执行命令“set-load 5 A”,此命令并没有给DC足够的信息把负载加到哪个物体上,因为命令并没有指出物体A是端口,是连线或是引脚。这种情况下,DC把5个电容单位的负载加到自己选择的物体A上,这时物体A可能是端口,也可能是连线或是引脚。

我们可以用“get_*”命令来选择特定的物体。如果要在连线A上加上5个电容单位的负载,应用下面的命令:

set_load 5 [get_nets A]

物体可以与通用字符“*” 或 “?”一起使用。

set_load 5 [get_ports addr_bus*]

set_load 6 [get_ports "A* B*"]

3.2 层次(Hierarchy)结构和模块划分(Partition)及修改

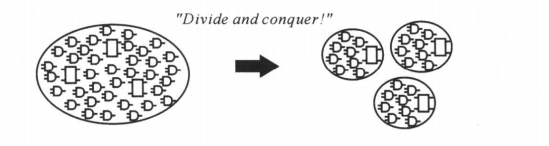

SOC设计由一些模块组成。对于设计复杂规模又大的电路,需要对它进行划分(Partitioning),然后对划分后比较简单规模又小的电路做处理。这时,由于电路小,处理和分析比较方便简单,容易较快的达到要求。再把已经处理好的小电路集成为原来的大电路。

设计时,为了得到最优的电路,需要对整个电路作层次结构的设计,对整个设计进行划分,使每个模块以及整个电路的综合结果能满足我们的目标。

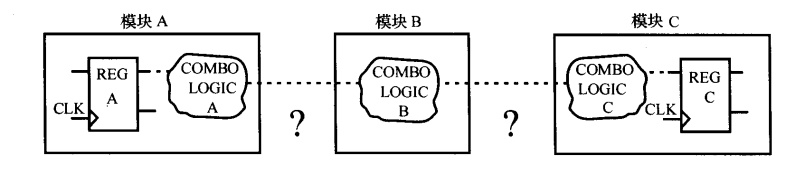

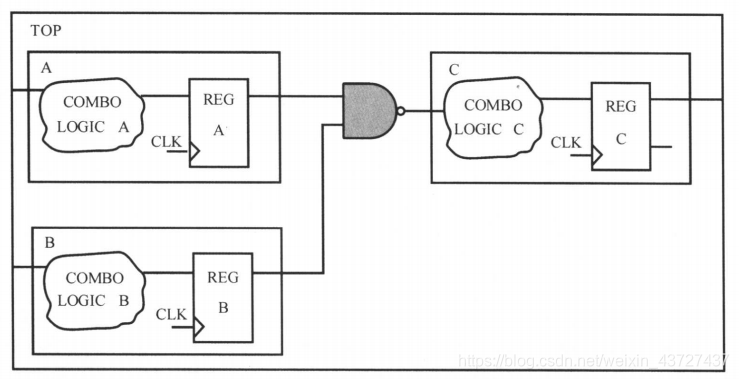

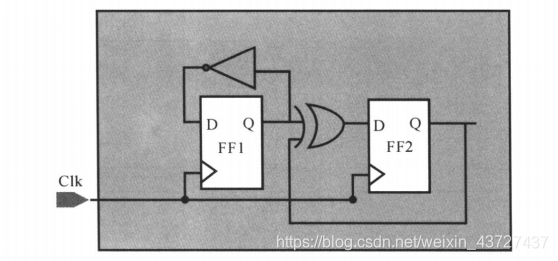

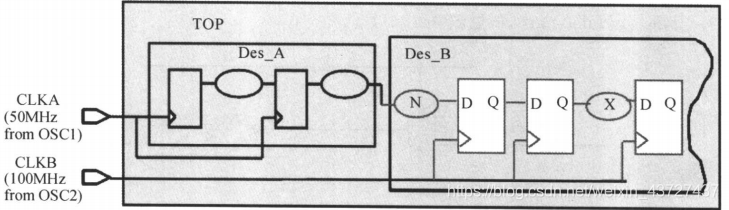

由于DC在对整个电路做综合时,必须保留每个模块端口。因此,逻辑综合不能穿越模块边界,相邻模块的组合逻辑也不能合并。从寄存器A到寄存器C的路径延时较长,这部分的电路面积较大。

将相关的组合电路合到一个模块,原来模块A、B和C中的组合电路没有了层次的分隔,综合工具中对组合电路优化的技术也能得到充分利用。这时电路的面积比原来要小,从寄存器A到寄存器C的路径的延时也短了。

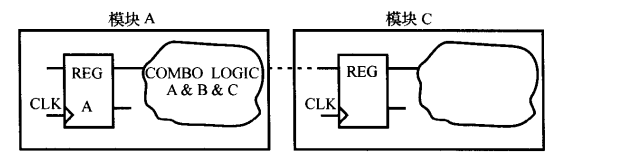

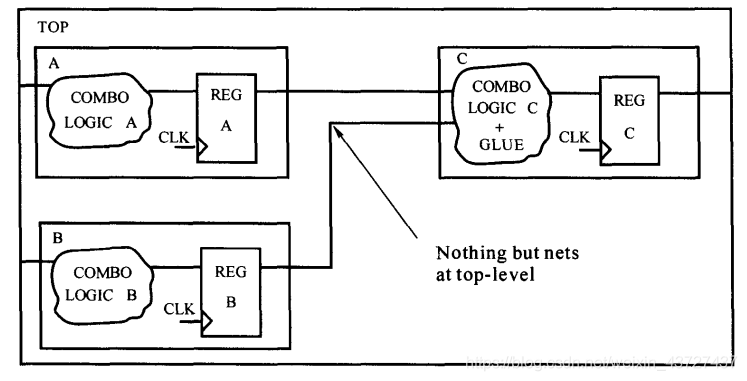

图中,模块的输出边界是寄存器的输出端。由于组合电路之间没有边界,其输出连接到寄存的数据输入端,可以充分利用综合工具对组合电路和时序电路的优化技术,得到最优的结果,同时也简化了设计的约束。图中每个模块除时钟端口外所有的输入端口延时是相同的,等于寄存器的时钟引脚CLK到输出引脚Q的延时。

胶合逻辑是连接到模块的组合逻辑,顶层的与非门仅仅是个例化的单元,由于胶合逻辑不能被其他模块吸收,优化收到了限制。如果采用由低向上的策略,需要在顶层做额外的编译(compile)。

胶合逻辑可以和其他逻辑一起优化,顶层设计也只是结构化的网表。不需要再做额外的编译。

3.2.3 模块划分的修改

对设计做编辑时,需要考虑划分模块规模的大小应与现有的计算机中央处理器(CPU)和内存资源相匹配。尽量避免下面划分不当情况:

(1)模块太小 由于人工划分的模块边界,使得优化收到限制,综合的结果可能不能是最优的

(2)模块太大 做编辑所需的运行时间可能会太长,由于要求设计的周期短,不能等太久。

按照期望的周转时间,一般模块的划分规模大约为400~800K门。对设计作综合时,比较合理的运行时间是一晚上。

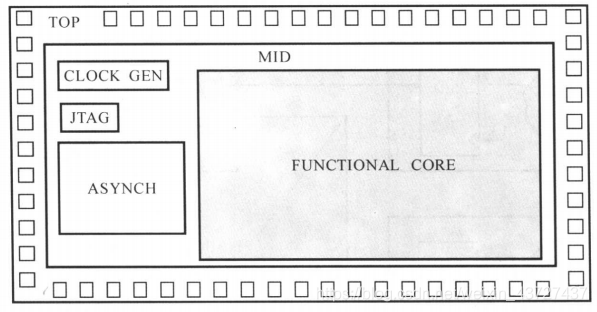

作划分时,要把核心逻辑(core logic),IO,Pads,时钟产生电路,异步电路和JTAG电路分开,放到不同的模块中。

顶层设计至少划分为3层的层次结构,

(1)顶层(Top-level)

(2)中间层(Mid-level)

(3)核心功能(Functional core)

异步电路的设计,其约束和综合与同步电路不同,所以也放在与核心功能不同的模块里。

为了使电路的综合结果最优化,综合的运行时间适中,需要对设计做出合适的划分。

DC两种方法修改划分:

(1)自动修改划分

综合过程中DC需透明地修改划分。在DC中使用命令:

compile -auto_ungroup area|delay

DC在综合时将自动取消小的模块划分。取消模块分区由变量

compile_auto_ungroup_delay_num_cells

compile_auto_ungroup_area_mum_cells

控制。

compile -ungroup_all

DC在综合时将自动取消所有的模块分区或层次结构。此时,设计将只有顶层一层的电路。

(2)手工修改划分

用户用命令指示所有的修改。

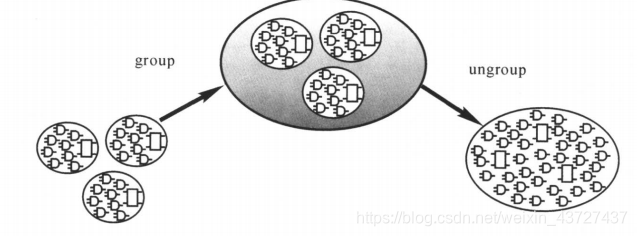

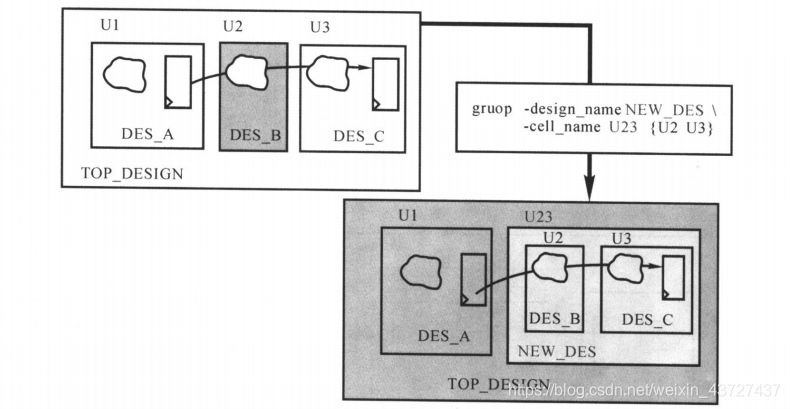

group命令产生新的层次模块。

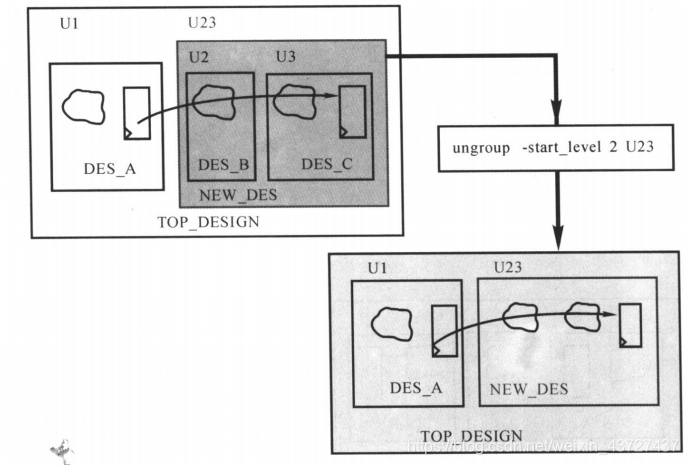

ungroup命令取消一个或者所有的模块分区。

如果要在当前设计中取消所有的层次机构,用命令:

ungroup -all -flatten

模块划分策略总结:

(1)不要通过层次边界分离组合电路

(2)把寄存器的输出作为划分边界

(3)模块的规模大小适中,运行时间合理

(4)把核心逻辑,Pads,时钟产生电路,异步电路和JTAG电路分开到不同的模块。

第四章 电路的设计目标和约束

设计规格中,一般包括电路的功能、设计的层次结构和模块划分、输入/输出端口及其驱动属性、电路的工作频率、电路的最大功耗、电路的最大面积、最小的测试覆盖率等等。

4.1 设计的时序约束

RTL代码中并不包括电路的时序(路径的延时)和电路面积(门数)。

电路的逻辑综合由三步组成:

综合 = 转化 + 逻辑优化 + 映射

先将RTL源代码转化为通用的的布尔等式------GTECH格式;然后按照设计的约束对电路进行逻辑综合和优化,使电路能满足设计的目标或约束;最后使用目标工艺库的逻辑单元映射成门级网表。综合的结果包括了电路的时序和面积。

4.1.1 同步(Synchronous)电路和异步(Asynchronous)电路

同步电路是指电路的所有时钟来自同一个时钟源。

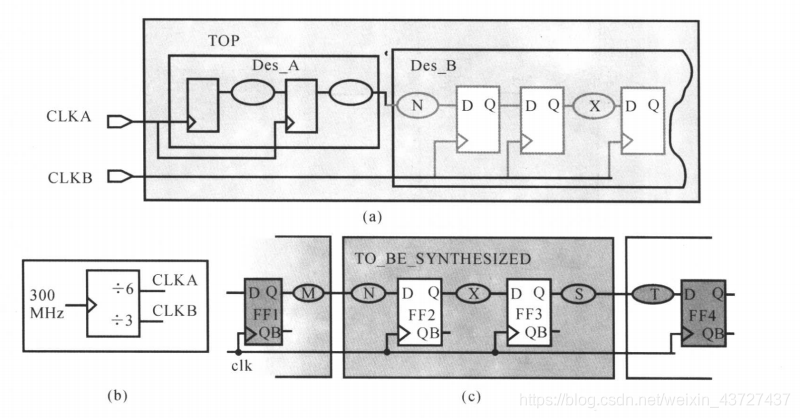

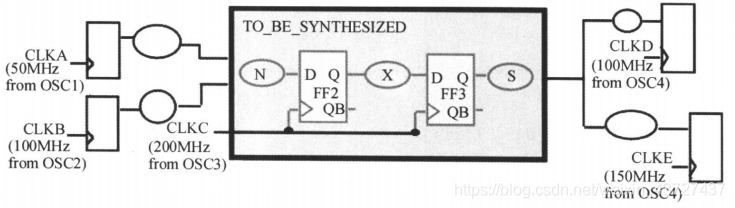

图(a)和图(c)都是同步电路。

异步电路是指电路的时钟来自不同的时钟域。

时钟CLKA和CLKB来自不同的振荡器OSC1和OSC2,它们之间没有固定的相位关系。

4.1.2 亚稳态(Metastability)

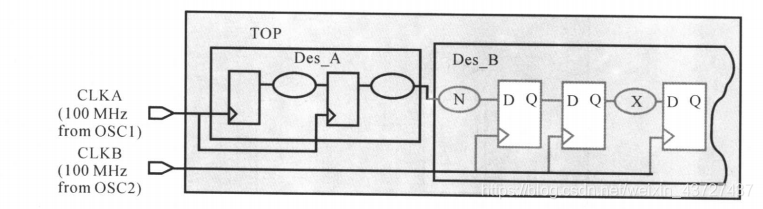

每个触发器都有其规定的setup(建立)和hold(保持)时间参数,该参数存放在由半导体厂商所提供的工艺库中。假设触发器由时钟的上升沿触发,在这个时间参数内,输入信号是不允许发生变化的。否则在信号的建立或保持时间中对其采样,获得的结果是不可预知的,有可能是“1”,“0”,“x”,“z”,即亚稳态。

4.1.3 单时钟同步设计的时序约束

对于同步电路,为了使电路能正常工作,即电路在我们规定的工作频率和工作环境中能功能正确的工作,需要对设计中的所有路径进行约束。

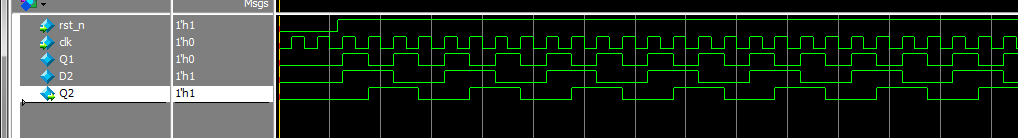

由于逻辑单元和连线是有延迟的,如果从寄存器FF1的clk引脚到寄存器FF2的D引脚的最大延迟小于时钟周期减去寄存器FF2的建立时间,即

Tco + Tlogic <= Tcycle - Tsetup

如果从寄存器FF1的clk引脚到寄存器FF2的D引脚的延迟大于时钟周期减去寄存器FF2的建立时间,而且其值小于时钟周期加上寄存器FF2的保持时间,这时,电路Q2的输出为不定值,电路不能正常工作。

一般情况下,如果寄存器和寄存器之间的组合逻辑延迟大于1clock cycle - Tsetup,电路的功能就会不正确。

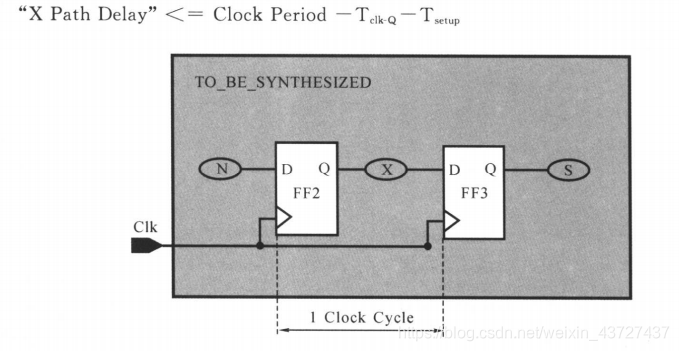

Tclk-Q是FF2的从引脚clk到引脚Q的延时,Tsetup是FF3的建立时间,这两个参数都由工艺库提供。

DC中用creat_clock命令来定义时钟

creat_clock -period 10 [get_port CLk]

定义时钟时(除虚拟时钟外),必须定义时钟周期和时钟源(端口或引脚),也可以加上一些可选项来定义时钟的占空因数,偏移和时钟名。

可以用report_clock命令来查看所定义的时钟及属性。

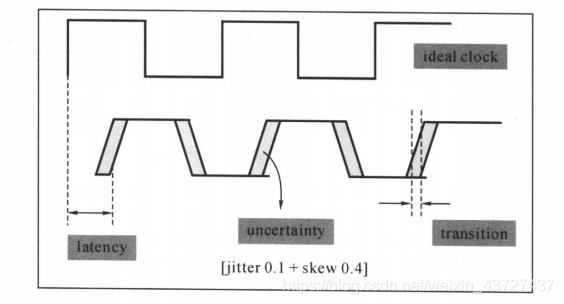

在默认情况下,逻辑综合时,即使一个时钟要驱动很多寄存器,DC也不会在时钟的连线上加时钟缓冲器(clock buffer),时钟输入端直接连接到所有寄存器的时钟引脚。在时钟连线上加上时钟缓冲器或作时钟树的综合一般由后端工具完成,后端工具根据整个设计的物理布局(placement)数据,进行时钟树的综合。加上时钟缓冲器后,使整个时钟树满足skew、latency和transition的目标。用下面的命令建立时钟模型

set_clock_uncertainty

set_clock_latency

set_clock_transition

偏差(uncertainty)表示时钟网络分支的延迟差异(相位差异)。这种延迟差异称为clock skew。

用set_clock_uncertainty命令来模拟时钟树

set_clock_uncertainty -setup TU [get_clocks CLK]

TU = clock skew + jitter。

假设时钟周期为10ns,时钟的偏差为0.5ns,用下面命令来定义时钟:

creat_clock -period 10 [get_ports CLK]

set_clock_uncertainty -setup 0.5 [get_clocks CLK]

在默认情况下,“set_clock_uncertainty”命令如果不加开关选项“-setup”或“-hold”,那么该命令给时钟赋予相同的建立时间和保持时间偏差值。

时钟网络的延迟(clock network latency)是时钟信号是从其定义的点(端口或引脚)到寄存器时钟引脚的传输时间。时钟源延迟(clock source latency),也称插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点的传输时间。

时钟网络延迟用下面的命令定义:

creat_clock -period 10 [get_ports CLK]

set_clock_latency -source 3 [get_clocks CLK]

set_clock_latency 1 [get_ports CLK]

在做布局布线之前,用set_clock_latency命令来模拟时钟网络的延迟。做完布局布线后,用set_propagated_clock来计算时钟网络的真实延迟。

版图前的时钟模型:

creat_clock -p 20 -n MCLK [get_ports CLK]

set_clock_uncertainty 0.5 MCLK

set_clock_transition 0.25 MCLK

set_clock_latency -source 4 MCLK

set_clcok_latency 2 MCLK

版图后的时钟模型

creat_clock -p 20 -n MCLK [get_ports CLK]

set_clock_uncertainty 0.1 MCLK

set_clock_latency -source 4 MCLK

set_propagated_clock MCLK

用set_clock_transition模拟时钟的转换(transition)时间。默认的上升转换时间为从电压的20%上升到80%的时间,下降的转换时间为从电压的80%下降至20%的时间。如果不加开关选项,那么该命令给时钟赋予相同的上升和下降转换时间。

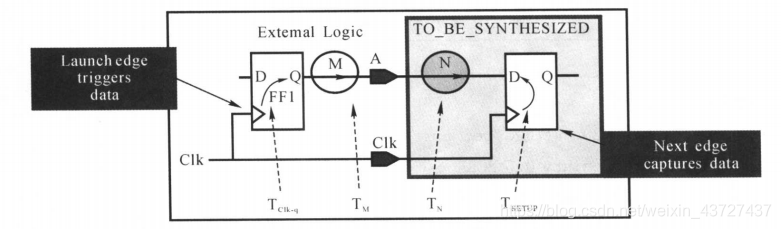

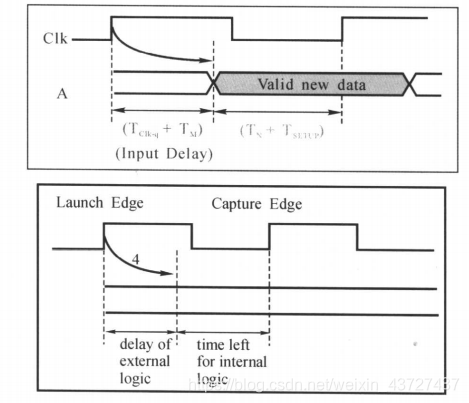

输入端口的时序约束:

在Clk的时钟上升沿,通过外部电路的寄存器FF1发送数据经过输入端口A传输到要综合的电路,在下一个时钟上升沿被内部寄存器FF2接收。

如果已知输入端口的外部电路的延迟(假设4ns),就可以很容易计算出留给综合电路输入端到寄存器N的最大延迟允许。

set_input_delay -max 4 -clock Clk [get_ports A]

对于时钟周期为10ns的电路,内部逻辑的最大延迟为10-4-Tsetup=6-Tsetup

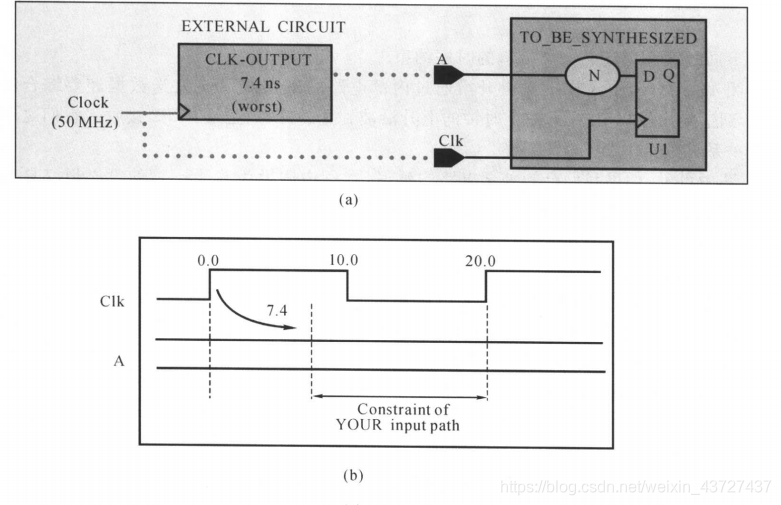

举例说明设置输入端口的约束。

输入端口的约束为:

creat_clock -period 20 [get_ports Clk]

set_input_delay -max 7.4 -clock Clk [get_ports A]

如果U1的建立时间为1ns,则N逻辑允许的最大延迟为:20-7.4-1=11.6ns

用下面命令对除时钟以外的所有输入端口设置约束

set_input_delay 3.5 -clock Clk -max \

[remoce_from_collection[all_inputs][get_ports Clk]]

remoce_from_collection[all_inputs][get_ports Clk]表示从所有的输入端口中除掉时钟Clk。如果要移掉多个时钟用

remoce_from_collection[all_inputs][get_ports "Clk1 Clk2"]

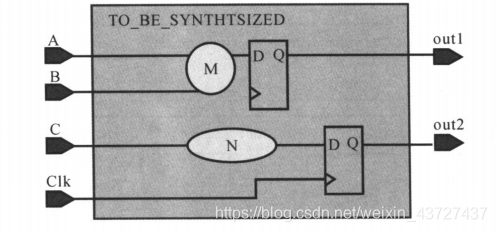

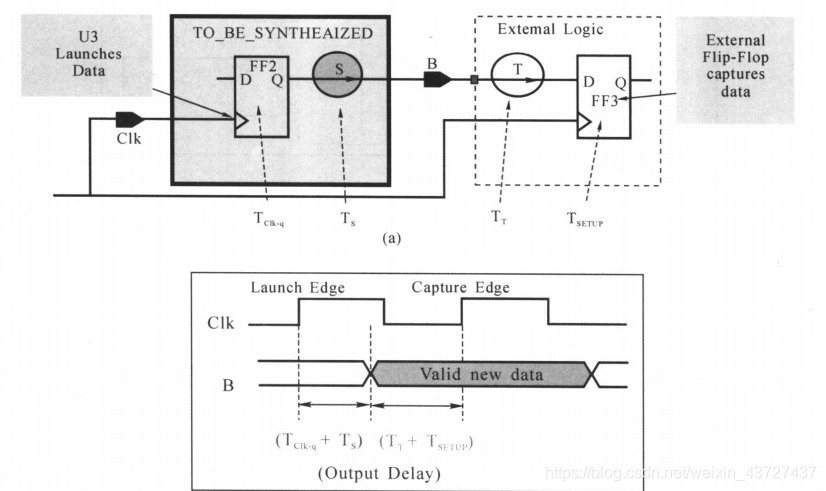

输出端口的时序约束

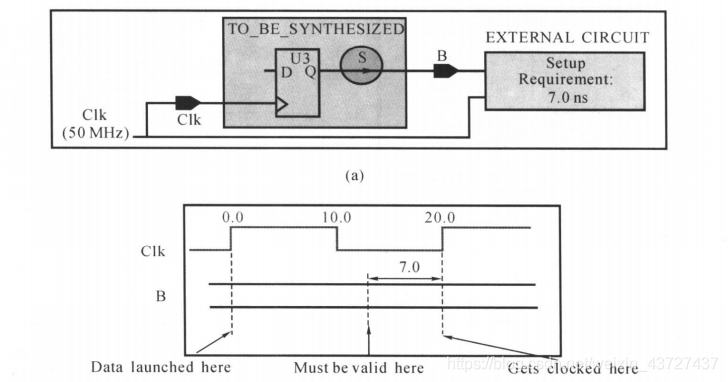

Clk时钟上升沿通过内部电路的寄存器FF2发送数据经要综合的电路电路S,到达输出端口B,在下一个时钟的上升沿被外部寄存器FF2接收。

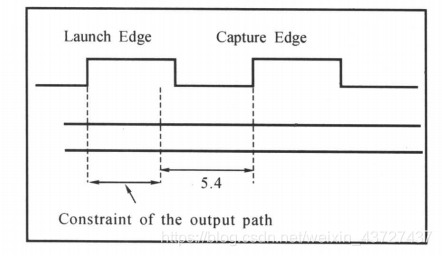

已知外部电路的延迟为5.4ns,DC中用set_output_delay命令约束输出路径的延迟。

set_output_delay -max 5.4 -clock Clk [get_ports B]

指定了外部逻辑用了多少时间,DC将会计算还有多少时间留给内部逻辑。

输出端约束为:

creat_clock -period 20 [get_ports Clk]

set_output_delay -max 7.0 -clock Clk [get_ports B]

如果U3的Tclk-Q=1.0ns,则s逻辑允许的最大延迟为20-7.0-1.0=12ns

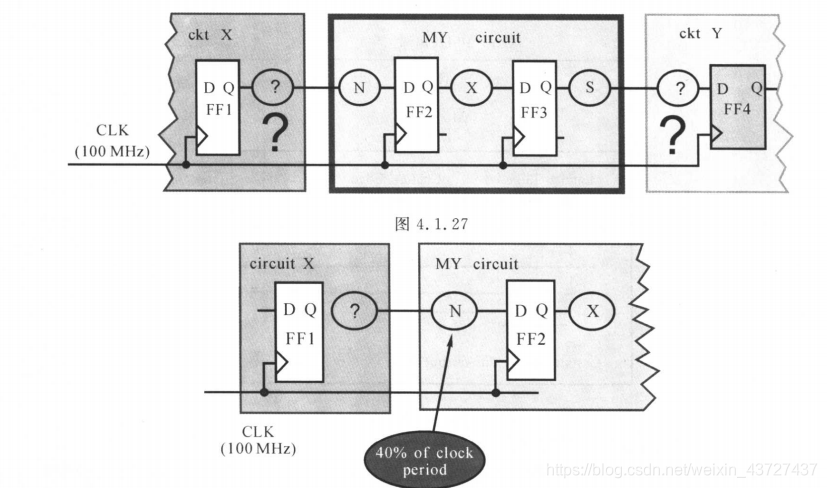

进行SOC设计时,由于电路比较大,需要对设计进行划分,在一个设计团队中,每个设计者负责一个或几个模块,但是并不知道每个模块的外部输入延迟和外部输出的建立要求,可以通过建立时间预算,为输入/输出端口设置时序约束。

DC要求不应在综合时还未加约束的路径,假设输入和输出的内部电路仅用了时钟周期的40%。所有模块都按照这种假定设置对输入/输出进行约束,将还有20%时钟周期的时间作为富余量(Margin),富余量包括寄存器FF1的延迟和FF2的建立时间。

富余量 = 20%T - Tclk-q - Tset-up

#Timing_budget.tcl

#A generic Time Budgeting script file

#for MY_BLOCK,X_BLOCK and Y_BLOCK

creat_clock -period 10 [get_ports CLK]

set_input_delay -max 6 -clock CLK [all_inputs]

remove_input_delay[get_ports CLK]

set_output_delay -max 6 -clock CLK[all_outputsx]

用check_timing命令在电路中寻找未加约束的路径。如设计中有未加约束的路径,该命令会报告警告信息,并把这些路径列出来。

在给设计添加约束的过程中,如果要删除已经加上的约束,可以用reset-design命令把它们删除。

4.1.4设计环境的约束

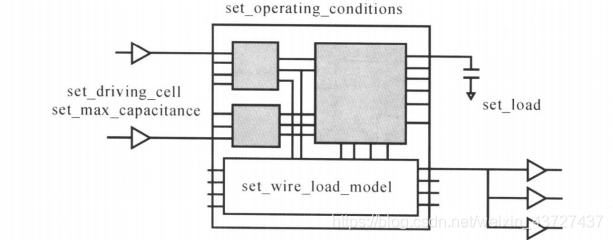

为了保证电路的每一条时序路径,特别是输入/输出路径延迟约束的精确性,还应该提供设计的环境属性。

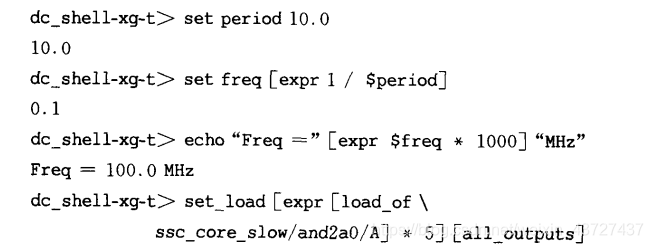

对于输出端,为了精确计算输出电路的时间,DC需要知道输出单元所驱动的总负载电容,用set_load命令说明端口(输入或输出)上的外部电容负载。

对于输入端为了精确计算输入电路的时间,需要知道到达输入端口的转换时间。在默认情况下,DC假设输入端口上的外部信号转换时间为0.用set_driving_cell命令在输入端加上一个驱动单元,DC将计算输入信号的实际转换时间,仿佛指定某一个库单元正在驱动它的(输入端)。

set_driving_cell -lib_cell FD1 -pin Q [get_ports IN1]

如果不加开关选项“-pin”,DC将使用所找到的第一只引脚。

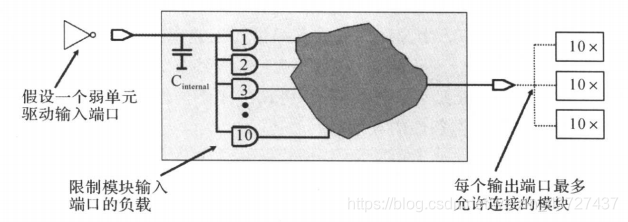

设计者可以通过负载预算(load budget)为输入/输出端口设置环境的约束。

产生负载预算可用下面的规则:

(1)为保守起见,假设输入端口由驱动能力弱的单元驱动

(2)限制每一个输入端口的输入电容(负载)

(3)估算输出端口的驱动模块数目

下面的脚本是下图负载预算的一个例子,原图的规格如下:

(1)模块输入端口驱动的负载不大于10个“AND2”门的输入引脚的负载

(2)模块输出端口最多允许连接3模块,如果某个输出端需要连接多余3个模块,需要在代码中复制该输出端口。

脚本load_budget.tcl如下:

current_design myblock

link

reset_design

source timing_dudget.tcl; #上节的脚本

set all_in_ex_clk[remove_from_collection\

[all_inputs][get_ports Clk]]

#Assum a weak driving buffer on the inputs

set_driving_cell -lib_cell invlal $all_in_ex_clk

#Limit the input load

set MAX_INPUT_LOAD[expr\

[load_of ssc_core_slow/and2a1/A] * 10]

set_max_capacitance $MAX_INPUT_LOAD $all_in_ex_clk

#MOdel the max possible load on the outputs,assuming

#outputs will only the tied to 3 subsequent blocks

set_load [expr $ MAX_INPUT_LOAD * 3][all_outputs]

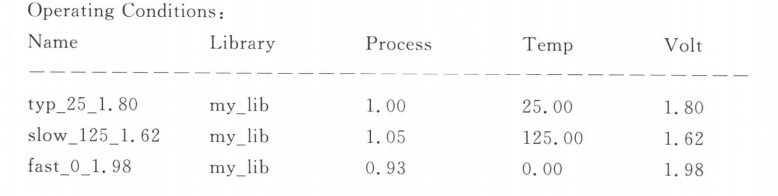

周围环境对电路的延迟有很大的影响。工艺库单元通常用“nominal”电压和温度来描述其特性。例如:

nom_process :1.0;

nom_temperature : 25.0;

nom_voltage : 1.8;

半导体厂商在其提供的工艺库中,一般会放入不同的工作条件,可以用set_operating_conditions命令把工作条件加入到设计上。综合时,将按工作条件作适当的比例调整。

report_lib libname

该命令把厂商提供的所有工作条件列出来,

设置工作条件可以用下面命令:

set_operating_condition -max "slow_125_1.62"

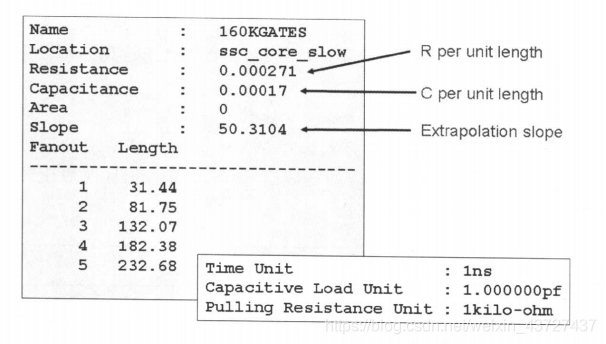

门单元的延迟一般用非线性延迟模型(non-linear delay model)算出。

DC遇到连线的扇出大于模型中列出的最大扇出值,它将使用外推斜率来计算连线的长度。

如果连线的扇出为7,而连线负载模型中最大扇出是5,连线的长度计算如下:

232.68 + 50.3104 * (7-5) = 333.3008

这条线的电容和电阻分别是:

333.308 * 0.00017 = 0.566pF

333.308 * 0.000271 = 0.0903kΩ

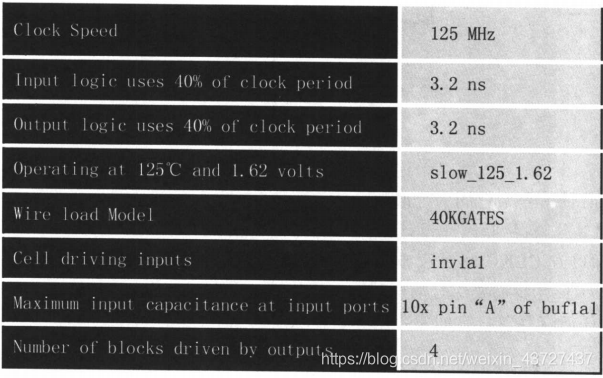

根据约束,写出设计的约束脚本,该脚本要适用于一个较大规模ASIC的每个子模块。

reset_design

set all_in_ex_clk [remove_from_collection \

[all_inputs][get_ports Clk]]

creat_clock -period 8 [get_ports Clk]

set_input_delay -max 4.8 -clock Clk $all_in_ex_clk

set_output_delay -max 4.8 -clock Clk [all_outputs]

set_operation_condition -max slow_125_1.62

set_wire_load_model -name 40KGATES

set_driving_cell -lib_cell invlal $all_in_ex_clk

set MAX_LOAD [expr[load_of ssc_core_slow/buflal/A]*10]

set_max_capacitance $AMX_LOAD $all_in_ex_clk

set_load [expr $ MAX_LOAD * 4][all_outputs]

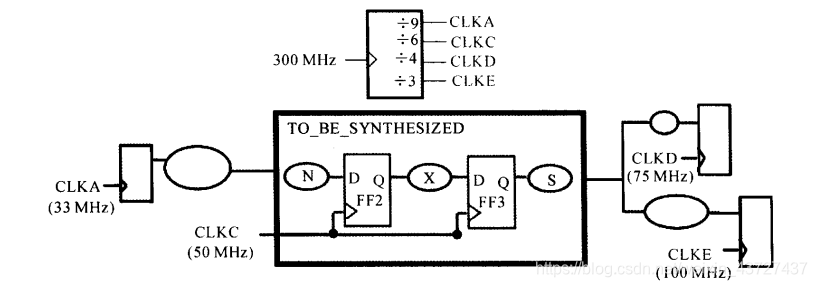

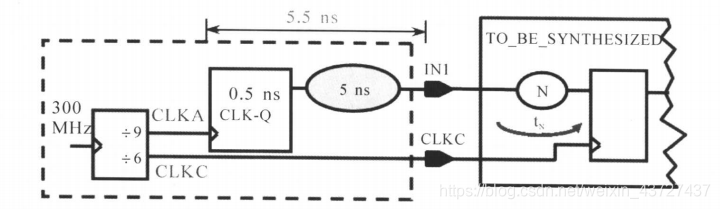

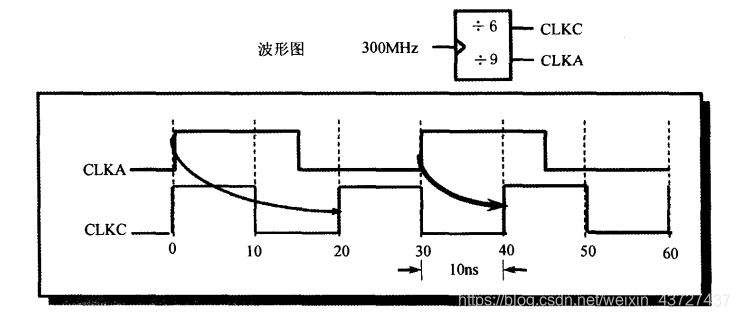

4.1.5 多时钟同步设计的时序约束

设计中所有的时钟由300Mhz的时钟源分频得到,因此是同步电路。CLKC在要综合的设计中有对应的输入端口,其定义与单时钟一样,即:

creat_clock -p 20 [get_ports CLKC]

由于CLKA、CLKD和CLKE在要综合的设计中没有对应的输入端口,因此需要使用虚拟(virtual)时钟。虚拟时钟在设计里并不驱动触发任何的寄存器,主要用于说明相对于时钟的IO端口延迟。DC根据这些约束,决定设计中最严格的约束。

creat_clock -name VCLK -period

虚拟时钟不驱动设计中的任何寄存器,设计中没有其对应的输入端口,所以定义中没有源端口或引脚。由于虚拟时钟没有对应的时钟端口,必须给它一个名字。虚拟时钟是DC的内存里已定义的时钟物体,不驱动设计中的任何寄存器,用作为输入/输出端口的设置延迟。

creat_clock -period 30 -name CLKA

creat_clock -period 20 [get_ports CLKC]

set_input_delay 5.5 -clock CLKA -max [get_ports IN1]

要综合电路的输入部分N必须满足

20-5.5-tsetup和10-5.5-tsetup这两个等式中最严格的情况,即

tN < 10-5.5-tsetup

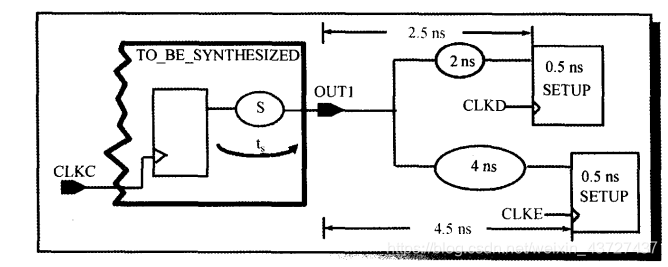

输出电路,用同样的方法定义虚拟时钟和施加约束。

creat_clcok -period [expr 1.0/75*1000] -name CLKD

creat_clock -period 10 -name CLKE

creat_clock -period 20 [get_ports CLKC]

set_output_delay -max 2.5 -clock CLKD [get_ports OUT1]

set_output_delay -max 4.5 -clock CLKE -add_delay [get_ports OUT1]

第二个输出延迟约束命令里面加了-add_delay意思是输出端口OUT1有两个约束。如果不加选项-add_delay,第二个输出延迟约束命令将会把第一个命令覆盖掉,这是输出端口OUT1只有一个约束。

4.1.6 异步设计的时序约束

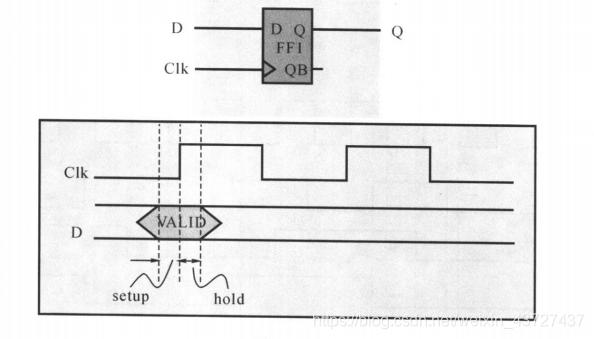

电路中,所有的时钟来自不同的时钟源。时钟之间是不同频率或者同频不同相的关系。进行异步设计时,设计者要注意会产生亚稳态导致某些寄存器的输出为不定态。

为了避免产生亚稳态问题,可以考虑在设计中使用双时钟、不易到亚稳态的触发器或使用异步FIFO等。对于穿越异步边界的任何路径,必须禁止对这些路径做时序综合。由于不同时钟源的时钟之间的相位关系是不确定的,一直在变。用set_false_path命令为跨时钟域的路径作约束。

current_design TOP

#Make sure register-register paths meet timing

creat_clock -period 10 [get_ports CLKA]

creat_clock -period 10 [get_ports CLKB]

#Dont optimize logic crossing clcok domains

set_false_paths -from [get_ports CLKA] -to [get_ports CLKB]

set_false_paths -from [get_ports CLKB] -to [get_ports CLKA]

compile -scan

如果设计中的所有时钟都是异步的,可以用下面命令为跨时钟域路径做约束。

set DESIGN_CLOCKS [all_clocks]

foreach_in_collection T_CLK $DESIGN_CLOCKS{

set_false_path -from $T_CLK -to \

[remove_from_collection[all_clocks] $ T_CLK]

}

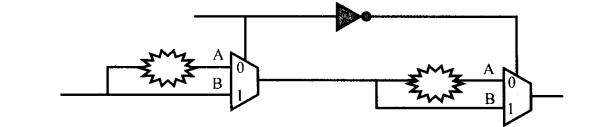

用set_false_path命令对路径做时序约束之后,DC做综合时,将终止对这些路径做时间的优化。该命令除了可以用于约束异步电路外,还可以用于约束逻辑上不存在的路径(logically false path),

图中前面的MUX的A1引脚和后面的MUX的A2引脚之间的逻辑通路并不存在。前面的MUX的B1引脚和后面的MUX的B2引脚之间的逻辑通路也不存在。

在DC中,伪路径“false path”称为时序例外(timing exception)。逻辑伪路径是一条物理上存在的路径。从点A1到点A2之间有一条物理上的连接路径,但是点A1输入信号并不通过这条路径传输到A2。

4.1.7 保持时间(Hold timing)

保持时间受下面因素影响:

(1)时钟树网络的时间偏差

(2)工作条件

(3)寄存器的保持参数

4.2 复杂时序约束

使用时钟的默认行为作为电路约束,即信号的变化要在一个时钟周期内完成,并达到稳定值,以满足寄存器的建立时间和保持时间的要求。有些设计的路径并不能或不需要在一个时钟周期内完成,只需要在规定的的数个时钟周期内完成信号的变化就可以了。作可测性设计时,为了提高测试的覆盖率,经常使用多路(multiplex,简称mux)传输电路控制时钟,使电路的时钟信号可以由输入端直接控制。

4.2.1 多时钟周期(Mult-Cycle)的时序约束

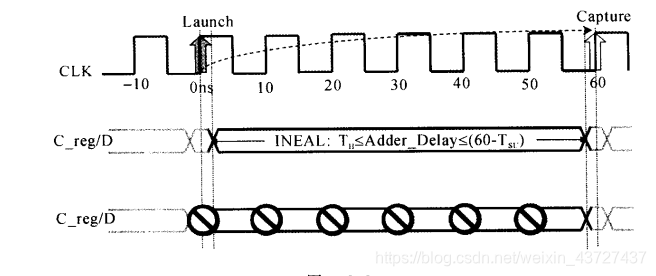

假设时钟clk的周期定义为10ns,加法器的延迟约为6个时钟周期。

creat_clock -period 10 [get_ports CLK]

set_multicycle_path 6 -setup -to [get_pins C_reg[*]/D]

默认的时序约是,在时钟触发沿,如果寄存器的数据输入引脚D信号变化,不满足建立时间和保持时间的要求,将产生亚稳态,寄存器的输出为不定态。

如上,加法器的最大延迟允许是60-Tsetup - Tuncertainty - Tclk-Q

默认的保持分析时间在建立分析时间的前一个时钟周期,在多时钟周期的设计里,DC将在50ns分析电路有无违反保持要求,即要求加法器的最小允许延迟是:

50 + Tholdtime + Tuncertainty。

要用DC综合出一条路径使其建立时间满足60ns的要求,并且同时满足保持时间50ns的要求实际上是没有必要的,这样会增加电路的复杂度。

在时间60ns的时刻,引起寄存器C-reg的D引脚信号变化的是时钟CLK在0ns时刻的触发沿。此刻(在0ns时),时钟CLK把寄存器A_reg和B_reg的D引脚信号采样到他们的输出端,再通过加法器把信号传输到寄存器C_reg的D引脚。由此可见,需要对保持时间作调整,应该在0ns时做保持时间的检查。

creat_clock -period 10 [get_ports CLK]

set_multicycle_path -setup 6 -to [get_pins C_reg[*]/D]

set_multicycle_path -hold 5 -to [get_pins C_reg[*]/D]

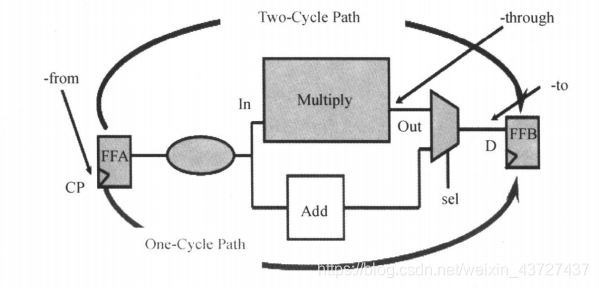

要求寄存器间的乘法运算单元为两个时钟周期,加法运算为默认的一个时钟周期。其约束为:

creat_clock -period 10 [get_ports clk]

set_multicycle_path -setup 2 -from FFA/CP \

-through Multiply/Out -to FFB/D

set_multicycle_path -hold 1 -from FFA/CP \

-through Multiply/Out -to FFB/D

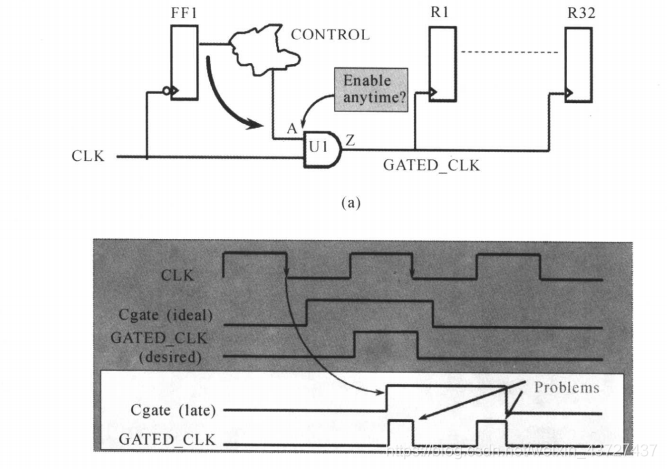

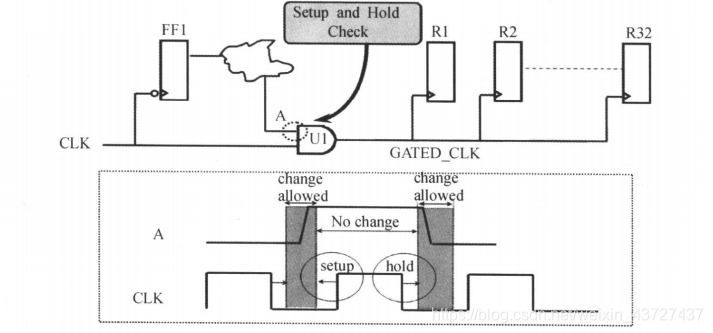

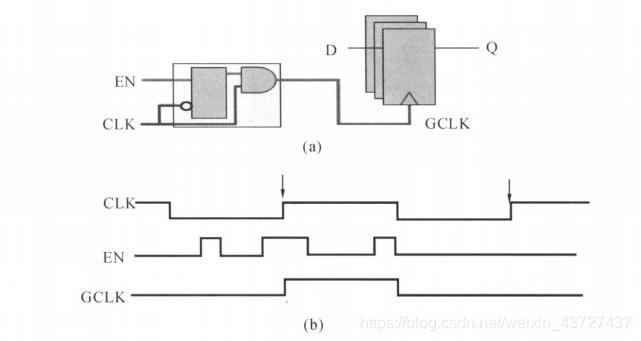

4.2.2 门控时钟的约束

门控时钟的使能信号约束为:

creat_clock -period 10 [get_ports CLK]

set_dont_touch_network [get_clocks CLK]

set_clock_gating_check -setup 0.5 -hold 0.5 [current_design]

DC能自动辨认门控时钟电路,综合时,DC将根据上述的约束在门控时钟电路中增加或删除逻辑以满足门控使能信号的建立和保持时间要求。

有两种门控时钟单元,一种是无锁存器门控时钟单元,一种是基于锁存器门控时钟单元。

基于锁存器的门控电路的输出没有毛刺,这种电路的结构行为表现的好像一个主从(master-slave)寄存器,它在时钟的上升沿捕获门控使能信号。

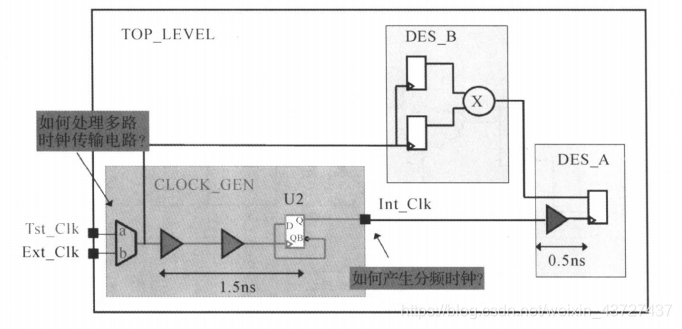

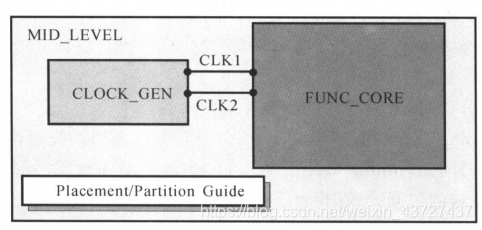

4.2.3 分频电路和多路传输多路传输电路的时钟约束

(1)顶层

(2)中间层

(3)核心功能

在中间层,把时钟电路和核心功能分开到不同的模块。

这样的好处是:

(1)所有的时钟产生电路在同一个模块中,对时钟逻辑可以有更好的控制并且易于分析结果

(2)简化了对其他模块的约束,它们的时钟约束只需要附加在输入端口上,加约束方便。

(3)增加了时钟的可控制性,易于提高测试覆盖率。

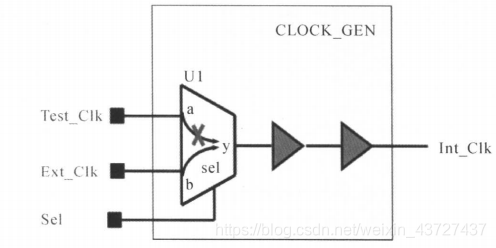

DC要用哪个时钟,DC会自己选择一个。可能会出现DC选择不同的时钟做建立和保持的分析。

creat_clock Ext_Clk -period 10

creat_clock Test_Clk -period 100

set_dont_touch_network [get_clocks Ext_Clk]

set_dont_touch_network [get_clocks Test_Clk]

#Allow DesignTime to use Ext_Clk for timing analysis

set_disable_timing CLOCK_GEN/U1 -from a -to y

set_disable_timing命令用起来灵活,该命令有多个选项。用该命令使设计中用到的库单元的时间弧无效。set_disable_timing命令使当前设计中的通过指定单元,引脚或端口的时间无效。

DC不能推导出分频时钟的波形。时钟信号可以通过任何的组合电路,但中止于寄存器。DC并不知道寄存器的输出端为时钟信号或非时钟信号。

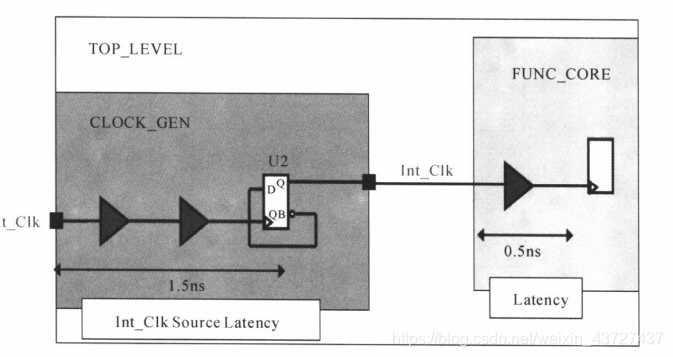

定义分频时钟的推荐方法

creat_clock -period 50 [get_ports Ext_Clk]

creat_generate_clock -name Int_Clk \

-source [get_pins CLOCK_GEN/U2/CP] -divide_by 2\

[get_pins CLOCK_GEN/U2/Q]

set_clock_latency -source 1.5 [get_clocks Int_Clk]

set_clock_latency 0.5 [get_clocks Int_Clk]

4.3 面积约束

用set_max_area命令为设计作面积约束。

current_design PRGRM_CNT_TOP

set_max_area 1000

面积的单位由工艺库定义,可以是:

(1)两输入与非门

(2)晶体管数目

(3)平方微米

如果不设置面积的约束,DC将做最小限度的面积优化。设置了面积的约束后,DC将在达到面积约束目标时退出面积优化。如果设置面积的约束为“0”,DC将为面积做优化直到再继续优化也不会有大的效果时退出优化。

设置面积目标用命令

set_max_area

设置时间目标用命令

creat_clock

set_input_delay

set_output_delay

creat_generated_clock

设置环境属性用命令

set_driving_cell

set_load

set_wire_load_model

set_operating_conditions

set_wire_load_mode

设置设计规则用命令

set_max_capacitance

报告命令有:

report_clock

report_port -verbose

report_design

清除约束用命令

reset_path

reset_design

1591

1591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?