状态机与序列检测器的实现

1. 什么是状态机

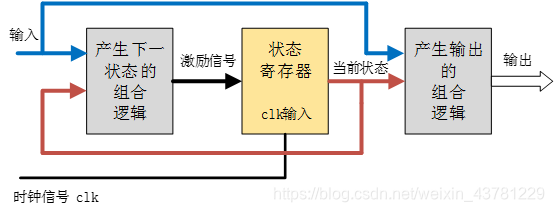

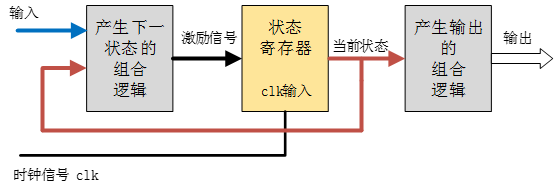

状态机(State Machine)/有限状态机(Finite State Machine,简称FSM)在有限个状态之间按一定规律转换的时序电路。在电路设计中主要用于逻辑控制。

2. 两种状态机类型

Mealy 状态机

Moore 状态机

两种状态机的区别在于:Moore的输出只取决于当前状态,而Mealy的输出不仅取决于当前的状态,还取决于外部的输入。

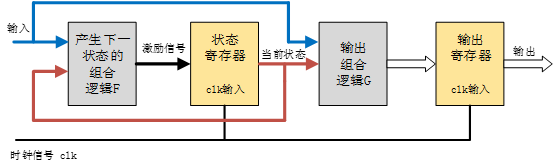

三段式可以在组合逻辑后再增加一级寄存器来实现时序逻辑输出:

1、可以有效地滤去组合逻辑输出的毛刺;

2、可以有效地进行时序计算与约束;

3、另外对于总线形式的输出信号来说,容易使总线数据对齐,从而减小总线数据间 的偏移,减小接收端数据采样出错的频率。

3. 典型序列检测器电路

`timescale 1ns/1ps

module sequential_detector(

input clk,

input rst_n,

input [3:0] data,

output reg response

);

parameter s1=4'b1000;

parameter s2=4'b0000;

parameter s3=4'b0010;

parameter s4=4'b0001;

parameter idle = 4'b1111;

reg [3:0] current_state;

reg [3:0] next_state;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

current_state <= idle;

else

current_state <= next_state;

end

always@(*)

begin

case(current_state)

idle: begin

if(data==4'b1000)

next_state <= s1;

else

next_state <= idle;

end

s1: begin

if(data == 4'b0000)

next_state <= s2;

else

next_state <= idle;

end

s2: begin

if(data == 4'b0010)

next_state <= s3;

else

next_state <= idle;

end

s4: begin

if(data == 4'b0001)

next_state <= s4;

else

next_state <= idle;

end

default:

next_state <= idle;

endcase

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

response <= 1'b0;

else if(current_state == s4)

response <= 1'b1;

else

response <= 1'b0;

end

endmodule

5537

5537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?