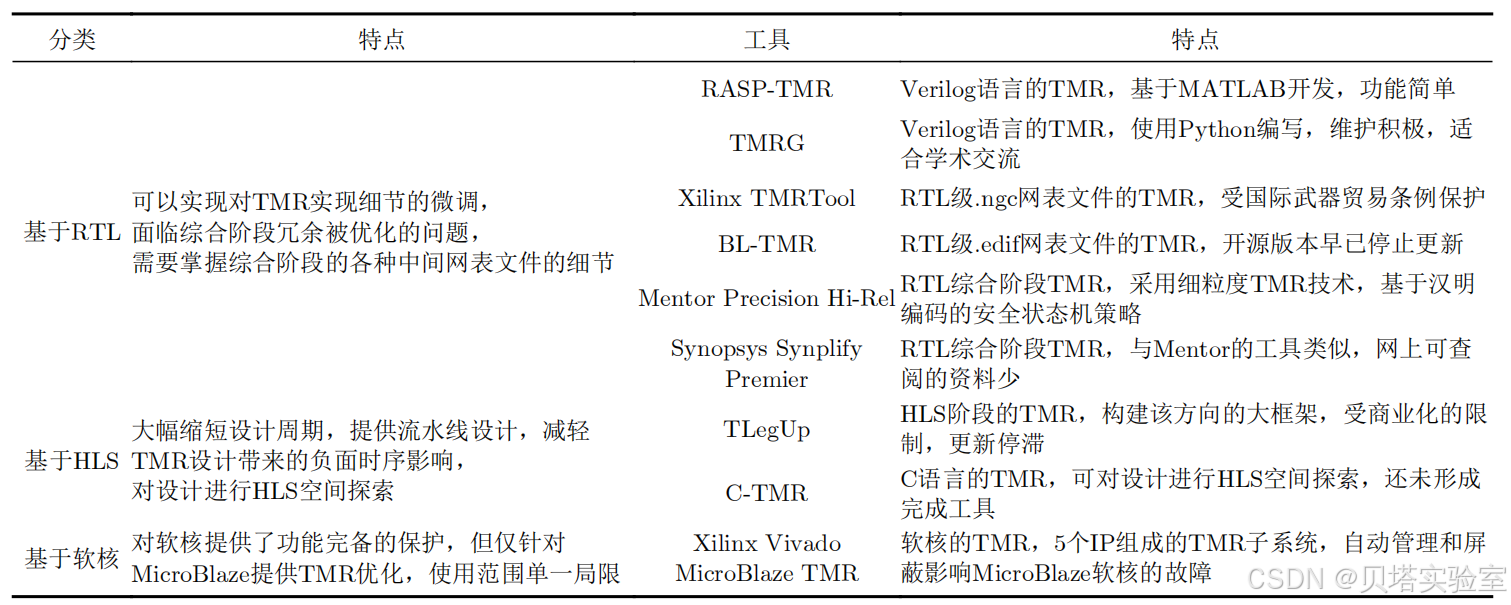

学术和商业领域有许多自动化的三模冗余TMR工具,本文介绍当前主流的基于寄存器传输级的三模冗余工具(Register-Transfer Level,RTL),基于重要软核资源的三模冗余工具,以及新兴的基于高层次综合的三模冗余工具(High Level Synthesis,HLS)。

1.基于RTL的工具

整体上分为两类,第一类是对Verilog语言进行TMR,主要有RASP-TMR和TMRG;第二类实在RTL综合的过程中对网表文件进行TMR,主要有Xilinx TMR-Tool,Mentor Precision Hi-Rel和Synopsys Synplify Premier。

1.1 RASP-TMR

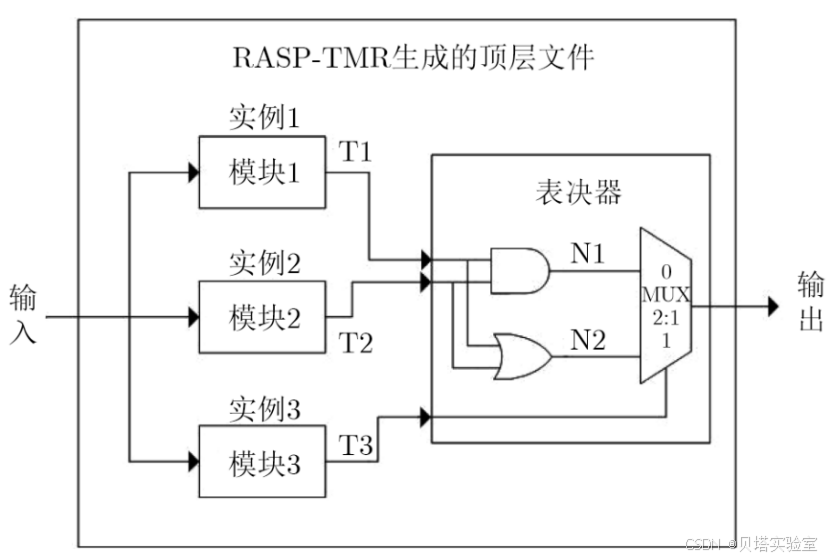

该工具以Verilog设计文件为输入,对其进行解析,获得输入输出参数,然后将设计模块3倍化。该工具还可以生成顶级模块文件,并在其中实例化生成的3个冗余模块,最后在实例化的冗余模块后添加多数表决器电路,生成三模冗余设计,如下图所示。此外,作者提出了一种新型、简单的多数表决逻辑实现,由1个与门、1个或门和1个2选1多路复用器组成,实现简单。

该工具仅由9个函数和254行MATLAB代码组成,是一款体量较小的学术工具,功能比较简陋,并且该作者已经转向研发另一款称为RASP-FIT的故障注入工具,该工具目前没有后续的维护计划。

1.2 CERN TMRG

TMRG(TMR Generator)是CERN用 Python语言开发的,用来协助创建不受SEU干扰的数字设计, 该工具以 Verilog语言为输入,输出Verilog语言的TMR设计。

TMRG工具集的组件主要包括TMRG、布局生成工具(PLAcement Generator, PLAG)、单粒子效应生成工具(Single Event Effect Generator,SEEG)和测试生成工具(Test Bench Generator,TBG)。TMRG相对于标准数字设计流程增加了一些新步骤,其主要思想是用户输入HDL语言,然后通过TMRG将其转换为三模冗余化后的HDL文件,此外 TMRG还会生成约束文件来防止综合工具删除冗余逻辑,而PLAG工具会生成约束文件来控制冗余模块分开布局,防止粒子影响多个存储相同冗余信息的单元。

此外,TMRG工具集还可以在验证过程中协助用户,单粒子效应生成工具提供了一种统一的机制来随机向门级瞬态模拟中引入SEU和SET,测试生成工具则可以通过将待测电路实例化为TMR版本和非TMR版本来进行测试。

TMRG的功能相对比较完善,在提供了生成TMR设计的 Verilog代码基础上,还针对TMR的冗余逻辑容易在综合过程中被优化的问题提出了解决措施。此外,该项目仍在积极维护,是学术TMR工具中为数不多的尚在积极更新的平台,非常适合学术研究与交流。

1.3 Xilinx TMRTool

Xilinx TMRTool,简称XTMR, 是 Xilinx与 Sandia National Laboratories合作开发,专为满足可重构FPGA的TMR设计的特殊需求而设计的,提供了许多有用的功能, 例如从Virtex和Virtex-II FPGA电路中移除半锁存器,以及同步表决器插入,可在任何Virtex至Virtex-5设计上提供全SEU和SET免疫。XTMR以ISE生成的.ngo和.ngc文件为输入, 输出.edif文件的TMR设计。

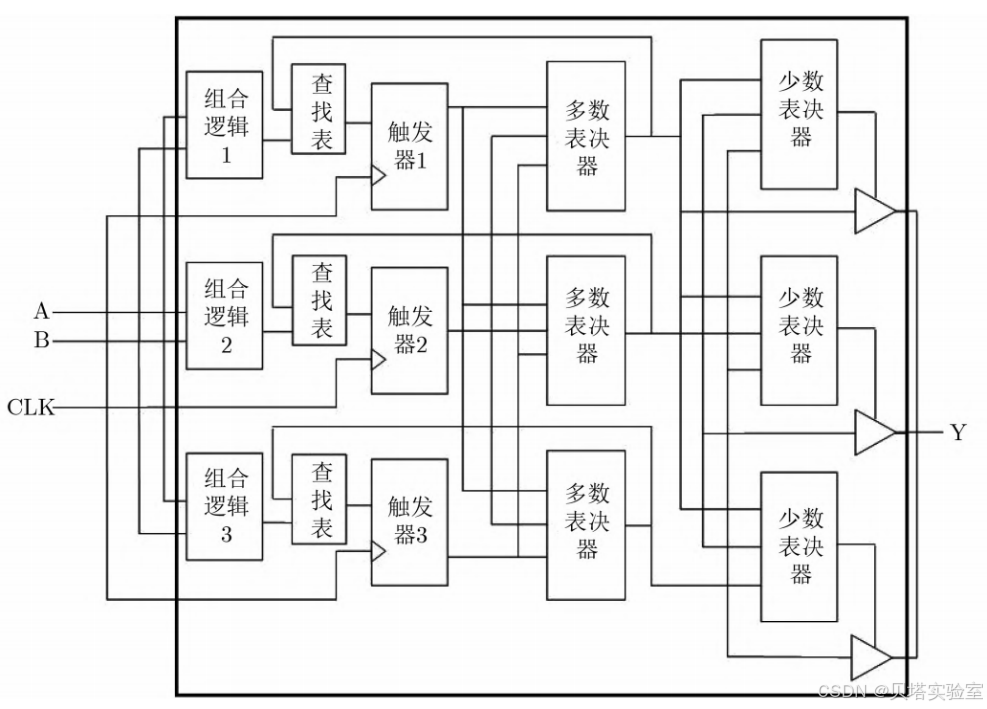

XTMR通过对输入和组合逻辑、反馈逻辑、输出逻辑3个基本设计模块的3倍复制,来解决传统TMR的诸多问题, 如下图所示。

在输入和组合逻辑部分,XTMR将输入和组合逻辑都复制为3份,由于还未添加表决逻辑,每个冗余路径都是独立的,此外,XTMR设计是在印刷电路板(Printed Circuit Board, PCB)上, 所以外部的输入输出不受辐射的影响,而在内部的输入、输出和表决器都是3份冗余,所以可以消除这些资源的单点故障,保证设计免受电路翻转和单粒子瞬态的干扰。

在反馈逻辑部分,XTMR使用了前文所说的触发器状态同步技术,通过在反馈路径上插入表决器来确保各冗余模块之间的状态同步。对于传统的TMR,冗余状态机要保持同步必须重置才能从SEU中完全恢复。Xilinx TMR通过在所有反馈路径上插入表决器来解决此问题,从而使冗余状态机之间可以持续同步,无需进行复位即可从SEU中恢复。

在输出阶段,输出的选择是整个XTMR的关键,TMR电路会有3个冗余逻辑路径,那么必须有一种方式将3个逻辑路径返回到单一路径,这就需要输出的选择来完成。XTMR将3个冗余模块的输出通过三态缓冲器和少数表决器在3个引脚分别输出,最后在PCB上“线或”为一个信号。如果某个冗余路径上发生了翻转,对应的少数表决器就会判定本冗余路径的信号为少数值,并通过控制三态缓冲器使输出端口变为高阻状态,从而控制该输出端口上无输出信号,另外两个冗余路径的正确信号将继续输出。

由于TMRTool受到国际武器贸易条例(The International Traffic in Arms Regulations, ITAR)的控制,对外实行严格的封锁和禁运,仅能通过其用户手册来管中窥豹,很难获取其软件的实际使用信息以及相关效果评测研究。TMRTool仅支持与ISE搭配使用, 而且FPGA器件也仅支持至 Virtex-5, 不支持 Xilinx Virtex-6以后的新型FPGA器件。

1.4 BYU-LANL TMR

BYU-LANL TMR是由BYU在洛斯阿拉莫斯国家实验室(Los Alamos National Laboratory,LANL)的支持下开发的,用于对EDIF格式的设计应用三模冗余。

该工具首先将EDIF格式的文件解析成网表数据结构,通过搜索强连通图来分析确定网表数据结构中的反馈结构,并分类出反馈结构的输入输出,BLTMR基于这些信息来选择电路中需要三模化的结构,并根据用户约束文件来选择尽可能多的反馈、反馈输入和反馈输出逻辑,之后就可以根据需要三模化的电路组件来确定表决器的插入位置,完成TMR设计并以EDIF格式输出。

BLTMR的开源版本已经不再提供维护,仅支持Virtex和Virtex4的设备, 主要与Xilinx ISE配合使用,而由美国国家科学基金会高性能可重构计算中心(NSF Center for High-Performance Reconfigurable Computing, CHREC)支持更新的版本支持 Xilinx-7系列和Vivado,并加入了新的表决器放置算法和IP的集成。

1.5 Mentor Precision Hi-Rel

Precision Hi-Rel是 Mentor Graphics在NASA指导下开发的一种基于综合的辐射效应缓解工具, 该工具以Verilog为输入, 输出.edif文件或.v网表文件的TMR设计。

Precision使用了前文所说的细粒度TMR技术, 提供了3种不同程度的TMR: LMTR,DTMR,GTMR,还为有限状态机(Finite State Machine,FSM)提供了基于汉明编码的安全状态机策略

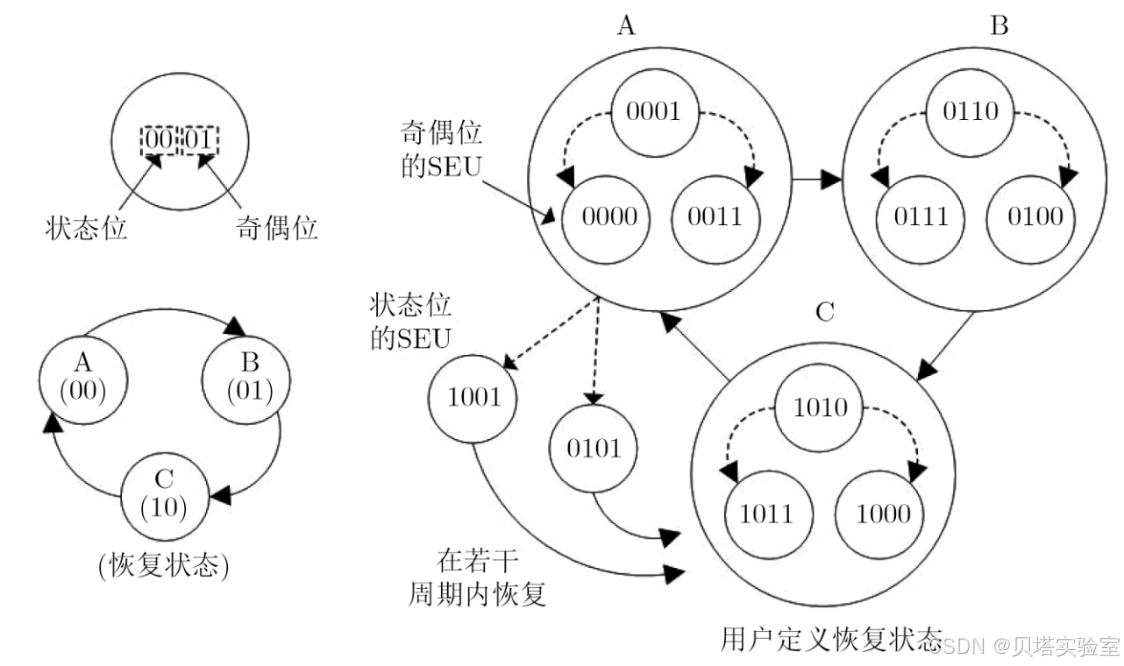

SEU的检测与恢复FSM使用汉明距离2的编码方式,如下图所示,使用奇偶校验的汉明编码将初始状态00,01,10编码为由状态位与校验位组成的0001,0110,1010,当状态位发生翻转时,FSM就会进入恢复状态,恢复到指定的初始状态;而当校验位发生翻转时,能够进行容错,尽可能减少FSM的中断。在FSM发生SEU的情况下,FSM操作中断,进入恢复状态,需要消耗若干个时钟周期,对于一些时序敏感的应用场景不够友好。

而容错FSM使用汉明距离3的编码方式,可以在不中断电路正常功能的情况下吸收SEU。

设计人员可以依据使用的可编程结构、预期的单粒子效应类型以及应用程序的关键程度来决定使用不同类型的TMR防止软错误。同时,它支持器件类型非常多,如 Microsemi的SmartFusion2,TRG4以及Xilinx的7系列和UltraScale系列。

1.6 Synopsys Synplify

Synplify Premier为F PGA设计人员提供了多种方式来实现错误检测和缓解的电路,包括TMR、双备份比较检错、带TMR的纠错码存储器、安全状态机、汉明-3编码的容错状态机。

Synplify提供了LTMR, DTMR与BTMR 3种类型,来保护和纠正SRAM逻辑、寄存器、IP、配置位、存储器和I/O。此外, Synplify支持的器件也非常多, Altera, Microsemi和 Xilinx的大部分器件均有支持。可搜索到的 Synplify相关信息比较少, 不过 Synopsys与 Mentor均是综合工具厂商,其工具相似性比较高,无论是细粒度的TMR,还是基于汉明编码的安全FSM,所以可以认为Synplify接近于 Precision的实现细节。

得益于FPGA编程技术的发展现状,当前的TMR工具主要集中在RTL级实现。无论是基于RTL描述的工具,还是基于RTL综合的工具,在RTL级的实现拥有对TMR实现细节进行各种微调的优势, 对于Verilog语言进行直接TMR,整体的实现难度相对降低,但是会面临综合阶段冗余被优化的问题,而在综合阶段插入TMR,可以避免冗余逻辑被综合的问题,需要对综合阶段的各种中间网表文件以及FPGA的底层架构非常了解。

2660

2660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?