开关电源自举电容设计

问题背景

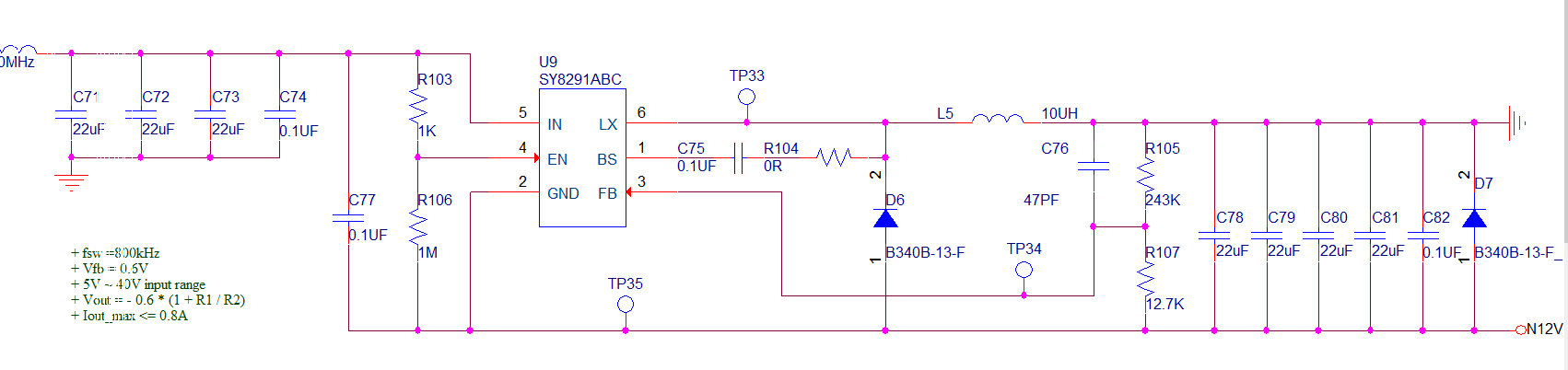

出现问题的电路是一个使用异步buck芯片做负电源的电路,电路图如图。

设计的输入电压为12V,输出电压为-12V。

出现的问题表现为,同一批次的6pcs板子,只有1PCS是不正常的,表现为输出电压只有-1.56V。

问题的debug过程

电路只是输出电压偏低,首先怀疑负载过重。断电测量输出端对地的阻抗,发现相比正常的单板偏小。断开后端负载后重新测量,发现阻抗仍然偏小,可见问题是出在开关电源这一侧。

测量开关节点波形,发现开关节点的高电压达不到输入的电源轨道附近,低电压接近输出电压。判断问题是出在了IC内部的nmos上,应该是nmos未完全导通导致的问题。此时经验丰富的工程师应该已经能够定位问题出现的位置了,而我就要在大量测试之后才能找到问题的所在,最后的问题出在了自举电容上。

然而当时的我并没有意识到问题的严重性,因为这个电路是在原有的buck电路上改过来的,项目已经量产,没有出现过自举电容的问题。因此我首先怀疑到了IC故障。从好的板子上吹下一颗IC后贴装到不良的板子上,故障波形依旧。将不良的IC贴到ok的板子上,芯片功能没有问题。因此问题不是出在IC上。

既然IC没有问题,那么就只能是分立的无源器件有问题了,分别测量开关节点对地和对输入电源的阻抗。发现故障单板的开关节点阻抗偏低。然后就开始拆除和开关节点有关的器件。在拆除了点入R104之后,开关节点的阻抗特性较为接近了。但是测量R104的阻值,并没有出现异常,因此继续拆除C75,测量后发现,C75的电容值相比于设计值0.1uF显著偏低。更换C75后,电路正常,问题解决。

失效分析

PCB是我们的代工厂贴装的,此前多次合作过,应该不是混料问题。因此电路的问题高概率出现在电路设计上。重新检查设计,发现电容选择的耐压值为25v.根据自举电容的工作原理,当下管导通时,此时电容充电,假设上管导通的时间足够长,此时的电容两端压降为Vin-Vout。在新的设计中,电容两端的压差达到了 24V!!! 当原有设计的电源为buck电源时,此时自举电容上承受的最大压差为Vin-Gnd,压差约为12V。而我们选用的电容为耐压25V 0.1uF的电容,因此导致了新设计的翻车。

总结

故障识别

自举电容击穿的典型表现为上mos无法可靠的被推开。因此导致开关节点的波形高电平无法达到电源轨道附近。

故障排除

如果开关节点的阻抗明显异常,但是又确认芯片无问题的话,如果满足故障识别的条件,可以考虑先更换自举电容。

故障避险

在自举电容的设计时。有以下几个点需要考量。

- 自举电容的容值,在原厂的参考设计中这个值一般是直接给出的。但是实际的设计中还是应当根据工况具体选择,比如当buck电路的压差比较小的时候,此时的占空比非常高,下管导通的时间较短,因此可能会出现下关周期中给自举电容充入的电荷量无法维持上管导通时的能量的问题。此时可以增加电容量或者增加充电回路解决问题,但是电容量也不能太大,因为芯片内部给自举电容充电电路的电流时有限的,因此过大的电容有可能无法达到所需要的自举电压。所以要选择合适的自举电容。

- 自举电容的耐压。翻车案例就在本blog中。就不多阐述了。除了耐压值以外,还应当注意由于DC偏置带来的电容损耗,防止出现容值不足的情况。

- 自举电容的ESR,一般来说我们都希望自举电容的ESR小一点,因为此时可以更快的推开MOS,减少损耗,但是当我们的电源设计出现EMI问题的时候,增加自举电容的ESR(人为串联电阻),可以使得开关的导通过程边缓。以此来削减开关电源的开关节点产生的高频分量,达到优化EMI的目的。

667

667

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?