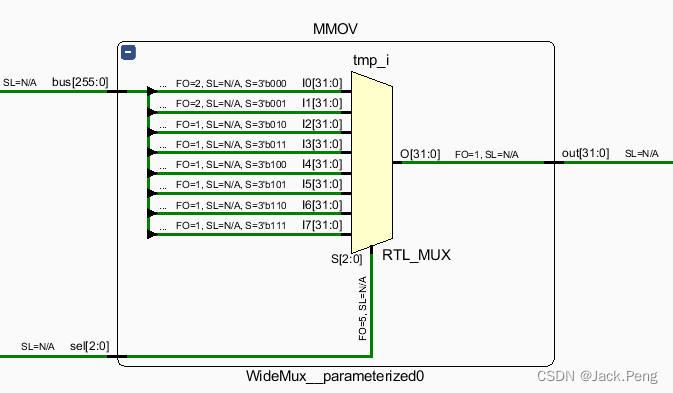

多位选多位的数据选择器在进行FPGA开发时经常会用到,在编写Verilog时往往可以直接通过case,if,generate等语句方便地实现数据选择器,但是这种写法很大程度脱离了基本的逻辑表达式,很多具体的逻辑实现都由编译器替我们完成了,在查看网表只能看到这样的结果:

而不清楚里面具体的逻辑,于是在理解数据选择器的时候我们往往会有这样的问题:数据选择器的底层是怎样的?如何一步步地拓展成我们看到的样子的?下面我们就从一个基础的例子来了解一下数据选择器。

1 一比特4选1数据选择器

数据选择器包含包含三部分:输入信号,选择信号和输出信号。

首先考虑一个简单的一位多输入选择器(四选一输入D[3:0],片选信号X[1:0],输出Y)

它的逻辑表达式可以写作:,对应如下表格:

| Input D | Sel X | Output Y |

|---|---|---|

| D[3:0] | 00 | D[0] |

| D[3:0] | 01 | D[1] |

| D[3:0] | 10 | D[2] |

| D[3:0] | 11 | D[3] |

从表达式中可以看出来,当确定某一个X的组合时,如X=00,那么不满足该条件的其它项都为0,最后Y的结果为,仅与

有关。这样就用与门和或门这样的基本逻辑单元实现了四选一的数据选择器。

按照上面的思想编写Verilog代码如下:

`timescale 1ns / 1ps

//

// Company: SUSTech

// Engineer: Daojie.PENG@qq.com

//

// Create Date: 2022/09/19 22:40:18

// Design Name: Multiplexer(1bit) 4 to 1

// Module Name: MUX

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies: None

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module MUX(

D,

X,

Y);

input wire [3:0] D;

input wire [1:0] X;

output wire Y;

assign Y = (~X[1]&~X[0]&D[0]) | (~X[1]&X[0]&D[1]) | (X[1]&~X[0]&D[2]) | (X[1]&X[0]&D[3]);

endmodule

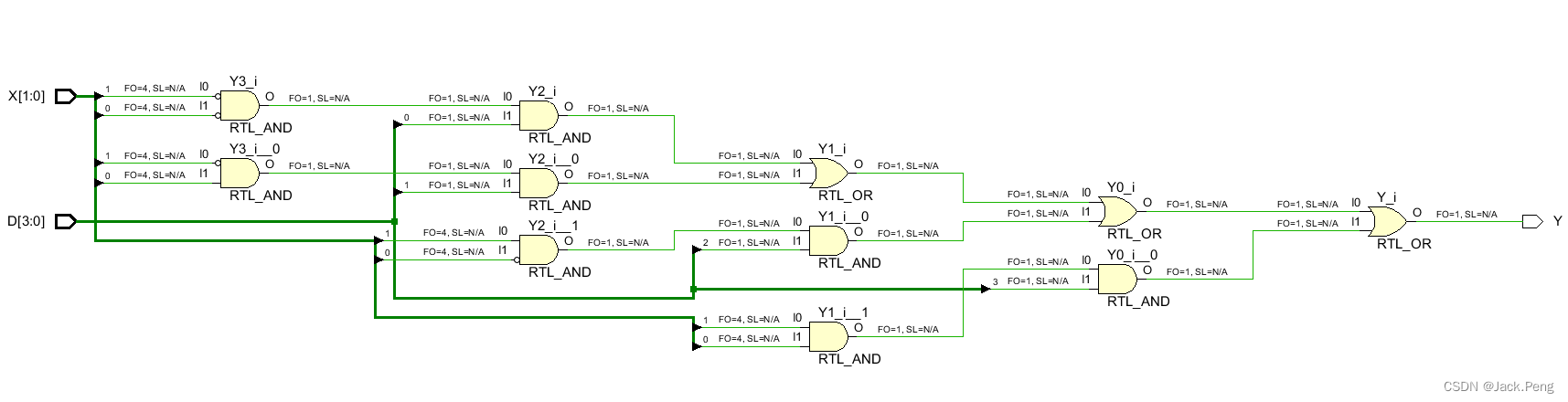

生成的逻辑图如下:

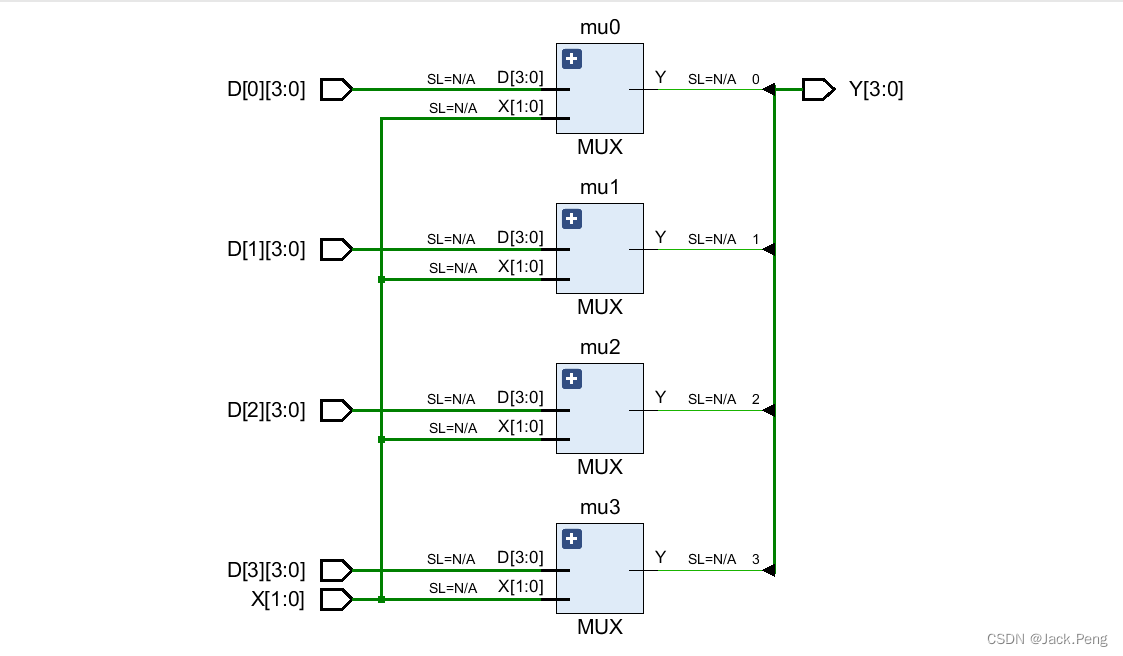

2 多比特4选1数据选择器

对于多位对多位的输入比如输入为4bits*4,输出为4bits,只需要将上1比特4选一复用器按位拓展。

`timescale 1ns / 1ps

//

// Company: SUSTech

// Engineer: Daojie.PENG@qq.com

//

// Create Date: 2022/09/19 22:40:18

// Design Name: Multiplexer 4 to 1

// Module Name: MUX

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies: None

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module MUX4(

D,

X,

Y);

input wire [3:0] D [3:0];

input wire [1:0] X;

output wire [3:0] Y;

MUX mu0 (D[0],X,Y[0]); // 将1比特4选一的MUX实例化

MUX mu1 (D[1],X,Y[1]);

MUX mu2 (D[2],X,Y[2]);

MUX mu3 (D[3],X,Y[3]);

endmodule

// 1bit 4 to 1 multiplixer

module MUX(

D,

X,

Y);

input wire [3:0] D;

input wire [1:0] X;

output wire Y;

assign Y = (~X[1]&~X[0]&D[0]) | (~X[1]&X[0]&D[1]) | (X[1]&~X[0]&D[2]) | (X[1]&X[0]&D[3]);

endmodule

生成的网表如下 :

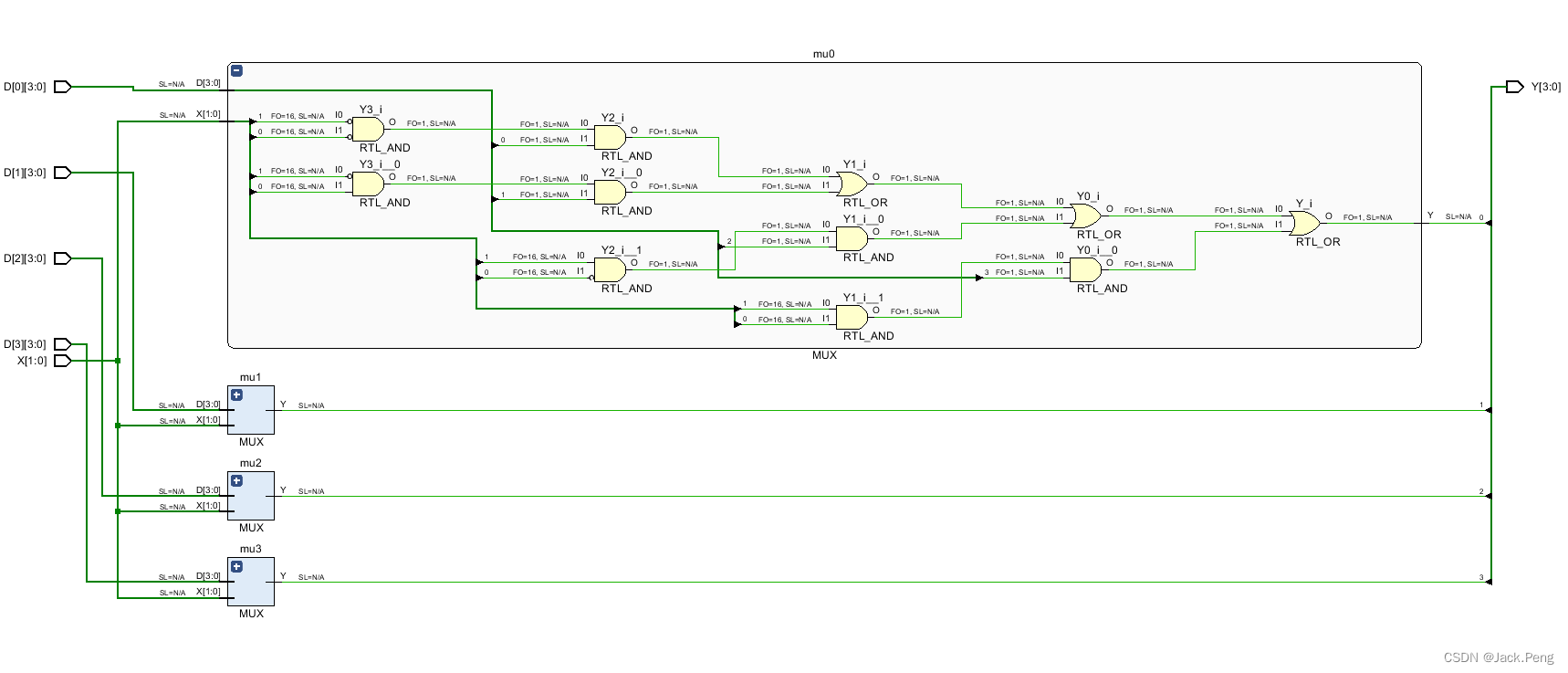

内部逻辑细节,就是上面的单个4选1数据选择器的逻辑:

3 多比特多选多数据选择器

对于8选一,只需要将X的位数变为3位X[2:0],对于16选一,只需要将X的位数变为4位X[3:0],以此类推。

注:使用工具为Vivado2019

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?